APPLIED PHYSICS LETTERS VOLUME 82, NUMBER 4 27 JANUARY 2003

## Investigation of buffer traps in an AlGaN/GaN/Si high electron mobility transistor by backgating current deep level transient spectroscopy

M. Marso,<sup>a)</sup> M. Wolter, P. Javorka, P. Kordoš, and H. Lüth *Institute of Thin Films and Interfaces, Research Centre Juelich, D-52425 Juelich, Germany*

(Received 19 August 2002; accepted 3 December 2002)

The influence of a substrate voltage on the dc characteristics of an AlGaN/GaN high electron mobility transistor (HEMT) on silicon (111) substrate is profited to investigate traps that are located between the substrate and the two-dimensional electron gas channel. The transient of the drain current after applying a negative substrate voltage is evaluated in the temperature range from 30 to  $100\,^{\circ}$ C. With this method, known as backgating current deep level transient spectroscopy, majority carrier traps with activation energy of 200 meV as well as minority carrier traps at 370 meV are identified. The experiments are performed on completed HEMTs, allowing the investigation of the influence of device fabrication technology. © 2003 American Institute of Physics.

[DOI: 10.1063/1.1540239]

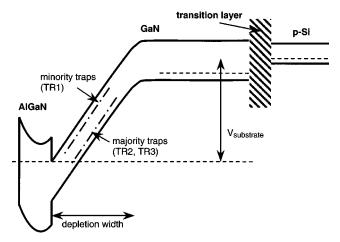

Sapphire and SiC are commonly used as substrate materials for GaN based electronic and optoelectronic devices. Recently Si has been found as a useful alternative because of its low cost and good thermal conductivity. AlGaN/GaN/Si high electron mobility transistors (HEMT) with unity current gain frequencies comparable to those known for devices using sapphire or SiC substrates have been reported. In contrast to sapphire the electrical conductivity of the Si substrate allows the application of a voltage at the backside of the devices through a substrate contact. This provides the control of backgating to study the physical properties of the device and of the material (defect states, trapping effects). The backgating effect is well known from GaAs based metalsemiconductor field effect transistors (MESFET) and HEMTs.<sup>2</sup> The junction between substrate and buffer creates a depletion layer that controls the transistor channel in the form of a gate from the backside. This effect can be used to control the drain current by a substrate voltage. The backgating effect is also one origin of the very high optoelectronic responsivity of MESFETs and HEMTs.<sup>3</sup> For HEMTs the backgating depletion region and therefore the influence of the substrate voltage is limited to the region below the twodimensional electron gas (2DEG). Therefore, all related effects have their origin in the bulk without contribution of surface effects. Uren et al.4 have profited from the influence of a backgating voltage on the pinch-off voltage of an AlGaN/GaN HEMT on a conducting SiC substrate to investigate the electrically active centers in the GaN buffer. They have shown that the backgating depletion layer of the AlGaN/GaN HEMTs extends from the 2DEG into the buffer and is not located between substrate and buffer. Therefore, the observed effects do not originate from traps in the lower, more defective part of the buffer, but they are due to traps near the heterointerface. In this work we use backgating current deep level transient spectroscopy (DLTS)<sup>5</sup> to investigate the activation energy of traps in the buffer of an AlGaN/GaN HEMT on a Si substrate. Figure 1 shows the schematic band

diagram of the substrate biased device.

The device was fabricated using an AlGaN/GaN heterostructure grown by metalorganic vapor phase epitaxy on a 2 in. (111)-oriented highly resistive p-type Si substrate. First a transition layer was grown, followed by an 800 nm GaN buffer layer, 6-nm-thick undoped AlGaN spacer, 20 nm Sidoped carrier supply layer, and 6 nm undoped AlGaN. The AlN mole fraction was 23%. The room temperature sheet carrier density and mobility were  $6 \times 10^{12} \, \mathrm{cm}^{-2}$  and  $700 \, \mathrm{cm}^2/\mathrm{V} \, \mathrm{s}$ , respectively. Device processing consisted of conventional HEMT fabrication steps. Details of growth and device fabrication are given elsewhere. The investigated transistor has a channel width of 50  $\mu$ m, a source-to-drain spacing of 3  $\mu$ m, and a gate length of 650 nm. No passivation layer was applied.

The dc and time domain measurements were performed by an HP 4145B semiconductor parameter analyzer. The substrate voltage was supplied by a Keithley 4200 SourceMeter. The temperature was controlled in the range of 30–100 °C by a peltier heater. Prior to each measurement the device was illuminated during two minutes by a microscope lamp to prevent any influence of the preceeding measurement. The

$FIG.\ 1.$  Schematic band diagram and trap location of the substrate-biased HEMT.

a)Electronic mail: m.marso@fz-juelich.de

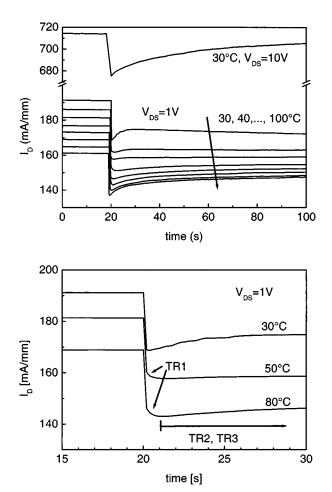

FIG. 2. Transient behavior of the drain current.  $V_{\text{substrate}} = 0 \text{ V}$  for t < 20 s and  $V_{\text{substrate}} = -10 \text{ V}$  for  $t \ge 20 \text{ s}$ . Upper part: behavior during the first 100 s. Lower part: expanded plot of the first seconds after applying the substrate voltage. The regions of trap contributions TR1, TR2, and TR3 are indicated.

actual measurements were performed in the dark. The substrate voltage of -10 V was applied 20 s after applying the bias voltages to allow relaxation of the start-up effects. The upper curve of Fig. 2 shows the transient behavior of the drain current for  $V_{\rm DS}$ =10 V, and  $V_{\rm GS}$ =0 V. The current decreases in accordance to the increase of the backgating depletion layer when the negative substrate voltage is applied. The large overshoot is caused by the thermal release of trapped majority carriers in the depletion layer. Detrapping of minority carriers would lead to a current transient in the opposite direction with a further reduction of the drain current. The dissipated dc power at these bias conditions leads to a large self-heating of the device above 100 °C.8 Therefore, the temperature dependent measurements were performed in the linear transistor regime at  $V_{DS} = 1 \text{ V}$  and  $V_{GS}$ = 0 V. The relaxation behavior of the drain current was measured from 30 to 100 °C in 2 °C steps in a 200 s time interval. Figure 2 shows the time domain behavior for selected temperatures.

The temperature dependent relaxation of the drain current was investigated by the backgating current deep level transient spectroscopy method.<sup>5</sup> Instead of using a boxcar technique the current transient was fitted by a sum of exponential functions in order to improve the accuracy of the time constant determination. The current characteristics below 50 °C show a fast decrease during the first seconds after

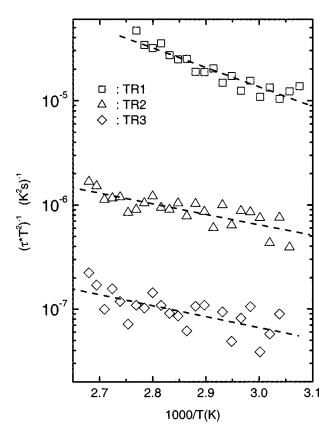

FIG. 3. Arrhenius plot of the fitted time constants.

applying the substrate voltage, followed by an increase and a subsequent very slow decrease. Although this behavior indicates the existence of several trap contributions with different properties and activation energies, the behavior below 50 °C was found too complex for a clear fitting. Therefore, the origin of the slowly decreasing current contribution could not be evaluated. Only the measurements between 50 to 100 °C were considered to determine the trap properties. A first, very fast decrease of the current was identified, shown on the expanded plot of Fig. 2. We attribute it to a minority carrier trap (TR1 in Figs. 2 and 3). The subsequent relaxation to a larger current is due to majority carrier traps. This relaxation can be fitted by two exponential functions with different time constants (TR2 and TR3 in Figs. 2 and 3). An Arrhenius plot of the fitted time constants (Fig. 3) yields an activation energy of (370+/-30) meV for the minority carrier trap. The activation energies of the majority carrier traps are (200+/-30) and (210+/-50) meV, respectively. The identical activation energies of both majority carrier traps suggest that they are coupled, or more probably that only one single trap contribution is observed with a nonexponential (e.g., a stretched exponential) relaxation behavior. A stretched exponential behavior of trapping transients in AlGaN/GaN HEMTs is known from literature. It is attributed to a decrease of the driving force for detrapping, when detrapping proceeds. The measurement method implicates that no surface effects are observed, but that these traps are located in the region below the 2DEG channel (Fig. 1). The determined activation energies correspond to published values by conventional DLTS measurements [e.g., Ref. 10 and 11 for the (370+/-30) and (210+/-50) meV traps, respectively.

Downloaded 21 Dec 2006 to 134.94.122.39. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

In conclusion backgating current DLTS is used to investigate traps in the buffer of an AlGaN/GaN HEMT on Si substrate. A substrate voltage controls the backgating depletion layer that influences the drain current. The evaluation of the temperature dependent current relaxation identifies minority carrier and majority carrier trap contributions with 370 and 200 meV activation energy, respectively. The evaluation is performed on completed devices, allowing the investigation of the influence of different fabrication steps.

- <sup>3</sup> M. A. Romero, M. A. G. Martinez, and P. A. Herczfeld, IEEE Trans. Microwave Theory Tech. 44, 2279 (1996).

- <sup>4</sup>M. J. Uren, D. Herbert, T. Martin, B. T. Hughes, J. Birbeck, R. Balmer, A. J. Pidduck, and S. K. Jones, Phys. Status Solidi A 188, 195 (2001).

- <sup>5</sup>M. Ogawa, IEICE Trans. **E70**, 847 (1987).

- <sup>6</sup>P. Javorka, A. Alam, M. Wolter, A. Fox, M. Marso, M. Heuken, H. Lüth, and P. Kordoš, IEEE Electron Device Lett. 23, 4 (2002).

- <sup>7</sup>D. V. Lang, J. Appl. Phys. **45**, 3023 (1974).

- <sup>8</sup>J. Kuzmík, P. Javorka, A. Alam, M. Marso, M. Heuken, and P. Kordoš, IEEE Trans. Electron Devices 49, 1492 (2002).

- <sup>9</sup>R. Vetury, N. Q. Zhang, S. Keller, and U. Mishra, IEEE Trans. Electron Devices 48, 560 (2001).

- <sup>10</sup>Z.-Q. Fang, D. C. Look, P. Visconti, D.-F. Wang, C.-Z. Lu, F. Yun, H. Morkoç, S. S. Park, and K. Y. Lee, Appl. Phys. Lett. **78**, 2178 (2001).

- <sup>11</sup> H. K. Cho, C.-H. Hong, E.-K. Suh, and H. J. Lee, J. Appl. Phys. 41, 197 (2002).

<sup>&</sup>lt;sup>1</sup> P. Javorka, A. Alam, A. Fox, M. Marso, M. Heuken, and P. Kordoš, Electron. Lett. 38, 288 (2002).

<sup>&</sup>lt;sup>2</sup>H. Goronkin, M. S. Birrittella, W. C. Seelbach, and R. L. Vaitkus, IEEE Trans. Electron Devices ED-29, 845 (1982).