## Gadolinium scandate thin films as an alternative gate dielectric prepared by electron beam evaporation

M. Wagner, <sup>a)</sup> T. Heeg, J. Schubert, St. Lenk, and S. Mantl Institute of Thin Films and Interfaces and Center of Nanoelectronic Systems for Information Technology, Research Centre Juelich, D-52425 Juelich, Germany

C. Zhao, M. Caymax, and S. De Gendt IMEC, Kapeldreef 75, B-3001, Leuven, Belgium

(Received 22 December 2005; accepted 10 March 2006; published online 25 April 2006)

Gadolinium scandate thin films deposited on silicon substrates using electron beam evaporation were investigated. Measurements with Rutherford backscattering spectrometry, high temperature x-ray diffraction, x-ray reflectometry, transmission electron microscopy, and atomic force microscopy were performed. A stoichiometric transfer of material from the source to the substrate in high vacuum could be demonstrated. Homogeneous, amorphous, and smooth films (root mean square surface roughness <1 Å) stable up to  $1000 \,^{\circ}$ C were obtained. Electrical characterization of capacitor stacks revealed a dielectric constant of  $\approx 23$ , C-V curves with small hysteresises and low leakage current densities (770  $\mu$ A/cm<sup>2</sup> for a capacitance equivalent thickness of 1.5 nm). © 2006 American Institute of Physics. [DOI: 10.1063/1.2198103]

In order to satisfy the demand for higher performance and integration density in microelectronics, the scaling of metal oxide semiconductor field effect transistors (MOS-FETs) becomes more and more aggressive. In this respect silicon dioxide as the gate dielectric will have to be replaced because of intolerable high leakage current densities. Therefore, one of the major challenges for the microelectronics industry is the integration of high- $\kappa$  dielectrics into the complementary metal oxide semiconductor (CMOS) process in the near future. A promising class of materials for high- $\kappa$ applications are the rare earth scandates (REScO<sub>3</sub>—RE denoting a rare earth element) because of their favorable material properties. For single crystals of these ternary oxides Schlom and Haeni<sup>2</sup> found dielectric constants of 20–35 depending on the lattice direction. Lim et al.3 determined an optical band gap larger than 5 eV and Afanas'ev et al.4 confirmed this value for thin amorphous films grown by pulsed laser deposition (PLD). In addition, these authors found conduction and valence band offsets to silicon of 2-2.5 eV. The thermal stability of LaScO<sub>3</sub>, GdScO<sub>3</sub>, and DyScO<sub>3</sub> thin films deposited with off-axial pulsed laser deposition was investigated by Zhao et al. They showed that in contact with silicon the amorphous phase of LaScO<sub>3</sub> is stable up to 800 °C while DyScO<sub>3</sub> and GdScO<sub>3</sub> thin films remain amorphous up to 1000 °C. However, films deposited with PLD are inhomogeneous and exhibit many particulates on the surface that have chipped off from the target. Other techniques such as chemical vapor deposition normally use an oxidizing atmosphere at elevated temperatures to stoichiometrically deposit binary or ternary oxides. This leads to the growth of a thermal SiO<sub>2</sub> on silicon substrates preventing the realization of low equivalent oxide thicknesses. Because of little differences in the morphological and electrical properties of DyScO<sub>3</sub> and GdScO<sub>3</sub> and their superior thermal stability,<sup>2–5</sup> GdScO<sub>3</sub> has been exemplarily selected to investigate the deposition of thin films with an unconventional deposition technique for such a material.

In this work, gadolinium scandate thin films were deposited by means of electron beam evaporation in a conventional deposition chamber (Leybold Univex 450). Typically, with this technique complex stoichiometries cannot be transferred from the evaporation source to the substrate because of different vapor pressures of the elements involved. But since the vapor pressures of Gd and Sc are similar, a deposition of stoichiometric  $GdScO_3$  thin films from a stoichiometric evaporation source made from a mixture of the metal oxides could be demonstrated. The depositions were performed at a pressure of  $1-5\times10^{-6}$  mbar without addition of any process gas. These high vacuum conditions offer the possibility to deposit the scandate directly on silicon preventing the formation of a low- $\kappa$  SiO<sub>x</sub> interface layer.

As substrates,  $2 \times 2$  cm<sup>2</sup> large pieces of (100) p-type silicon were used. Prior to the deposition either a 2 nm thick silicon dioxide was thermally grown on the surface or the substrate was HF dipped to remove the native oxide. The sample holder in the chamber is equipped with a resistive heater and the depositions were done at a substrate temperature of 600 °C. After deposition, the films were investigated with respect to their morphology and chemical composition by means of Rutherford backscattering spectrometry (RBS), x-ray reflectometry (XRR), high temperature x-ray diffraction (HT-XRD), transmission electron microscopy (TEM), and atomic force microscopy (AFM).

For electrical characterization of the films, capacitor stacks were manufactured. Metal top contacts (Au, Pd, or Pt) with a thickness of 70 nm and an area of  $65 \times 65 \ \mu m^2$  were deposited by thermal or electron beam evaporation through a shadow mask. The Ohmic backside contact was realized by deposition of 200 nm Al followed by a forming gas anneal (10% H<sub>2</sub>/90% N<sub>2</sub>) to improve the backside contact and the high- $\kappa$  dielectric-to-silicon interface. The capacitor stacks were investigated using an impedance analyzer (HP 4192A) for *C-V* measurements and a semiconductor parameter analyzer (HP 4155B) for leakage current measurements.

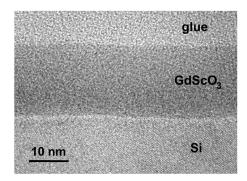

Figure 1 shows a cross sectional TEM micrograph of a 17 nm thick GdScO<sub>3</sub> film after deposition on a HF last sur-

a)Electronic mail: m.wagner@fz-juelich.de

FIG. 1. TEM micrograph of a 17 nm thick GdScO<sub>3</sub> film deposited at 600 °C on a HF last surface of (100) Si.

face of (100) silicon at a substrate temperature of 600 °C. The film exhibits a homogeneous and amorphous structure. Obviously, the growth of an interfacial SiO<sub>x</sub> layer was suppressed in the high vacuum conditions. The scandate layer directly adjoins the crystalline silicon substrate.

To investigate the stoichiometry of the films the coverage of the substrate with Gd and Sc atoms was determined using RBS. The stoichiometry of the films is close to the nominal composition of GdScO<sub>3</sub>. The ratio Gd:Sc lies between 1:0.9 and 1:1.3. Within this range no influences of the stoichiometry on the morphology or electrical properties of the films could be observed. In addition, the RBS measurements confirm a growth rate linear with deposition time. Comparisons of RBS (coverage with atoms) and XRR data (physical thickness) show that the densitiy of the films deposited at 600 °C is about 83% of the single crystalline density.

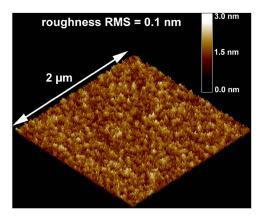

The films are free from particulates and homogeneous. A film thickness variation of <5% over a 2 in. wafer was achieved. In addition, the surface is very smooth as indicated by AFM measurements (Fig. 2). A peak-to-valley roughness of about 1 nm and a rms roughness of below 0.1 nm for film thicknesses up to 20 nm within a scan size of  $2\times 2 \mu m^2$ were revealed.

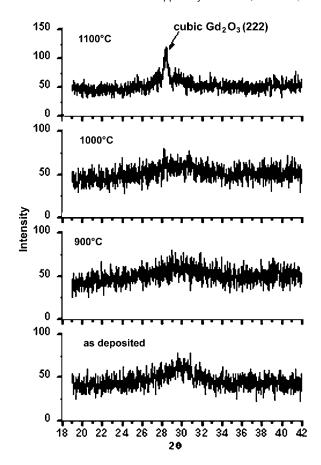

To investigate the thermal stability of the scandate films, in situ high temperature XRD measurements were performed in high vacuum ambient. The sample is held at each temperature step for 30 min to perform the measurement. Figure 3 shows data of a 20 nm thick GdScO<sub>3</sub> film deposited at 600 °C on a HF last surface. Obviously the layer remains amorphous up to 1000 °C. At 1100 °C, a phase segregation

FIG. 2. (Color online) AFM scan of an ≈20 nm thick GdScO<sub>3</sub> film; the scan size is  $2 \times 2 \mu m^2$ , the peak-to-valley value 1 nm, and the RMS roughness

FIG. 3. High temperature XRD measurement of an ≈20 nm thick GdScO<sub>3</sub> film deposited on a HF last surface of (100) Si at 600 °C.

occurs and Gd<sub>2</sub>O<sub>3</sub> crystallites start to form. This crystallization onset temperature is much higher than that for hafnium dioxide<sup>6</sup> films. In addition, a decomposition of the films as reported for hafnium dioxide films in literature could not be observed. Compared to the films prepared by PLD,<sup>5</sup> the e-beam films show a similar crystallization onset temperature. The crystalline phase, however, is cubic Gd<sub>2</sub>O<sub>3</sub>, instead of hexagonal Gd<sub>2</sub>O<sub>3</sub>, as found in the PLD films.<sup>4</sup> The high crystallization onset temperature is within the thermal budget required for CMOS processing.

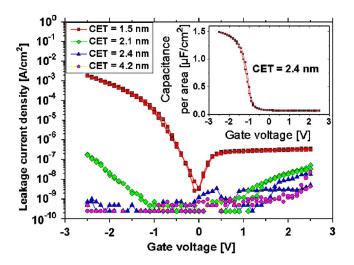

For the electrical characterization, samples with different film thicknesses (3.8, 6, 10, and 19.5 nm) were prepared and Pt top contacts were deposited to form capacitor stacks. On all samples, C-V and I-V measurements were performed. Figure 4 displays *I-V* data for this set of samples. The curves were recorded with a hold time of 30 s for each measuring point to wait for all relaxation processes to be decayed before the measurement. The capacitance equivalent thickness (CET) of the capacitors calculated from the capacitance in accumulation at -2 V ranges from 1.5 to 2.4 nm. In contrast to the equivalent oxide thickness (EOT) the CET does not take quantum effects into account and usually is significantly larger for thin films. The thinnest film with a CET of 1.5 nm exhibits a low leakage current density of  $7.7 \times 10^{-4}$  A/cm<sup>2</sup> at a voltage of -2 V which is about five orders of magnitude lower than conventional SiO<sub>2</sub>.

The leakage current of the thicker films is close to the detection limit. The inset in Fig. 4 shows a typical C-V curve of the film with a CET of 2.4 nm. It was recorded at 100 kHz with a hold time of 3 s for each measuring point. It is free of humps and irregularities and exhibits a small hysteresis indi-

Downloaded 21 Dec 2006 to 134.94.122.39. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

FIG. 4. (Color online) *I-V* curves of GdScO<sub>3</sub> films with different thicknesses; the inset shows a *C-V* curve for the sample with a CET of 2.4 nm recorded at 100 kHz.

cating a low number of interface states. With the two-frequency method an interface trap charge density of the films close to  $5 \times 10^{11}$  cm<sup>-2</sup> was determined.

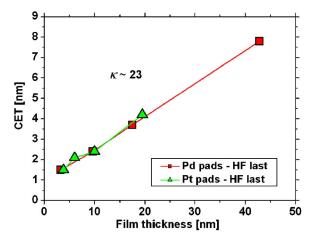

In Fig. 5 the capacitance equivalent thickness of the gate stacks is plotted versus the film thickness determined by XRR measurements. The data shown are from two different sample series on HF last surface with different top contact metals (Pd and Pt). All the data points lie on a straight line.

FIG. 5. (Color online) CET plots of sample series on HF last surface with different top contact metals. From the slope of the plots a  $\kappa$  value of  $\approx$ 23 can be derived.

No significant difference between the different contact pads is observed. From the slope of the linear fit a  $\kappa$  value of  $\approx 23$  is derived which is comparable to  $\mathrm{HfO_2}$ . CET plots of samples on thermal oxide or HF last surface with Au top contacts reveal similar  $\kappa$  values (not shown). The intersect of the plots with the CET axis at 0.9 nm indicates the existence of a thin interfacial layer between the high- $\kappa$  dielectric and the silicon substrate with a dielectric constant lower than  $\mathrm{GdScO_3}$ . The possible origin of such a layer has still to be analyzed. A detailed investigation on the interface morphology and the possibilities for modification by variation of the deposition and annealing parameters is in progress.

In summary, with electron beam evaporation a stoichiometric transfer of gadolinium scandate thin films from a stoichiometric ceramic source in ultrahigh vacuum conditions could be demonstrated. The films show very promising properties for high- $\kappa$  applications. Homogeneous and particulate free depositions linear with time were achieved. The surface of the films is very smooth (rms roughness <0.1 nm). In situ high temperature XRD measurements proved an excellent thermal stability of the amorphous phase up to  $1000 \,^{\circ}$ C. TEM micrographs show a SiO<sub>x</sub> free interface on HF dipped silicon after deposition. The electrical investigations reveal low leakage current densities (770  $\mu$ A/cm<sup>2</sup> for a CET of 1.5 nm) C-V curves with a small hysteresis and a dielectric constant of  $\approx$ 23 independent of the gate metal used.

One of the authors (M.W.) gratefully acknowledges the financial support by the European network of excellence "SI-NANO." Another author (T.H.) gratefully acknowledges the financial support by the Deutsche Forschungsgemeinschaft (Graduiertenkolleg GRK 549 "Noncentrosymmetric Crystals"). The authors would like to thank D. Schlom for the supply with the evaporation source material.

<sup>&</sup>lt;sup>1</sup>International Technology Roadmap for Semiconductors: http://public.itrs.net/ (2004).

<sup>&</sup>lt;sup>2</sup>D. G. Schlom and J. H. Haeni, MRS Bull. **27**, 198 (2002).

<sup>&</sup>lt;sup>3</sup>S. G. Lim, S. Kriventsov, T. N. Jackson, J. H. Haeni, D. G. Schlom, A. M. Balbashov, R. Uecker, P. Reiche, J. L. Freeouf, and G. Lucovsky, J. Appl. Phys. **91**, 4500 (2002).

<sup>&</sup>lt;sup>4</sup>V. V. Afanas'ev, A. Stesmans, C. Zhao, M. Caymax, T. Heeg, J. Schubert, Y. Jia, and D. G. Schlom, Appl. Phys. Lett. **85**, 5917 (2004).

<sup>&</sup>lt;sup>5</sup>C. Zhao, T. Witters, B. Brijs, H. Bender, O. Richard, M. Caymax, T. Heeg, J. Schubert, V. V. Afanas'ev, A. Stesmans, and D. G. Schlom, Appl. Phys. Lett. 86, 132903 (2005).

<sup>&</sup>lt;sup>6</sup>K. Hyoungsub, P. C. McIntyre, and K. C. Saraswat, Appl. Phys. Lett. **82**, 106 (2003).

<sup>&</sup>lt;sup>7</sup>Y.-S. Lin, R. Puthenkovilakam, and J. P. Chang, Appl. Phys. Lett. **81**, 2041 (2002).