# Low temperature deposition of high-k/ metal gate stacks on high-Sn content (Si)GeSn-alloys

C. Schulte-Braucks<sup>1\*</sup>, N. von den Driesch<sup>1</sup>, S. Glass<sup>1</sup>, A.T. Tiedemann<sup>1</sup>, U. Breuer<sup>2</sup>, A. Besmehn<sup>2</sup>, J.-M. Hartmann<sup>3</sup>, Z. Ikonic<sup>4</sup>, O.T Zhao<sup>1</sup>, S. Mantl<sup>1</sup> and D. Buca<sup>1\*</sup>

<sup>1</sup>Peter Gruenberg Institute 9 (PGI 9) and JARA-FIT, Forschungszentrum Juelich GmbH, 52425 Juelich, Germany

<sup>2</sup>Zentralinstitut für Engineering, Elektronik und Analytik (ZEA-3), Forschungszentrum Juelich GmbH, 52425 Juelich, Germany

<sup>3</sup>Univ. Grenoble Alpes, 38000 Grenoble, France and CEA, LETI, Minatec Campus, 38054 Grenoble, France

<sup>4</sup>Institute of Microwaves and Photonics, School of Electronic and Electrical Engineering, University of Leeds, UK

Keywords: GeSn, high-k/metal gate, low energy direct band gap, high-mobility, atomic vapor deposition

#### **ABSTRACT**

(Si)GeSn is an emerging, group IV alloy system, offering new exciting properties, with great potential for low power electronics due to the fundamental direct bandgap and prospects as high mobility material. In this article we present a systematic study of HfO<sub>2</sub>/TaN high-k/metal gate stacks on (Si)GeSn ternary alloys and low temperature processes for large scale integration of Sn based alloys. Our investigations indicate that SiGeSn ternaries show enhanced thermal stability compared to GeSn binaries, allowing the use of the existing Si technology. Despite the multielemental interface and large Sn content of up to 14 at.%, the HfO<sub>2</sub>/(Si)GeSn capacitors show small frequency dispersion and stretch-out. The good interface passivation is also supported by a low leakage current of 2x10<sup>-8</sup> A/cm<sup>2</sup> at -1 V and a high breakdown field of ~8 MV/cm. For large Sn content SiGeSn/GeSn direct bandgap heterostructures, process temperatures below 350°C are required for integration. We developed an atomic vapor deposition process for TaN metal gate on HfO<sub>2</sub> high-k dielectric and validated it by resistivity as well as temperature and frequency dependent capacitance-voltage measurements of capacitors on SiGeSn and GeSn. The densities of interface traps are deduced to be in the low 10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup> range and do not depend on the Snconcentration. The new processes developed here are compatible with (Si)GeSn integration in large scale applications.

## INTRODUCTION

Sn-based alloys, GeSn and SiGeSn, are emerging group IV semiconductors with applications in Si-photonics<sup>1,2</sup>, Complementary Metal Oxide Semiconductor (CMOS) nanoelectronics<sup>3</sup> or solar cells<sup>4</sup>. The great application potential arises from the novel latitude of tuning group IV material properties in terms of bandgap with direct/indirect transitions<sup>5,6</sup>, high/low effective masses<sup>7</sup>, and mobility. Here, we focus on Sn based alloys for electronics, primarily motivated by theoretical predictions of reduced effective masses of electrons and holes<sup>7,8</sup>, placing GeSn on the roadmap of potential high mobility channel materials for future low power CMOS devices<sup>9</sup>. Even though Sn based semiconductor electronics is still at the very beginning, MOS-Field Effect Transistors (MOSFETs)<sup>10,11</sup> and Tunneling FETs (TFETs)<sup>12,13</sup> have been fabricated and improvements of both, electron and hole mobilities as compared to Ge based devices have been achieved. However, so far mostly binary GeSn layers with low Sn contents under high compressive strain have been used, where the advantages over Ge are limited. Myriad of advantages are expected at Sn atomic concentration over 10%, where the bandgap becomes direct and the contribution of electrons from the  $\Gamma$ -valley becomes significant. The direct bandgap was recently experimentally proven by laser action in Ge<sub>0.88</sub>Sn<sub>0.12</sub> waveguides<sup>14</sup>. By allowing direct band-to-band-tunneling it can serve as a booster for the tunneling current in TFETs as recently demonstrated by the observation of characteristic negative differential resistance in p-i-n Ge<sub>0.89</sub>Sn<sub>0.11</sub> tunneling diodes<sup>15</sup>. A major challenge of high Sn content GeSn technology is the limited thermal processing budget<sup>16</sup>, as a consequence of the low solid solubility of Sn in Ge (less than 1 at.%). It has been predicted that incorporation of Si in GeSn

would improve the thermal stability due to an increased mixing entropy in the ternary, as compared to a corresponding binary with the same Sn concentration<sup>17</sup>.

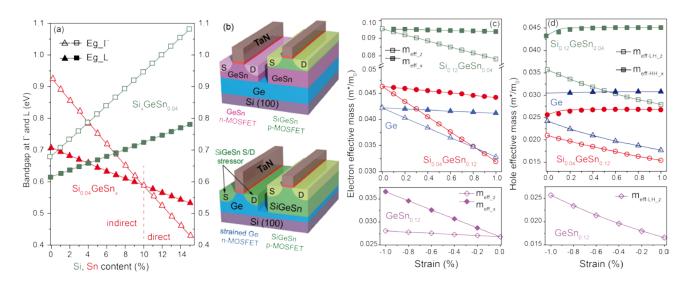

SiGeSn ternaries are another class of group IV semiconductors, which complement the properties of GeSn binaries. Due to their larger and mostly indirect band gap, SiGeSn ternaries have been considered solely as cladding layers for GeSn lasers<sup>18,19</sup>, drain material for TFETs<sup>13,20</sup> or as buffers for solar cells<sup>4</sup>. With Si, Sn and strain as tunable parameters, the bandgap, band offsets and lattice parameters can be widely varied, enabling novel heterostructures and applications. We expect substantial advantages from SiGeSn alloys in terms of process technology and device applications. This is substantiated by band structure calculations using 8x8 k.p method<sup>21</sup>, revealing a large tunability of SiGeSn. Fig. 1a shows the evolution of the bandgap for cubic SiGeSn alloys for fixed Sn (Si) content of 4% and variable Si (Sn) content. Accordingly, alloying with Si shifts both  $\Gamma$  and L valleys upwards, increasing the bandgap, while the incorporation of Sn reduces it, and for certain (Si,Sn) compositions the alloy becomes a direct bandgap semiconductor<sup>22</sup>.

Figure 1: Bandgap at  $\Gamma$  and L-valley (a) for variable Si (Sn) content from 0-15% and fixed Sn (Si) content of 4%, green (red). (b) Possible integration scheme for GeSn or Ge n-type with

SiGeSn p-type MOSFET devices on the same chip. (c,d) Electron and hole effective masses vs. biaxial tensile strain for several (Si)GeSn alloys (upper panels) and compressive strain for GeSn alloys (lower panels) demonstrating the usefulness of GeSn and SiGeSn for n- and p-type devices respectively.

High quality epitaxial growth of SiGeSn layers is performed on Ge (virtual) substrates (grown on Si(001)) or in the case of heterostructures on GeSn buffers, resulting in a tetragonal distortion of the SiGeSn lattice. The strain in SiGeSn changes from tensile to compressive, depending on the substrate and Si/Sn ratio<sup>23</sup>: Epitaxial Si<sub>0.12</sub>GeSn<sub>0.04</sub> is almost strain free (ε= -0.09 %) on Ge or highly tensile strained ( $\varepsilon = 1.75\%$ ) on cubic Ge<sub>0.88</sub>Sn<sub>0.12</sub> alloy. In the higher Sn content alloy  $Si_{0.04}GeSn_{0.12}$  the strain changes from large compressive  $\varepsilon = -1.64\%$  on Ge to slightly tensile  $\varepsilon = 0.17\%$  on  $Ge_{0.88}Sn_{0.12}$ . Lattice strain influences the electronic band structure appreciably and may lead even to indirect to direct bandgap transitions<sup>8</sup>. Si<sub>0.04</sub>GeSn<sub>0.12</sub> used in this work, becomes direct at a strain level of ~ 0.07%. Lattice mismatch induced strain can be used to stress Ge or GeSn channels via source/drain GeSn stressors<sup>24,25</sup> as indicated in Fig.1b. The high Sn content GeSn binaries, in practice mostly under compressive strain, show the lowest electron effective mass of all Ge based alloys, including tensile strained Ge (Fig 1c). The SiGeSn ternaries may exhibit lower hole effective masses as compared to Ge (Fig 1d). Thus, a practical integration scheme for drift-diffusion based MOSFETs includes GeSn for n-FETs and SiGeSn for p-FETs, as illustrated in Fig.1b. Epitaxial growth of this kind of heterostructures has been reported in the literature <sup>13,26</sup>.

In the following we present a systematic study of (Si)GeSn MOS capacitors (MOScaps) as a key process module for (Si)GeSn devices. The surface pre-high-k cleaning and the formed high-k/(Si)GeSn interface are characterized in detail for a large variety of GeSn binaries and

SiGeSn ternaries ranging from indirect to direct semiconductors via physical and electrical measurements. The novelties here are the first characterization of group IV ternaries based capacitors and the proof of their enhanced thermal stability, compared to that of binaries. In the second part we present the development of a low temperature atomic vapor deposition (AVD) metal gate process allowing to cope with the limited thermal budget of very high-Sn content direct bandgap GeSn alloys. As a major result, the complete gate stack deposition process in 300 mm wafer industrial reactors is developed and validated electrically by capacitance-voltage (CV) measurements.

#### **EXPERIMENTAL**

The pseudomorphic and partially strain relaxed (Si)GeSn binary and ternary epilayers with Sn-contents from 3% to 14% and Si contents between 0% and 10% have been grown by reduced pressure chemical vapor deposition (RP-CVD) on 200 mm Ge-buffered Si(001) wafers e.g. Gevirtual substrates (Ge-VS). The precursor gases, Si<sub>2</sub>H<sub>6</sub>, Ge<sub>2</sub>H<sub>6</sub> and SnCl<sub>4</sub> were introduced simultaneously in the reactor via a dedicated showerhead that guaranteed a high uniformity over the 200 mm wafer. Rutherford-Backscattering-Spectrometry (RBS) was used to determine the thickness and stoichiometry of the epitaxial (Si)GeSn layers and X-ray diffraction to extract the residual compressive lattice strain. The high crystalline quality has been proven by Transmission Electron Microscopy (TEM) and ion channeling. Details on growth, physical and optical characterization of (Si)GeSn alloys can be found in Ref. <sup>27,28</sup>.

## Cleaning of (Si)GeSn prior high-k deposition

Surface preparation prior to dielectric deposition plays a crucial role in controlling the high-k/(Si)GeSn interface quality, ultimately affecting the electrostatic performance of FET-devices. The high-k/GeO<sub>2</sub>/Ge interface, which is very different from the stable and low defect

density SiO<sub>2</sub>/Si interface, suffers from both chemical (solubility in water) and thermal instability (formation of GeO<sub>x</sub> sub-oxides). Great efforts have been made to achieve low densities of interface traps (D<sub>it</sub>) on Ge<sup>29-32</sup>. (Si)GeSn alloys hold similar constraints regarding the control of the interface with high-k gate dielectrics, which includes optimization of the wet cleaning procedure prior to pre- high-k deposition<sup>33</sup>. Standard CMOS cleaning solutions, such as H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O (CARO), NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (SC1) or HCl:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (SC2), use H<sub>2</sub>O<sub>2</sub> as oxidant which strongly chemically etches GeSn alloys, resulting in material loss and surface roughening. As a consequence, a modified pre-high-k deposition cleaning procedure has been used: after a pre-clean in an ultrasonic acetone bath, residual particles and organic contamination were removed in a 60°C hot ultrasonic bath of dimethyl sulfoxide (DMSO):cyclopentanone (10:3) followed by exposure to an inductively coupled oxygen plasma. Potential residual metallic contamination and native oxides were removed in HF:HCl (1% aq.) without a water rinse afterwards (called "HF:HCl-last"). The formation of an ultrathin SiO2 or GeO2 layer was found to be beneficial for the improvement of interface electrical properties of Si and Ge, respectively<sup>31</sup>. However, the formation of SnO<sub>2</sub> can be detrimental, as SnO<sub>2</sub> is known to exhibit metallic behavior<sup>34</sup>. Consequently, a chemically controlled surface prior to high-k deposition is of critical importance. X-ray photoelectron spectroscopy (XPS) has been used to analyze the surface (and near surface region) chemical composition before and after the cleaning procedure.

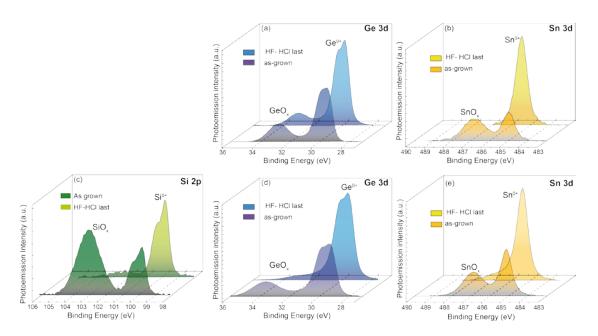

Figure 2: XPS-analysis of (a,b) Ge<sub>0.875</sub>Sn<sub>0.125</sub> and (c-e) Si<sub>0.1</sub>Ge<sub>0.81</sub>Sn<sub>0.09</sub>-surface. "HF:HCl last" cleaning significantly reduces the SiO<sub>x</sub>, GeO<sub>x</sub> and SnO<sub>x</sub> peak intensities. The transfer to the XPS-tool occurred ex-situ.

XPS analysis of the core level spectra of the SiGeSn surface was performed in a PHI5000 VersaProbe II tool with monochromatic Al  $K_{\alpha}$  X-rays at 1486.7 eV. As the sample transfer to the XPS-tool occurred *ex-situ*, the C1s peak at 285.0 eV served as a reference. The information of interest here is the oxidation state of the Si, Ge and Sn atoms. Fig.2 shows the Si2p, Ge3d and Sn3d peaks of  $Ge_{0.875}Sn_{0.125}$  and  $Si_{0.1}Ge_{0.81}Sn_{0.09}$  prior to and after cleaning. Despite the *ex-situ* sample transfer into the XPS chamber, the  $SiO_x$  and  $GeO_x$  signals were reduced significantly and  $SnO_x$  was completely removed from the (Si)GeSn-surface.

The cleaned (Si)GeSn substrates were loaded into the 300 mm ALD reactor and 5 nm HfO<sub>2</sub> was deposited at 300°C. The Hf precursor, liquid Tetrakis EthylMethylAmino Hafnium, (TEMAH), Hf [N(CH<sub>3</sub>)(C<sub>2</sub>H<sub>5</sub>)]<sub>4</sub>, was injected in pulses followed by ozone (O<sub>3</sub>) pulses. In order to allow direct comparison with our previous study on strained Ge and GeSn MOScap results, we used the same HfO<sub>2</sub> deposition sequence and parameters as in Ref.<sup>8</sup> In the first approach the gate

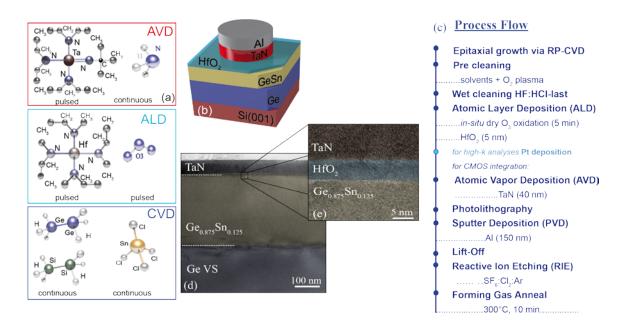

stack was finalized with Pt deposition as top metal contact. In the second part of the paper, we present the optimization of low-temperature TaN AVD process which allows *in-situ* deposition of the whole gate stack (vacuum transfer between the 300 mm ALD (HfO<sub>2</sub>) and AVD (TaN) reactors). For samples with TaN 150 nm thick Al was sputter-deposited and a lift-off process was used to fabricate electrical contact pads. Subsequently, the Al pads acted as hard masks for the metal gate etch in a SF<sub>6</sub>:Cl<sub>2</sub>:Ar reactive ion etching plasma. The fabrication ended with a 300°C forming gas annealing (N<sub>2</sub>:H<sub>2</sub>/4:1) for 10 min. The complete description of the MOS capacitors fabrication including the precursors and their injection mechanism used for the growth of the (Si)GeSn, HfO<sub>2</sub> and TaN, is schematically illustrated in Fig.3a-c. The cross-sectional TEM-images in Figs.3d,e show the high crystalline quality of the Ge-VS/GeSn/HfO<sub>2</sub>/TaN heterostructure after the complete gate stack process, including the forming gas annealing. The smooth HfO<sub>2</sub>/GeSn interface is clearly visible (Fig. 3e).

Figure 3: (a) The precursors used for layer deposition and their injection mechanism. (b)

Schematic layer stack and (c) fabrication process flow. (d,e) TEM-micrograph of a

TaN/HfO<sub>2</sub>/Ge<sub>0.875</sub>Sn<sub>0.125</sub> stack showing the excellent crystalline quality of the GeSn layer and a smooth high-k/GeSn interface.

#### Electrical Characterization

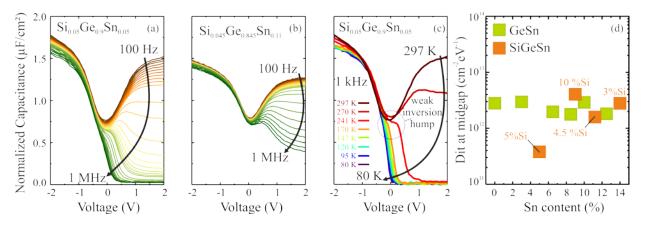

The MOScap fabrication process has been applied for (Si)GeSn alloys with a broad range of Si/Sn ratios corresponding to a bandgap ranging from 0.66 eV (for Si<sub>0.1</sub>Ge<sub>0.81</sub>Sn<sub>0.09</sub>) to 0.45 eV (for Ge<sub>0.875</sub>Sn<sub>0.125</sub>), as calculated by the 8-band k·p method. The current voltage (I-V) characteristics show low leakage currents of 2x10<sup>-8</sup> A/cm<sup>2</sup> at -1 V and a high breakdown field of ~8 MV/cm, indicating good mesa passivation with negligible diffusion of Sn into the high-k layer. The electrical quality of the HfO<sub>2</sub>/(Si)GeSn interface was investigated by temperature dependent capacitance - voltage (C-V) measurements. The frequency dependent C-V characteristics at 300 K of HfO<sub>2</sub>/Si<sub>0.05</sub>Ge<sub>0.9</sub>Sn<sub>0.05</sub> and HfO<sub>2</sub>/Si<sub>0.045</sub>Ge<sub>0.845</sub>Sn<sub>0.11</sub> MOScaps are shown as examples in Fig.4 a,b. The capacitors feature a very low frequency dispersion in accumulation and a small frequency dependent flat-band voltage shift suggesting a good interface quality. The small bandgap of the Si<sub>0.045</sub>Ge<sub>0.845</sub>Sn<sub>0.11</sub> layer translates into C-V characteristics similar to that of state-of-the-art III-V MOS-structures<sup>35</sup>.

The variation of the alloys bandgap induces a characteristic carrier response in the C-V curves: lower bandgap semiconductors show very strong minority inversion response even at relatively high frequencies, featuring a significant so-called "weak inversion hump". The hump stems from an enhanced interaction of mid-gap traps with the conduction and the valence bands, promoted by the low-bandgap<sup>8,36</sup>. In this case the weak inversion hump does not stem from a high density of interface trap states, known as the D<sub>it</sub> - hump, as in larger bandgap materials such as Si. As a consequence, these effects exclude the use of the conduction method for a reliable extraction of D<sub>it</sub> at room temperature, which would lead to a misinterpretation of the weak

inversion as the D<sub>it</sub> contribution. Low temperature C-V measurements reduce the minority carrier response at the expense of a reduced region in the bandgap where the trap positions are sampled<sup>8,36</sup>. Fig.4c shows the temperature dependence of C-V characteristics between 80 K and 300 K recorded at 1 kHz for the SiGeSn MOScap of Fig.4a. The effect of temperature on the response of minority carriers is clearly evidenced: below 170 K the weak inversion hump is completely suppressed, allowing the use of the conductance method. The values of D<sub>it</sub> at midgap, extracted for a set of GeSn binaries and SiGeSn ternary MOScaps structures with both Si and Sn-contents ranging from 0% to 14%, are plotted in Fig.4d. The D<sub>it</sub> is around 2x10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup> and appears to be almost independent of the Sn-content in the investigated region.

Figure 4: (a,b) C-V characteristics of 5 nm HfO<sub>2</sub>/SiGeSn MOScaps with different Si/Sn ratios. The higher Sn-content in (b) results in a lower bandgap and an enhanced minority carrier response. (c) Temperature dependent measurements at 1 kHz. (d) Density of interface states at mid-gap for several GeSn and SiGeSn samples.

## Thermal stability of GeSn and SiGeSn with large Sn contents

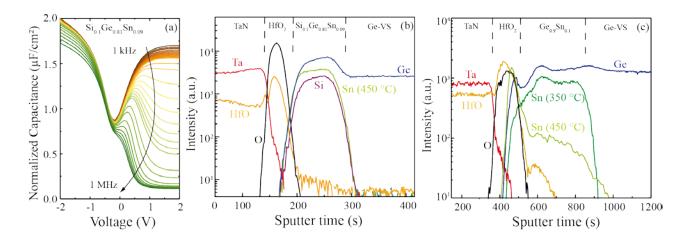

A commercially available industry 300 mm ALD - AVD deposition cluster enables in-situ wafer transfer between the reactors, highly desirable for process integration and reliability. SiGeSn and GeSn MOScaps were fabricated using 300 mm ALD - AVD deposition processes as used for Si and Ge MOSFETs. A typical Si-technology AVD metal gate process requires a deposition temperature of  $\geq 450^{\circ}\text{C}^{37}$ , which is much above the 350°C growth temperature used for direct bandgap (Si)GeSn alloys. However, well behaving C-V characteristics were measured for Si<sub>0.1</sub>Ge<sub>0.81</sub>Sn<sub>0.09</sub> with a stack of TaN/HfO<sub>2</sub> deposited at 450°C (Fig. 5a). The CVcharacteristics are comparable to those of the Pt metal contacts deposited at room temperature. This is due to the higher thermal stability of the channel/gate stack compared to the Ge<sub>0.9</sub>Sn<sub>0.1</sub> binary, as confirmed experimentally by time-of-flight secondary ion mass spectroscopy (ToF-SIMS) measurements in Fig.5b,c. In contrast, the SIMS spectra of MOScaps fabricated on Ge<sub>0.9</sub>Sn<sub>0.1</sub> with nearly the same Sn content as for the Si<sub>0.1</sub>Ge<sub>0.81</sub>Sn<sub>0.09</sub>, show strong Sn diffusion both into the high-k and into the Ge-VS when using the same metal gate process at 450°C (bright green curve in Fig.5c). Sn diffusion may lead to metallic β-Sn precipitates, degrading the gatestack and leading to a strong increase of the leakage current 16,38. However when reducing the metal gate deposition temperature to 350°C Sn-diffusion in Ge<sub>0.9</sub>Sn<sub>0.1</sub> is significantly suppressed (dark-green curve in Fig.5c). Therefore, the processing of direct bandgap GeSn semiconductors requires a reduction of the AVD temperature.

Figure 5: (a) CV-characteristics of MOScap fabricated with 450°C AVD TaN on Si<sub>0.1</sub>Ge<sub>0.81</sub>Sn<sub>0.09</sub>. (b,c) ToF-SIMS analysis of MOScaps with AVD-TaN deposited on HfO<sub>2</sub>/Si<sub>0.1</sub>Ge<sub>0.81</sub>Sn<sub>0.09</sub> and on HfO<sub>2</sub>/Ge<sub>0.9</sub>Sn<sub>0.1</sub>. No significant Sn-diffusion is observed for 450°C TaN deposition on SiGeSn alloys, demonstrating an enhanced thermal stability of SiGeSn alloys compared to that of binary GeSn. For GeSn the AVD deposition temperature has to be reduced to 350°C. The high HfO intensity in the TaN-layer is caused by mass interferences between HfO and TaN.

## In-situ low temperature TaN deposition in an ALD/AVD cluster tool

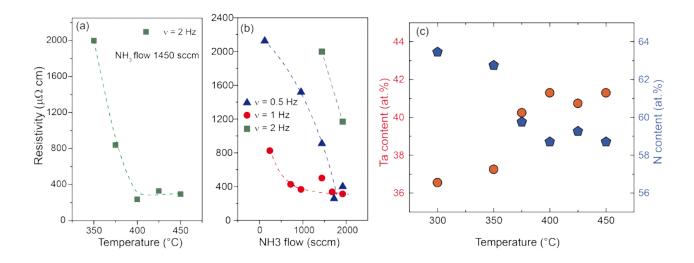

One of the most important characteristics of the metal gate is its sheet resistance to ensure fast switching and low losses, especially for low power devices. Lowering the deposition temperature to 350°C requires process optimization in order to avoid a significant increase of the TaN resistivity for reduced deposition temperatures, as indicated by Van der Pauw measurements in Fig.6a.

Figure 6: Resistivity of AVD deposited TaN as a function of (a) the deposition temperature and (b) the NH<sub>3</sub> flow as well as precursor pulse frequency at 350°C. (c) Deposition temperature dependence of TaN stoichiometry. Growth temperature reduction leads to N-rich TaN phase formation, with increased resistivity.

During the AVD process the Ta precursor, Tris(diethylamido)(Tert-butylimino)Tantalum (TBTDET), [((C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>N)<sub>3</sub>(C<sub>4</sub>H<sub>9</sub>N)Ta], is injected in pulses in the reactor and the reduction agent ammonia, NH<sub>3</sub>, is delivered continuously. At temperatures below 600°C the nitrogen in TaN is supplied in a ligand exchange reaction of both precursors<sup>39</sup>. Solely a reduction of the process temperature results in an incomplete reaction, leading to stoichiometry changes and contamination of the film with carbon rich by-products <sup>40</sup>. ALD or AVD grown TaN films typically consist of a mixture of different phases (TaN, Ta<sub>2</sub>N, Ta<sub>5</sub>N<sub>6</sub>, Ta<sub>3</sub>N<sub>5</sub>, Ta<sub>2</sub>O<sub>5</sub>) and their relative fractions determine the total resistivity. <sup>41</sup> Generally, Ta rich phases (Ta<sub>2</sub>N, TaN) are metallic, while the N-rich phases such as Ta<sub>5</sub>N<sub>6</sub> have higher resistance or insulating /semiconducting properties (Ta<sub>3</sub>N<sub>5</sub>)<sup>42,43</sup>. The Ta/N-ratio was determined on TaN-films directly grown on Si substrates at various temperatures using RBS in channeling mode, in order to reduce the influence of the Si-substrate. The Ta/N ratio of 0.70 at 450°C decreases to only 0.57 for

300°C (see Fig.6c), suggesting a predominance of the insulating Ta<sub>3</sub>N<sub>5</sub> phase, which increases the resistivity for low deposition temperatures.

Optimization of the AVD process parameters was performed by tuning the Ta precursor injection frequency and the NH<sub>3</sub> flow, as both affect the chemical reactions. The resistivity of TaN films deposited at 350°C is plotted in Fig.6b as a function of the NH<sub>3</sub> flow for different injection frequencies v, at a constant injector opening time of 10 ms. The presence of NH<sub>3</sub> is known to be beneficial for TBTDET deposited TaN in order to form a dense film and to reduce the carbon content by formation of volatile by-products such as short-chain amines<sup>44–46</sup>. The reduced reactivity at lower temperatures is compensated by an increased NH<sub>3</sub> flow and leads to a significant decrease of the resistivity. With optimized deposition parameters the resistivity of TaN could be reduced by an order of magnitude, from 2000  $\mu\Omega$ ·cm down to 200  $\mu\Omega$ ·cm.

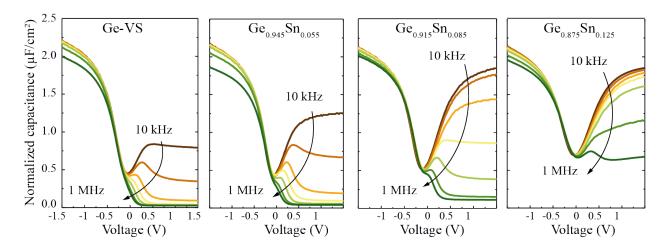

The optimized AVD TaN metal gate process has been successfully applied to a series of GeSn substrates with 5.5 % Sn, 8.5 % Sn and 12.5 % Sn, as well as to Ge-VS for comparison. The C-V characteristics for frequencies from 10 kHz to 1 MHz are plotted in Fig.7. For the AVD metal gate the HfO<sub>2</sub>-thickness was kept at 5 nm and the leakage current remained at ~2x10<sup>-8</sup> A/cm<sup>-2</sup> at -1 V indicating no significant Sn-diffusion into the high-k/metal gate stack. A continuous increase of the inversion response for increased Sn-content is noticeable, associated with decrease of the bandgap. The physics of this behavior is beyond the scope of this work and will the subject of further studies.

Figure 7: C-V characteristics of various GeSn capacitors fabricated using optimized 20 nm TaN/5 nm HfO2 gate stacks.

## **SUMMARY**

In summary, we have fabricated and analyzed TaN/HfO<sub>2</sub> high-k/metal gate stacks on low bandgap group IV GeSn and SiGeSn alloys with a large stoichiometry range. The surface treatment prior to metal gate deposition has been optimized for (Si)GeSn. Electrical as well as physical analysis confirmed the good interfacial quality of the high-k/metal gate stacks with D<sub>it</sub> values ~ 2x10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup>. We have presented the first study of SiGeSn MOS capacitors with an enhanced thermal stability, as compared to GeSn with Sn concentrations where it possesses a direct bandgap. With the aim of CMOS compatible device fabrication from Sn-based direct band gap group IV alloys, we have developed a low temperature atomic vapor deposition process for TaN metal gates. Our high-k/metal gate process has been validated by electrical characteristics on various high Sn contents (Si)GeSn alloys with bandgaps around ~0.45-0.70 eV. With the now available high-k/metal gate process, together with Ni(Si)GeSn metal contact formation on high Sn content (Si)GeSn alloys<sup>25</sup> the fabrication of FET devices on direct band gap (Si)GeSn is in progress.

#### ASSOCIATED CONTENT

**Supporting Information**. Not available. This material is available free of charge via the Internet at <a href="http://pubs.acs.org">http://pubs.acs.org</a>.

### **AUTHOR INFORMATION**

# **Corresponding Author**

\*c.schulte-braucks@fz-juelich.de , d.m.buca@fz-juelich.de

#### ACKNOWLEDGMENT

This research received funding from the EU FP7 project E2SWITCH (619509) and the German Federal Ministry of Education and Research (BMBF) project UltraLowPow (16ES0060 K).

## REFERENCES

- (1) Soref, R. A.; Buca, D.; Yu, S.-Q. Group IV Photonics- Driving Integrated Optoelectronics. *Opt. Photonics News* **2016**, *January*, 32–39.

- (2) Soref, R. Group IV Photonics: Enabling 2 μm Communications. *Nat. Photonics* **2015**, *9* (6), 358–359.

- Yang, Y.; Guo, P.; Han, G.; Lu Low, K.; Zhan, C.; Yeo, Y.-C. Simulation of Tunneling Field-Effect Transistors with Extended Source Structures. *J. Appl. Phys.* **2012**, *111* (11), 114514.

- (4) Roucka, R.; Clark, A.; Landini, B. Si-Ge-Sn Alloys with 1.0 eV Gap for CPV Multijunction Solar Cells. In *11th International Conference on Concentrator Photovoltaic Systems*; 2015; Vol. 1679, p 040008.

- (5) Stange, D.; Wirths, S.; von den Driesch, N.; Mussler, G.; Stoica, T.; Ikonic, Z.; Hartmann, J. M.; Mantl, S.; Grützmacher, D.; Buca, D. Optical Transitions in Direct-Bandgap Ge 1– X Sn X Alloys. *ACS Photonics* **2015**, *2* (11), 1539–1545.

- (6) Ghetmiri, S. A.; Du, W.; Margetis, J.; Mosleh, A.; Cousar, L.; Conley, B. R.; Domulevicz,

- L.; Nazzal, A.; Sun, G.; Soref, R. A.; Tolle, J.; Li, B.; Naseem, H. A.; Yu, S. Direct-Bandgap GeSn Grown on Silicon with 2230 Nm Photoluminescence. *Appl. Phys. Lett.* **2014**, *105* (15), 151109.

- (7) Lu Low, K.; Yang, Y.; Han, G.; Fan, W.; Yeo, Y.-C. Electronic Band Structure and Effective Mass Parameters of Ge1–xSnx Alloys. *J. Appl. Phys.* **2012**, *112* (10), 103715.

- (8) Wirths, S.; Stange, D.; Pampillón, M.-A.; Tiedemann, A. T.; Mussler, G.; Fox, A.; Breuer, U.; Baert, B.; San Andrés, E.; Nguyen, N. D.; Hartmann, J.-M.; Ikonic, Z.; Mantl, S.; Buca, D. High- K Gate Stacks on Low Bandgap Tensile Strained Ge and GeSn Alloys for Field-Effect Transistors. ACS Appl. Mater. Interfaces 2015, 7 (1), 62–67.

- (9) Sau, J. D.; Cohen, M. L. Possibility of Increased Mobility in Ge-Sn Alloy System. *Phys. Rev. B* **2007**, *75* (4), 1–7.

- (10) Fang, Y.-C.; Chen, K.-Y.; Hsieh, C.-H.; Su, C.-C.; Wu, Y.-H. N-MOSFETs Formed on Solid Phase Epitaxially Grown GeSn Film with Passivation by Oxygen Plasma Featuring High Mobility. *ACS Appl. Mater. Interfaces* **2015**, *7* (48), 26374–26380.

- (11) Gupta, S.; Vincent, B.; Yang, B.; Lin, D.; Gencarelli, F.; Lin, J.-Y. J.; Chen, R.; Richard, O.; Bender, H.; Magyari-Kope, B.; Caymax, M.; Dekoster, J.; Nishi, Y.; Saraswat, K. C. Towards High Mobility GeSn Channel nMOSFETs: Improved Surface Passivation Using Novel Ozone Oxidation Method. *IEDM* 2012, 16.2.1–16.2.4.

- (12) Yang, Y.; Han, G.; Guo, P.; Wang, W.; Gong, X.; Wang, L.; Low, K. L.; Yeo, Y. Germanium-Tin P-Channel Tunneling Field-Effect Transistor: Device Design and Technology Demonstration. *IEEE Trans. Electron Devices* **2013**, *60* (12), 4048–4056.

- (13) Wirths, S.; Tiedemann, A. T.; Ikonic, Z.; Harrison, P.; Holländer, B.; Stoica, T.; Mussler, G.; Myronov, M.; Hartmann, J. M.; Grützmacher, D.; Buca, D.; Mantl, S. Band Engineering and Growth of Tensile Strained Ge/(Si)GeSn Heterostructures for Tunnel Field Effect Transistors. *Appl. Phys. Lett.* 2013, 102 (19), 192103.

- (14) Wirths, S.; Geiger, R.; Driesch, N. von den; Mussler, G.; Stoica, T.; Mantl, S.; Ikonic, Z.; Luysberg, M.; Chiussi, S.; Hartmann, J. M.; Sigg, H.; Faist, J.; Buca, D.; Grützmacher, D. Lasing in Direct-Bandgap GeSn Alloy Grown on Si. *Nat. Photonics* **2015**, *9*(2) (January), 88–92.

- (15) Schulte-Braucks, C.; Stange, D.; von den Driesch, N.; Blaeser, S.; Ikonic, Z.; Hartmann, J. M.; Mantl, S.; Buca, D. Negative Differential Resistance in Direct Bandgap GeSn P-I-N Structures. *Appl. Phys. Lett.* 2015, 107 (4), 042101.

- (16) Chen, R.; Huang, Y.-C.; Gupta, S.; Lin, A. C.; Sanchez, E.; Kim, Y.; Saraswat, K. C.; Kamins, T. I.; Harris, J. S. Material Characterization of High Sn-Content, Compressively-Strained GeSn Epitaxial Films after Rapid Thermal Processing. *J. Cryst. Growth* **2013**,

- *365*, 29–34.

- (17) Xie, J.; Chizmeshya, A. V. G.; Tolle, J.; Dcosta, V. R.; Menendez, J.; Kouvetakis, J. Synthesis, Stability Range, and Fundamental Properties of Si-Ge-Sn Semiconductors Grown Directly on Si(100) and Ge(100) Platforms. *Chem. Mater.* 2010, 22 (12), 3779–3789.

- (18) Soref, R. Mid-Infrared Photonics in Silicon and Germanium. *Nat. Photonics* **2010**, *4* (8), 495–497.

- (19) Wirths, S.; Ikonic, Z.; Tiedemann, A. T.; Holländer, B.; Stoica, T.; Mussler, G.; Breuer, U.; Hartmann, J. M.; Benedetti, A.; Chiussi, S.; Grützmacher, D.; Mantl, S.; Buca, D. Tensely Strained GeSn Alloys as Optical Gain Media. *Appl. Phys. Lett.* 2013, 103 (19), 192110.

- (20) Sant, S.; Schenk, A. Band-Offset Engineering for GeSn-SiGeSn Hetero Tunnel FETs and the Role of Strain. *IEEE J. Electron Devices Soc.* **2015**, *3* (3), 164–175.

- (21) Bahder, T. B. Eight-Band K · P M odel of Strained Zinc -Blende Crystals. *Phys. Rev. B* **1990**, *41* (17), 11992–12001.

- (22) Moontragoon, P.; Soref, R. a.; Ikonic, Z. The Direct and Indirect Bandgaps of Unstrained SixGe1-x-ySny and Their Photonic Device Applications. *J. Appl. Phys.* **2012**, *112* (7), 073106.

- (23) Wirths, S.; Troitsch, R.; Mussler, G.; Zaumseil, P.; Hartmann, J.-M.; Schroeder, T.; Mantl, S.; Buca, D. Ni(SiGeSn) Metal Contact Formation on Low Bandgap Strained (Si)Ge(Sn) Semiconductors. *ECS Trans.* **2014**, *64* (6), 107–112.

- (24) Vincent, B.; Shimura, Y.; Takeuchi, S.; Nishimura, T.; Eneman, G.; Firrincieli, a.; Demeulemeester, J.; Vantomme, a.; Clarysse, T.; Nakatsuka, O.; Zaima, S.; Dekoster, J.; Caymax, M.; Loo, R. Characterization of GeSn Materials for Future Ge pMOSFETs Source/drain Stressors. *Microelectron. Eng.* 2011, 88 (4), 342–346.

- (25) Wirths, S.; Troitsch, R.; Mussler, G.; Hartmann, J.-M.; Zaumseil, P.; Schroeder, T.; Mantl, S.; Buca, D. Ternary and Quaternary Ni(Si)Ge(Sn) Contact Formation for Highly Strained Ge P- and N-MOSFETs. *Semicond. Sci. Technol.* **2015**, *30* (5), 055003.

- (26) Stange, D.; von den Driesch, N.; Rainko, D.; Schulte-Braucks, C.; Wirths, S.; Mussler, G.; Tiedemann, A. T.; Stoica, T.; Hartmann, J. M.; Ikonic, Z.; Mantl, S.; Grützmacher, D.; Buca, D. Study of GeSn Based Heterostructures: Towards Optimized Group IV MQW LEDs. Opt. Express 2016, 24 (2), 1358.

- von den Driesch, N.; Stange, D.; Wirths, S.; Mussler, G.; Holländer, B.; Ikonic, Z.; Hartmann, J. M.; Stoica, T.; Mantl, S.; Grützmacher, D.; Buca, D. Direct Bandgap Group

- IV Epitaxy on Si for Laser Applications. Chem. Mater. 2015, 27 (13), 4693–4702.

- (28) Wirths, S.; Buca, D.; Ikonic, Z.; Harrison, P.; Tiedemann, A. T.; Holländer, B.; Stoica, T.; Mussler, G.; Breuer, U.; Hartmann, J. M.; Grützmacher, D.; Mantl, S. SiGeSn Growth Studies Using Reduced Pressure Chemical Vapor Deposition towards Optoelectronic Applications. *Thin Solid Films* **2014**, *557*, 183–187.

- (29) Lee, C. H.; Tabata, T.; Nishimura, T.; Nagashio, K.; Kita, K.; Toriumi, A. Ge/GeO2 Interface Control with High Pressure Oxidation for Improving Electrical Characteristics. In *ECS Transactions*; ECS, 2009; Vol. 19, pp 165–173.

- (30) Zhang, R.; Iwasaki, T.; Taoka, N.; Takenaka, M.; Takagi, S. Al2O3/GeOx/Ge Gate Stacks with Low Interface Trap Density Fabricated by Blectron Cyclotron Resonance Plasma Postoxidation. *Appl. Phys. Lett.* **2011**, *98* (11), 112902.

- (31) Matsubara, H.; Sasada, T.; Takenaka, M.; Takagi, S. Evidence of Low Interface Trap Density in GeO2 / Ge Metal-Oxide- Semiconductor Structures Fabricated by Thermal Oxidation. *Appl. Phys. Lett.* **2008**, *93* (3), 032104.

- (32) Hu, C.; McDaniel, M. D.; Jiang, A.; Posadas, A.; Demkov, A. A.; Ekerdt, J. G.; Yu, E. T. A Low-Leakage Epitaxial High-κ Gate Oxide for Germanium Metal–Oxide–Semiconductor Devices. *ACS Appl. Mater. Interfaces* **2016**, acsami.5b10661.

- (33) Brunco, D. P.; De Jaeger, B.; Eneman, G.; Mitard, J.; Hellings, G.; Satta, a.; Terzieva, V.; Souriau, L.; Leys, F. E.; Pourtois, G.; Houssa, M.; Winderickx, G.; Vrancken, E.; Sioncke, S.; Opsomer, K.; Nicholas, G.; Caymax, M.; Stesmans, a.; Van Steenbergen, J.; Mertens, P. W.; Meuris, M.; Heyns, M. M. Germanium MOSFET Devices: Advances in Materials Understanding, Process Development, and Electrical Performance. *J. Electrochem. Soc.* **2008**, *155* (7), H552.

- (34) Kılıç, Ç.; Zunger, A. Origins of Coexistence of Conductivity and Transparency in SnO\_{2}. *Phys. Rev. Lett.* **2002**, 88 (9), 095501.

- (35) Monaghan, S.; O'Connor, E.; Rios, R.; Ferdousi, F.; Floyd, L.; Ryan, E.; Cherkaoui, K.; Povey, I. M.; Kuhn, K. J.; Hurley, P. K. Capacitance and Conductance for an MOS System in Inversion, with Oxide Capacitance and Minority Carrier Lifetime Extractions. *IEEE Trans. Electron Devices* **2014**, *61* (12), 4176–4185.

- (36) Martens, K.; Chui, C. O.; Brammertz, G.; De Jaeger, B.; Kuzum, D.; Meuris, M.; Heyns, M.; Krishnamohan, T.; Saraswat, K.; Maes, H. E.; Groeseneken, G. On the Correct Extraction of Interface Trap Density of MOS Devices With High-Mobility Semiconductor Substrates. *IEEE Trans. Electron Devices* **2008**, *55* (2), 547–556.

- (37) Karim, Z.; Barbar, G.; Boissière, O.; Lehnen, P.; Lohe, C.; Seidel, T.; Adelmann, C.; Conard, T.; O'Sullivan, B.; Ragnarsson, L.-A.; Schram, T.; Van Elshocht, S.; De Gendt,

- S. AVD and MOCVD TaCN-Based Films for Gate Metal Applications on High K Gate Dielectrics. In *ECS Transactions*; ECS, 2007; Vol. 11, pp 557–567.

- (38) Wang, W.; Li, L.; Zhou, Q.; Pan, J.; Zhang, Z.; Tok, E. S.; Yeo, Y. Tin Surface Segregation, Desorption, and Island Formation during Post-Growth Annealing of Strained Epitaxial Ge1–xSnx Layer on Ge(001) Substrate. *Appl. Surf. Sci.* **2014**, *321*, 240–244.

- (39) Somani, S.; Mukhopadhyay, A.; Musgrave, C. Atomic Layer Deposition of Tantalum Nitride Using A Novel Precursor. *J. Phys. Chem. C* **2011**, *115* (23), 11507–11513.

- (40) Fang, Z.; Aspinall, H. C.; Odedra, R.; Potter, R. J. Atomic Layer Deposition of TaN and Ta3N5 Using Pentakis(dimethylamino)tantalum and Either Ammonia or Monomethylhydrazine. *J. Cryst. Growth* **2011**, *331* (1), 33–39.

- (41) Song, M.-K.; Rhee, S.-W. Formation of Tantalum Carbide and Nitride Phases in Atomic Layer Deposition Using Hydrogen Plasma and Tert -Butylimido-Tris(diethylamido)-Tantalum (TBTDET), and Its Effect on Material Properties. *Chem. Vap. Depos.* **2008**, *14* (11-12), 334–338.

- (42) Stampfl, C.; Freeman, A. J. Metallic to Insulating Nature of TaN Role of Ta and N Vacancies. *Phys. Rev. B* **2003**, *67* (6), 064108.

- (43) Stampfl, C.; Freeman, a. J. Stable and Metastable Structures of the Multiphase Tantalum Nitride System. *Phys. Rev. B* **2005**, *71* (2), 024111.

- (44) Weiller, B. H. Chemical Vapor Deposition of TiN from Tetrakis(dimethylamido)titanium and Ammonia: Kinetics and Mechanistic Studies of the Gas-Phase Chemistry. *J. Am. Chem. Soc.* **1996**, *118* (21), 4975–4983.

- (45) Won, Y. S.; Park, S. S.; Kim, Y. S.; Anderson, T. J.; McElwee-White, L. Computational Study on Transamination of Alkylamides with NH3 during Metalorganic Chemical Vapor Deposition of Tantalum Nitride. *J. Cryst. Growth* **2009**, *311* (14), 3587–3591.

- (46) Cho, S.-L. Diffusion Barrier Properties of Metallorganic Chemical Vapor Deposited Tantalum Nitride Films Against Cu Metallization. *J. Electrochem. Soc.* **1999**, *146* (10), 3724.