## DESIGN AND CRYOGENIC CHARACTERIZATION OF INTEGRATED CIRCUITS FOR QUANTUM COMPUTING

Alfonso Rafael Cabrera Galicia <sup>1</sup>, Arun Ashok <sup>1</sup>, Patrick Vliex <sup>1</sup>, Andre Kruth <sup>1</sup>, André Zambanini <sup>1</sup>, Stefan van Waasen <sup>1,2</sup>

- <sup>1</sup> Central Institute of Engineering, Electronics and Analytics, ZEA-2 Electronic Systems, Forschungszentrum Jülich GmbH, Germany

- <sup>2</sup> Faculty of Engineering, Communication Systems, University Duisburg-Essen, Germany

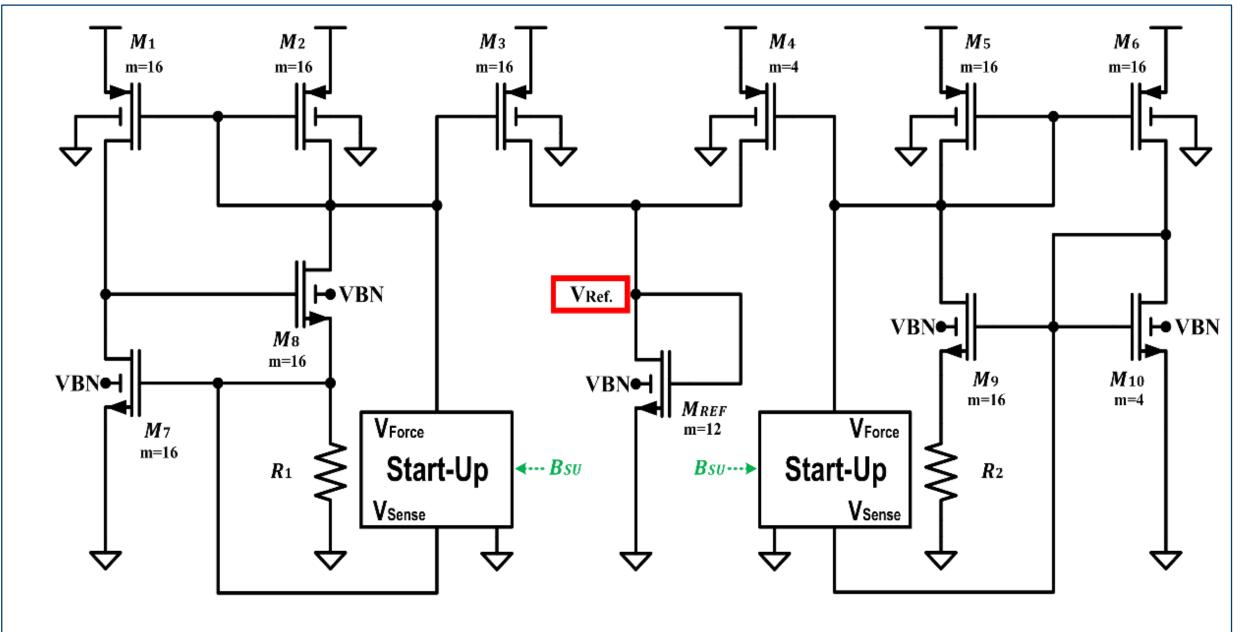

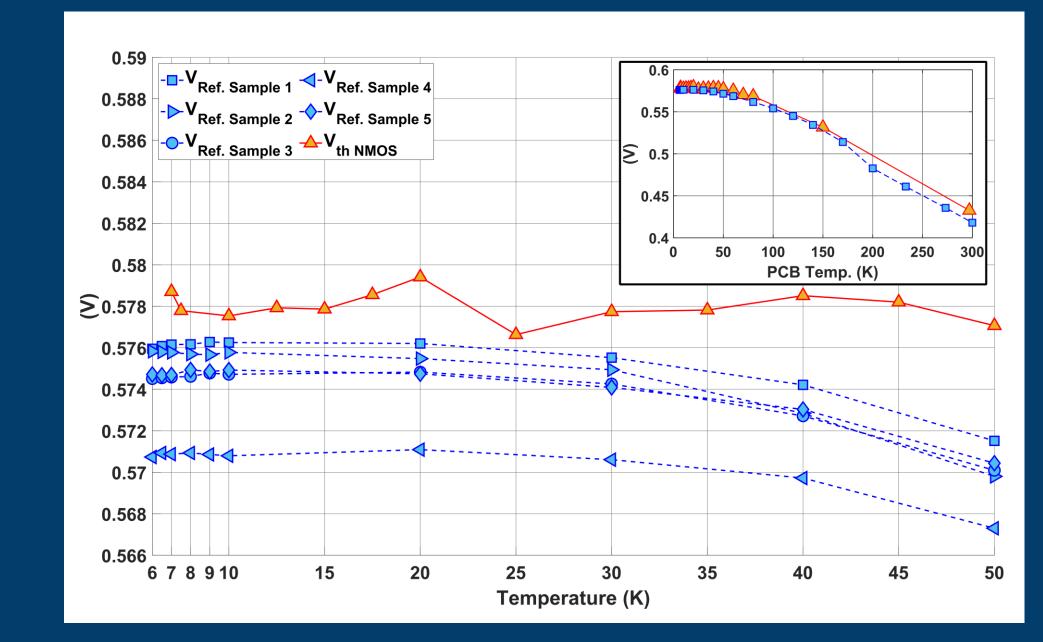

Fig. 1: Cryogenic voltage reference based on cryogenic Vth saturation phenomenon.

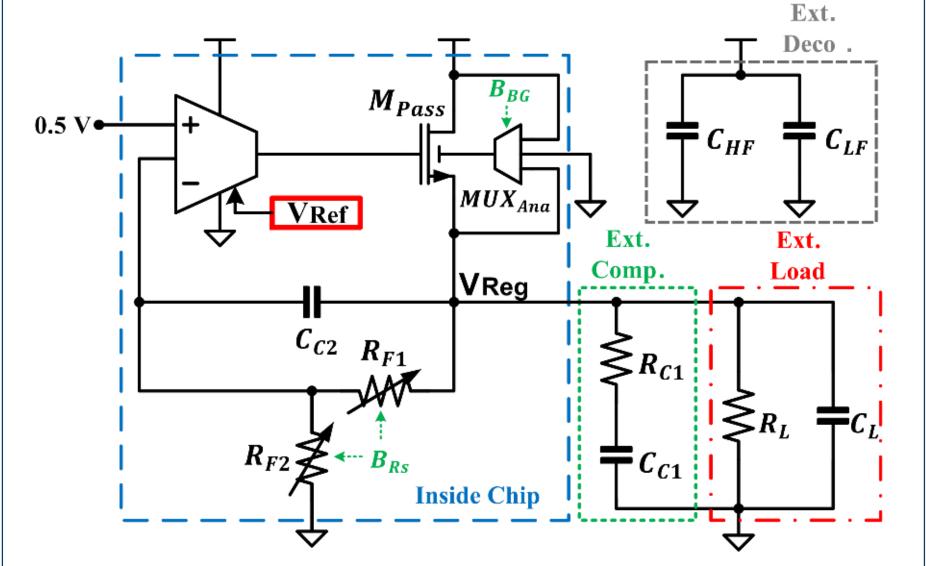

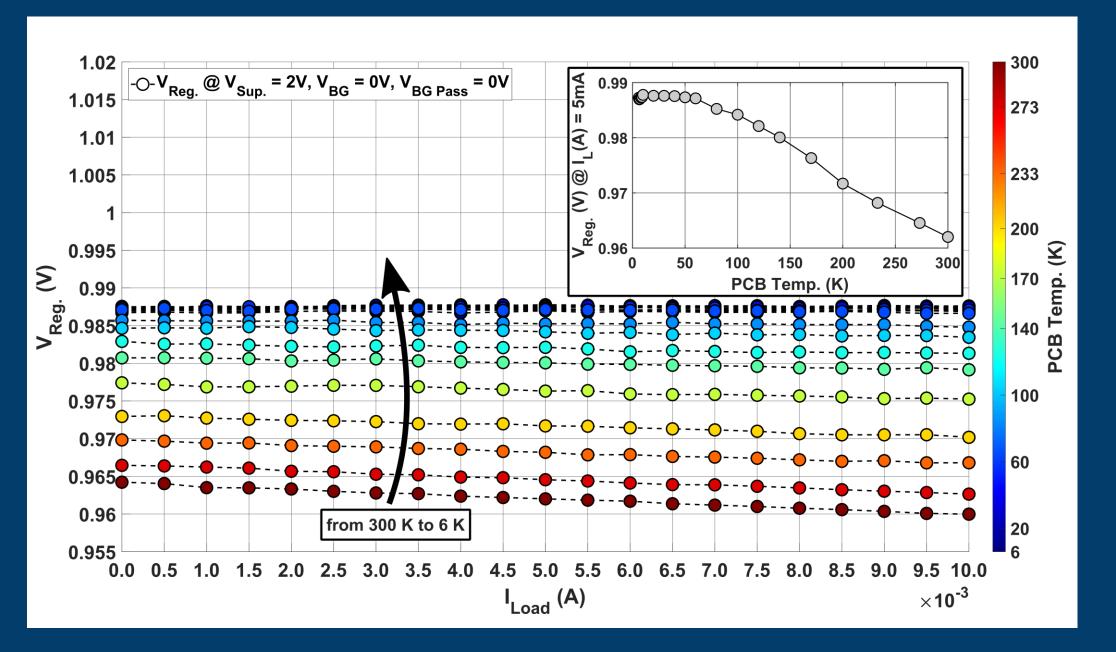

Fig. 2: Cryogenic voltage regulator, with its components integrated on chip and external elements.

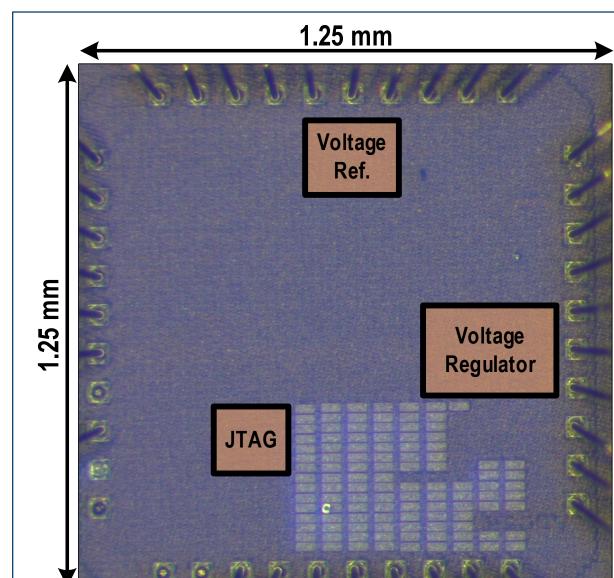

Fig. 3: Micrograph of a prototype IC manufactured in a commercial 22 nm FDSOI Technology.

## 1. MOTIVATION

- High performance Integrated Circuits (ICs) are a fundamental part of future Quantum Computers (QCs) [1].

- The ICs of QCs need regulated, stable and noise free supply voltages [2].

- Supply voltage lines in dilution fridges are prone to voltage ripple noise due to pulse tube vibrations, ground loops induce noise and dynamic load currents [3], [4].

- Cryogenic ICs for in situ voltage regulation can provide a clean voltage supply for the ICs of QCs.

- A voltage reference and a voltage regulator are presented as building blocks for cryogenic voltage regulation.

- The investigated circuits were developed in 22 nm FDSOI technology and tested from 6 K to 300 K.

## 2. INTEGRATED CIRCUITS DESCRIPTION

- The voltage reference circuit (Fig. 1) uses the cryogenic Vth saturation phenomenon as working principle.

- The circuit is composed of current sources that bias a diode connected NMOS device to yield the output reference voltage (VRef).

- VRef is a temperature stable quantity used in analog signal processing.

- The voltage regulator (Fig. 2) employs an NMOS pass element whose back-gate terminal connection can be shifted by an analog multiplexer via a JTAG interface.

- Back-gate shifting allows the NMOS pass element Vth reduction for power optimization at cryogenic temperatures.

- The output regulated voltage (VReg) can energize other cryogenic circuits with a stable power signal.

- The voltage reference, the voltage regulator and the JTAG interface are included in a prototype IC (Fig. 3) manufactured in a commercial 22 nm FDSOI technology.

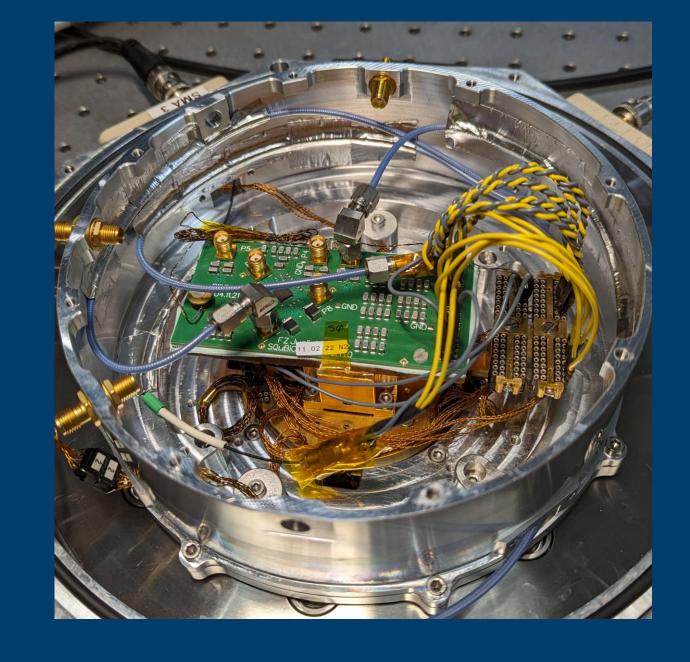

Fig. 4: Experimental setup: PCB with prototype IC, mounted onto the cryostat cold head (Gifford-McMahon cryocooler).

Fig. 5: Measured output from voltage reference over the temperature range of interest (6 K to 50 K), with VSup = 1.25 V and VBG = 0 V; results correspond to 5 sample chips. Extracted Vth from I/O NMOS (W = 1  $\mu$ m,  $L = 0.32 \mu m$ ) is added for comparison. Inset displays sample 1 data over a wider temperature range (6 K to 300 K).

Fig. 6: Measured regulator output voltage (VReg ) in relation to ILoad and temperature, at VIN Ref = 0.5 V, RF1 = RF2, VBG = 0 V and VSup = 2 V. Inset displays VReg for ILoad = 5 mA over temperature (from 6 K to 300 K).

## 3. EXPERIMENTAL RESULTS

- A prototype IC is mounted over the cryostat cold head (Gifford-McMahon cryocooler) via a PCB specially designed for good thermal coupling (Fig. 4).

- Fig. 5 shows the response from the voltage reference circuit, with a temperature coefficient of 300 ppm/K, over the 6 K to 50 K range.

- Fig. 6 shows the voltage regulator response, with load regulation of 22 mV/A at 6 K.

- The studied circuits served as exploration vehicles to gain inside into the design and electrical characterization of cryogenic ICs [5], [6].

Alfonso Rafael Cabrera Galicia PhD Researcher

a.cabrera.galicia@fz-juelich.de

**Electronic Systems (ZEA-2)** www.fz-juelich.de/en/zea/zea-2

<sup>&</sup>lt;sup>1</sup> E. Charbon, F. Sebastiano, A. Vladimirescu, H. Homulle, S. Visser, L. Song, and R. M. Incandela, "Cryo-cmos for quantum computing," in 2016 IEEE International Electron Devices Meeting (IEDM), 2016, pp. 13.5.1–13.5.4.

<sup>&</sup>lt;sup>2</sup> H. Homulle and E. Charbon, "Cryogenic low-dropout voltage regulators for stable low-temperature electronics," Cryogenics, vol. 95, 2018.

<sup>&</sup>lt;sup>3</sup> K. Rachpon et al. "Vibration-induced electrical noise in a cryogen-free dilution refrigerator: Characterization, mitigation, and impact on qubit coherence." Review of Scientific Instruments, 2016, vol. 87, no 7. <sup>4</sup> H. W. Ott, *Electromagnetic compatibility engineering*. John Wiley & Sons, 2011.

<sup>&</sup>lt;sup>5</sup> A. R. Cabrera-Galicia, A. Ashok, P. Vliex, C. Degenhardt, A. Kruth, A. Artanov, and S. van Waasen, "Towards the development of cryogenic integrated power management units," in 2022 IEEE 15th Workshop on Low Temperature Electronics (WOLTE), 2022, pp. 1–4. <sup>6</sup> A. R. Cabrera-Galicia, A. Ashok, P. Vliex, A. Kruth, A. Zambanini, and S. van Waasen, "A Cryogenic Voltage Reference in 22 nm FDSOI Technology," in 2023 IEEE 19th Asia Pacific Conference on Circuits and Systems (APCCAS), 2023.