# Variability Reduction with Bilayer RRAM Device

Tim Kempen<sup>1</sup>, Ankit Bende<sup>1</sup>, Alexandros Sarantopoulos<sup>1</sup>, Regina Dittmann<sup>1,2</sup>, Christopher Bengel<sup>2</sup>, André Zambanini<sup>3</sup>, Dennis Nielinger<sup>3</sup>, Stephan Menzel<sup>1</sup>, Vikas Rana<sup>1</sup>

<sup>1</sup>Peter Grünberg Institute 7 & 10, Forschungszentrum Jülich GmbH

<sup>2</sup>IWE-2 RWTH Aachen, Germany

<sup>3</sup>ZEA-2, Forschungszentrum Jülich GmbH

Abstract—The inherent stochastic behavior of filamentary switching introduces significant cycle-tocycle (C2C) fluctuations in the device characteristics, which poses a challenge to the practical applications of resistive random-access memories (RRAMs). Here, we report a simple bilayer oxide-based device structure of TaOx/HfO2 on a 180-nm CMOS substrate to address this variability issue and improve the overall performance of the memory device. The improved switching variability in the bilayer stack is attributed to the incorporation of a conductive TaOx thin film, which serves as the switching layer after the conductive filament formation in HfO2. More specifically, the switching happens at the interface between the conductive filament and TaOx and exhibits a more gradual and less stochastic behavior than filamentary switching. As a result, 3-bit multi-level nonoverlapping switching can be demonstrated in TaO<sub>x</sub>/HfO<sub>2</sub> bilayer RRAM devices. These findings could be crucial for the high density data storage applications

## Keywords—Bilayer RRAM, Variability, 3-Bit MLC

#### I. INTRODUCTION

Resistive random-access memory (RRAM) is considered a promising technology for the next generation of non-volatile memory (NVM) and neuromorphic computing applications due to its simple metal-insulator-metal (MIM) device geometry that possesses high speed operation, low power consumption, and excellent scalability [1-3]. Though the resistive switching phenomena has been observed in various dielectrics, simple binary metal oxides, namely, TiOx, HfOx, and TaOx, etc., have been found to be more promising [4-6]. Within the realm of binary metal oxides, TaO<sub>x</sub> and HfO<sub>x</sub>-based devices have garnered significant attention, primarily due to their exceptional device performance, ease of fabrication, and compatibility with semiconductor (CMOS) process technology [7-8].

The filamentary resistive switching effect is generally driven by the growth and rupture of conductive filaments (CFs) within the switching oxide film. Particularly, the filaments in oxide-based RS devices are composed of a highly oxygen-deficient region. However, the size, shape, and location of these CFs inside the switching layer are completely stochastic, which, in turn, induces cycle-to-cycle (C2C) and device-to-device (D2D) variability in RRAMs [9]. This poses a major challenge for the commercialization of RRAM technology. Several strategies have been proposed to overcome this critical issue such as impurity doping, insertion of nanoparticles, and

interface engineering [10-12]. In this work, we report a simple and practical approach for achieving low variability resistive switching operation in TaO<sub>x</sub>/HfO<sub>2</sub> bilayer devices with 3-bit multilevel storage capability fabricated by physical vapor deposition technique. The stoichiometry and resistivity of the conductive TaO<sub>x</sub> thin film is tailored by the oxygen flow rate during the sputtering deposition. In HfO2-based RRAM devices utilizing a conductive metal oxide (CMO), such as TaO<sub>x</sub> in the bilayer devices, a gradual SET transition in clockwise switching direction is observed [13]. After the CF is formed in the HfO2-layer of CMO/HfO2based RRAM, the resistive switching happens within the CMO, specifically at the CMO/CF interface [14]. Since this type of resistive switching is less stochastic than filamentary switching, a gradual SET transition and a lower variability can be obtained. Hence, the bilayer device (TaO<sub>x</sub>/HfO<sub>2</sub>) structure considerably improves the C2C variability during the switching. The C2C variability is further compared with single switching oxide (W/Ta<sub>2</sub>O<sub>5</sub>) RRAM.

The multi-level cell (MLC) operation can be achieved either by varying the current compliance ( $I_{\rm CC}$ ) during the SET process or changing the RESET stop voltages during the RESET process [15, 16]. A precise control over multiple resistance states is obtained by using different  $I_{\rm CC}$ . By varying the  $I_{\rm CC}$  during the SET process, 8 distinct and reproducible resistance states are achieved for the bilayer RRAM devices.

## II. DEVICE FABRICATION

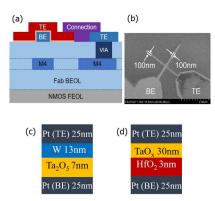

For this study, 100 x 100 nm<sup>2</sup> RRAM devices were fabricated on a 180-nm CMOS substrate. On the processed substrate, which was designed and fabricated in collaboration with X-FAB, single 1T-1R structures as well as 1T-1R arrays of different dimensions can be found. All results shown in this work originate from single 1T-1R devices. The cross section schematic of the integrated 1T-1R device is shown in Fig. 1. After exposing the W-plug, a 25-nmthick Pt layer, serving as bottom electrode is deposited on the CMOS substrate with DC sputtering process. This layer is eventually patterned by electron beam lithography, followed by back etching using reactive ion etching (RIE). Subsequently, for single layer RRAM, a 7-nm-thick TaO<sub>X</sub> layer was deposited by RF-sputtering Ar (77%) and O<sub>2</sub> (23%) gas mixture at 236 W RF power followed by deposition of 13-nmthick W through DC sputtering using Ar gas without breaking the vacuum. The bilayer RRAM stack was also deposited in the similar process consisting of 3nm-thick HfO<sub>2</sub> layer by RF sputtering using Ar (60%) and O<sub>2</sub> (40%) gas mixture at 200 W RF power followed by RF sputtering of 30-nm-thick TaOx using Ar (99%) and O<sub>2</sub>(1%) at 85 W RF power. The oxygen-deficient TaO<sub>x</sub> thin-film in the bilayer stack exhibits a high electrical conductivity. Next, a 25-nm-thick Pt top electrode (TE) was deposited using DC sputtering on both samples. Finally, the switching oxide and TE stack were patterned and etched using electron beam lithography and RIE, respectively. Figure 1 shows the SEM image of the 100 x 100 nm<sup>2</sup> crossbar device fabricated on the CMOS substrate in 1T-1R configuration. In this configuration, an NMOS transistor serves as a current limiter for the RRAM device.

Fig. 1. Cross-sectional schematic diagram of RRAM device integrated on a 180-nm CMOS substrate, leaving out the lower metal layers for better visibility (a) and the SEM image of 100 x 100 nm² nano-crossbar RRAM device fabricated on the CMOS substrate (b). (c), (d) Both RRAM device stacks are shown with respective thickness of the layer. Additionally, the top electrode (TE) and bottom electrode (BE) assignment for the electrical characterization is displayed.

# III. RESULT AND DISCUSSION

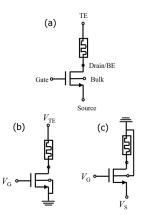

The electrical characterizations of the 1T-1R structures were carried out using Keithley 4200 SCS. Figure 2 (a) shows the layout of the 1T-1R structure used for electrical measurements. Measurements applied to the RRAM TE (e.g. electroforming) are assigned a positive polarity in all following figures showing current-voltage (I-V) characteristics, while measurements applied to the transistor source (e.g. RESET) are assigned a negative polarity. The voltages applied to the 1T-1R structure in both configurations are displayed in the schematics in Figs. 2(b) & (c). In both configurations, a voltage sweep is either applied at the TE or Source terminal while keeping the Source or TE and the Bulk terminal at ground level. The applied Gate voltage (V<sub>G</sub>=const.) determines the compliance current ( $I_{CC}$ ).

Figure 3 shows the the median value of the forming voltage for the single layer (W/Ta<sub>2</sub>O<sub>5</sub>) and the bilayer stacks (TaO<sub>x</sub>/HfO<sub>2</sub>). For each type, 25-39 devices were measured. Figure 3(b) shows the cumulative probability of the forming voltage, indicating a lower variability of the forming voltage for the bilayer  $TaO_x/HfO_2$  devices.

Fig.2 (a) Schematic diagram of electrical setup for 1T-1R device, including transistor and RRAM terminals. The RRAM BE is connected to the transistor Drain terminal. (b) Configuration for positive voltage sweeps (applied to the TE). (c) Configuration for negative voltage sweeps (applied to the Source).

Fig. 3 (a) Median Forming I-V characteristics and (b) Cumulative distribution function of the forming voltage for single layer  $TaO_x/W$  and bilayer  $TaO_x/HfO_2$  RRAM. 25-39 devices were measured for each case.

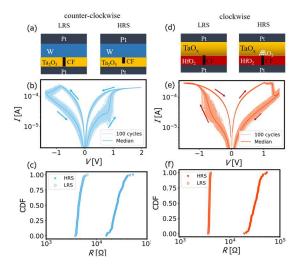

Figure 4 shows the *I-V* characteristics of the single layer W/Ta<sub>2</sub>O<sub>5</sub> and bilayer TaO<sub>x</sub>/HfO<sub>2</sub> RRAM in 1T-1R configuration for 100 cycles. It should be noted that the single layer W/Ta<sub>2</sub>O<sub>5</sub> devices show counterclockwise switching, whereas the bilayer TaO<sub>x</sub>/HfO<sub>2</sub> devices show clockwise switching, which is happening within the TaO<sub>x</sub> at the TaO<sub>x</sub>/CF interface [13, 14]. Figures 4 (a) and (d) graphically display the switching mechanisms for single layer (counter-clockwise) and bilayer devices (clockwise), respectively. Counterclockwise switching in single layer W/Ta<sub>2</sub>O<sub>5</sub> devices is based on rupture/reconnection of the CF (Figure 4 (a)). As suggested by [13, 14], a dome-shaped region above the CF might result in the observed clockwise switching in bilayer TaO<sub>x</sub>/HfO<sub>2</sub> devices, as illustrated in Fig. 4(d). In these works, the device properties enabling clockwise switching in TaO<sub>x</sub>/HfO<sub>2</sub>-based RRAM devices are discussed in more detail. Figures 4(c) and (f) show the cumulative probability of LRS and HRS for both type of devices. It is evident that the bilayer TaO<sub>x</sub>/HfO<sub>2</sub> RRAM device shows lower C2C variability than its counterpart: the W/Ta<sub>2</sub>O<sub>5</sub> stack. The coefficient of variation (CoV) for C2C switching is shown in Table 1. The CoV for LRS and HRS is calculated by dividing the standard deviation (StD) by the mean value of the distribution. For both LRS and

HRS, the bilayer (TaO<sub>x</sub>/HfO<sub>2</sub>) RRAM devices show the lower C2C variation.

Fig. 4. Schematics illustrating the difference between LRS and HRS configuration for (a) counter-clockwise switching direction and (d) clockwise switching direction. (b), (c) I-V characteristics and cumulative probability of single layer W/Ta<sub>2</sub>O<sub>5</sub> RRAM devices;  $V_{\text{SET,stop}} = V_{\text{TE}} = 2 \text{ V}$ ,  $V_{\text{gate,SET}} = 1.2 \text{ V}$ ,  $V_{\text{RESET,stop}} = V_{\text{Source}} = 1.3 \text{ V}$ ,  $V_{\text{gate,RESET}} = 4 \text{ V}$ . (e), (f) I-V characteristics and cumulative probability of bilayer TaO<sub>x</sub>/HfO<sub>2</sub> RRAM devices;  $V_{\text{SET,stop}} = V_{\text{Source}} = 1.5 \text{ V}$ ,  $V_{\text{gate,RESET}} = 4 \text{ V}$  Each type of device was measured for 100 cycles. HRS and LRS values are extracted from the I-V characteristic of each cycle.

The lower variability in the bilayer (TaO<sub>x</sub>/HfO<sub>2</sub>) devices can be attributed to the fact that the switching process in these bilayer devices takes place at the TaO<sub>x</sub>/CF interface. This type of switching exhibits a reduced non-linearity in the switching kinetics [14] compared to the kinetics of purely filamentary switching happening in single layer devices. As a result of the reduced non-linearity in the switching kinetics, a lower stochasticity in the resistance states (HRS & LRS) is observed in the bilayer devices.

Table 1. Coefficient of variation (CoV) for C2C switching variability. CoV = StD/Mean.

| RRAM device                                    | CoV HRS | CoV LRS | Off/On |

|------------------------------------------------|---------|---------|--------|

| Single layer, W/Ta <sub>2</sub> O <sub>5</sub> | 0.34    | 0.14    | 7.43   |

| Bilayer, TaO <sub>x</sub> /HfO <sub>2</sub>    | 0.30    | 0.080   | 6.53   |

## IV. 3-BIT MULTILEVEL SWITCHING

To achieve higher data density for storage applications in RRAMs is to enable more than two bits to be stored in a single RRAM device. Many authors have demonstrated 2-bit and 3-bit MLC in 1T-1R and passive crossbar arrays [17, 18] by using  $I_{\rm CC}$  control and varying  $V_{\rm RESET}$ .

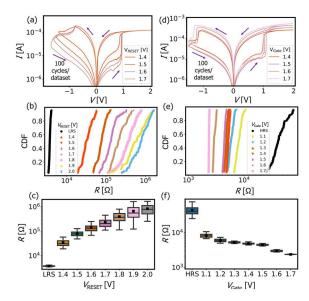

We have tested both types of RRAM devices with the  $I_{\rm CC}$  control and varying  $V_{\rm RESET}$ . The HRS and LRS values of each dataset in the 3-bit MLC operation are extracted from the I-V characteristics.

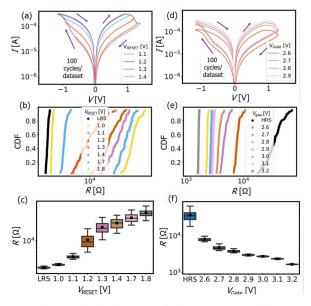

Fig. 5. 3-Bit MLC in single layer W/Ta<sub>2</sub>O<sub>5</sub> 1T-1R RRAM devices (a) median *I-V* characteristics, (b), (c) resistance state distributions for different  $V_{\text{RESET}}$ , switching parameters:  $V_{\text{SET,stop}} = V_{\text{TE}} = 2 \text{ V}$ ,  $V_{\text{gatc,SET}} = 1.2 \text{ V}$ ,  $V_{\text{RESET,stop}} = V_{\text{Source}}$  varies,  $V_{\text{gatc,RESET}} = 4 \text{ V}$ . 3-Bit MLC (d) median *I-V* characteristics, (e), (f) resistance state distributions for different  $I_{\text{CC}}$ , switching parameters:  $V_{\text{SET,stop}} = V_{\text{TE}} = 2 \text{ V}$ ,  $V_{\text{gatc,RESET}}$  varies,  $V_{\text{RESET,stop}} = V_{\text{Source}} = 1.3 \text{ V}$ ,  $V_{\text{gatc,RESET}} = 4 \text{ V}$ . The  $I_{\text{CC}}$  dependent MLC shows lower variability among the different resistance states.

Fig. 6. 3-Bit MLC in bilayer layer TaO<sub>x</sub>/HfO<sub>2</sub> 1T-1R RRAM devices (a) median I-V characteristics, (b) (c) resistance state distributions for different  $V_{\rm RESET}$ , switching parameters:  $V_{\rm SET,stop} = V_{\rm Source} = 1.5$  V,  $V_{\rm gate,SET} = 2.9$  V,  $V_{\rm RESET,stop} = V_{\rm TE}$  varies,  $V_{\rm gate,RESET} = 4$  V. 3-Bit MLC (d) median I-V characteristics, (e), (f) resistance state distributions for different  $I_{\rm CC}$ , switching parameters:  $V_{\rm SET,stop} = V_{\rm Source} = 1.5$  V,  $V_{\rm gate,RESET} = 4$  V. The  $I_{\rm CC}$  dependent MLC shows lower variability among the different resistance states.

Figure 5 shows the 3-bit MLC operation in single layer W/Ta<sub>2</sub>O<sub>5</sub> RRAM in 1T-1R configuration. Figures 5(a-c) & (d-f) show the MLC operation with varying the  $V_{\rm RESET}$  and different  $I_{\rm CC}$  control, respectively. It is evident that varying the  $V_{\rm RESET}$

introduces more variability than the  $I_{\rm CC}$  control method. As a result, an overlapping of different resistance states is observed for the varying the  $V_{\rm RESET}$  method. Figure 6 shows the 3-bit MLC operation in bilayer  ${\rm TaO_x/HfO_2}$  RRAM for 1T-1R configuration. Figures 6(a-c) & (d-f) show the MLC operation with varying the  $V_{\rm RESET}$  and different  $I_{\rm CC}$  control, respectively. Similar trends, i.e., a lower variability with the  $I_{\rm CC}$  control method is also observed in the bilayer RRAM devices.

When comparing the different RRAM device stacks for the varying  $V_{\rm RESET}$  method, a noticeable lower variability is observed for bilayer  ${\rm TaO_x/HfO_2}$  devices in comparison to single layer  ${\rm W/Ta_2O_5}$  RRAM devices. The CoV for both RRAM stacks are tabulated in Table 2.

Table 2. Comparison of maximum resistance state variability during 3-bit multilevel switching

| RRAM device                                   | CoV Icc | CoV Vreset |

|-----------------------------------------------|---------|------------|

| Single layer W/Ta <sub>2</sub> O <sub>5</sub> | ≤ 0.27  | ≤ 0.68     |

| Bilayer TaO <sub>x</sub> /HfO <sub>2</sub>    | ≤ 0.27  | ≤ 0.44     |

### V. CONCLUSIONS

In this study, we have integrated single layer W/Ta<sub>2</sub>O<sub>5</sub> and bilayer TaO<sub>x</sub>/HfO<sub>2</sub> RRAM on 180-nm CMOS substrates and demonstrated that C2C variability in the filamentary switching can be reduced by introducing the bilayer device stack. When compared to single layer W/Ta<sub>2</sub>O<sub>5</sub>, the bilayer RRAM shows lower variability (D2D) during the forming process but also lower C2C variability during the switching. As a result, we were able to demonstrate 3bit MLC operation with 8 distinct resistance states in the bilayer TaO<sub>x</sub>/HfO<sub>2</sub> RRAM devices. Multistate devices enable novel in-memory applications, e.g. ternary computation, in which the computational complexity as well as the number of devices is reduced compared to binary computation [17]. We believe that these results could pave a way for designing a high performing RRAM device stack for high data density applications.

## VI. ACKNOWLEDGEMENT

This work was supported by the BMBF, Germany, in the project NEUROTEC II under Project no. 16ME0398K and 16ME0399. Special thanks goes out to Dr. Michael Schiek for his management work in the NEUROTECH II project.

## REFERENCES

- [1] B. Rajendran et al., "Neuromorphic Computing Based on Emerging Memory Technologies," IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 6, no. 2. Institute of Electrical and Electronics Engineers Inc., pp. 198–211, Jun. 01, 2016. doi: 10.1109/JETCAS.2016.2533298.

- [2] R. Waser *et al.*, "Redox-based resistive switching memories nanoionic mechanisms, prospects, and

- challenges," *Advanced Materials*, vol. 21, no. 25–26. pp. 2632–2663, Jul. 13, 2009. doi: 10.1002/adma.200900375.

- [3] N. Verma et al., "In-memory computing advances and prospects," IEEE Solid-State Circuits Magazine, vol. 11, no. 3, pp. 43–55, 2019, doi: 10.1109/MSSC.2019.2922889.

- [4] F. Cüppers et al., "Exploiting the switching dynamics of HfO2-based ReRAM devices for reliable analog memristive behavior," APL Mater, vol. 7, no. 9, Sep. 2019, doi: 10.1063/1.5108654.

- [5] P. Bousoulas et al., "Investigating the origins of high multilevel resistive switching in forming free Ti/TiO<sub>2-x-</sub> based memory devices through experiments and simulations," J Appl Phys, vol. 121, no. 9, Mar. 2017, doi: 10.1063/1.4977063.

- [6] K. Szot et al., "TiO2 A prototypical memristive material," Nanotechnology, vol. 22, no. 25. Jun. 24, 2011. doi: 10.1088/0957-4484/22/25/254001.

- [7] G. Niu et al., "Geometric conductive filament confinement by nanotips for resistive switching of HfO<sub>2</sub>-RRAM devices with high performance," Sci Rep, vol. 6, May 2016, doi: 10.1038/srep25757.

- [8] D. Bhattacharjee, W. Kim et al., "Multi-valued and Fuzzy Logic Realization using TaO<sub>x</sub> Memristive Devices," Sci Rep, vol. 8, no. 1, Dec. 2018, doi: 10.1038/s41598-017-18329-3.

- [9] R. Degraeve et al., "Causes and consequences of the stochastic aspect of filamentary RRAM," Microelectron Eng, vol. 147, pp. 171–175, Nov. 2015, doi: 10.1016/j.mee.2015.04.025.

- [10] T. Kempen et al., "50x endurance improvement in TaOx RRAM by extrinsic doping," in 2021 IEEE International Memory Workshop, IMW 2021 - Proceedings, Institute of Electrical and Electronics Engineers Inc., May 2021. doi: 10.1109/IMW51353.2021.9439591.

- [11] S. P. Swathi and S. Angappane, "Low power multilevel resistive switching in titanium oxide-based RRAM devices by interface engineering," *Journal of Science: Advanced Materials and Devices*, vol. 6, no. 4, pp. 601–610, Dec. 2021, doi: 10.1016/j.jsamd.2021.08.002.

- [12] Y. Fang et al., "Improvement of HfO<sub>x</sub>-Based RRAM Device Variation by Inserting ALD TiN Buffer Layer," *IEEE Electron Device Letters*, vol. 39, no. 6, pp. 819–822, Jun. 2018, doi: 10.1109/LED.2018.2831698.

- [13] T. Stecconi et al., "Filamentary TaO<sub>x</sub>/HfO<sub>2</sub> ReRAM Devices for Neural Networks Training with Analog In-Memory Computing," Adv Electron Mater, vol. 8, no. 10, Oct. 2022, doi: 10.1002/aelm.202200448.

- [14] D. F. Falcone et al., "Physical modeling and design rules of analog Conductive Metal Oxide-HfO2 ReRAM," 2023 IEEE International Memory Workshop (IMW), Monterey, CA, USA,2023,pp.1-4, doi:10.1109/IMW56887.2023.10145936.

- [15] T. S. Lee et al., "Compliance Current-Controlled Conducting Filament Formation in Tantalum Oxide-Based RRAM Devices with Different Top Electrodes," ACS Appl Electron Mater, vol. 2, no. 4, pp. 1154–1161, Apr. 2020, doi: 10.1021/acsaelm.0c00128.

- [16] M. Ismail et al., "Stabilized and RESET-voltage controlled multi-level switching characteristics in ZrO<sub>2</sub>based memristors by inserting a-ZTO interface layer," J Alloys Compd, vol. 835, p. 155256, Sep. 2020, doi: 10.1016/j.jallcom.2020.155256.

- [17] W. Kim et al. Multistate Memristive Tantalum Oxide Devices for Ternary Arithmetic. Sci Rep 6, 36652 (2016). https://doi.org/10.1038/srep36652.

- [18] J. -H. Yoon et al., "A 40-nm 118.44-TOPS/W Voltage-Sensing Compute-in-Memory RRAM Macro With Write Verification and Multi-Bit Encoding," in *IEEE Journal of Solid-State Circuits*, vol. 57, no. 3, pp. 845-857, March 2022, doi: 10.1109/JSSC.2022.3141370.