# A Cryogenic Voltage Regulator with Integrated Voltage Reference in 22 nm FDSOI Technology

A. R. Cabrera-Galicia \*, A. Ashok \*, P. Vliex \*, A. Kruth \*, A. Zambanini \*, S. van Waasen \*<sup>†</sup>

\* Central Institute of Engineering, Electronics and Analytics, Electronics Systems (ZEA-2),

Forschungszentrum Jülich GmbH, 52428 Jülich, Germany

Email: {a.cabrera.galicia, a.ashok, p.vliex, a.kruth, a.zambanini, s.van.waasen }@fz-juelich.de

† Faculty of Engineering, Communication Systems, University Duisburg-Essen, 47057 Duisburg, Germany

Abstract—High performance ICs (Integrated Circuits) operating at cryogenic temperatures will be a fundamental part of future quantum computers, providing precise manipulation of a large number of qubits [1], [2]. However, these ICs will need regulated and stable supply voltages in situ for optimum operation due to their mixed signal nature [3], [4]. Accordingly, this paper presents the design and cryogenic electrical characterization of a voltage regulator with an integrated voltage reference. Together, the circuits can generate a regulated voltage of 1.15 V with up to 10 mA of output current capability at 6 K. The investigated circuits exploit two cryogenic MOS transistor phenomena, the threshold voltage ( $V_{\rm th}$ ) saturation and the transconductance ( $g_m$ ) increase. The circuits were developed in 22 nm FDSOI technology.

Index Terms—CMOS, fully depleted silicon-on-insulator (FDSOI), cryogenics, voltage reference, voltage regulator, quantum computing.

# I. INTRODUCTION

The use of quantum physics phenomena at cryogenic temperatures, via the manipulation of a large number of qubits performed by a Quantum Computer (QC), promises to speed up the finding of solutions to computational challenges faced in drug design, cryptography and logistics. In addition, it has been demonstrated that ICs (Integrated Circuits) will be an important part of such a system and its scalability [1], [2]. However, the ICs belonging to a QC need a stable and defined supply voltage for proper operation due to their mixed signal nature [3], [4]; e.g. the phase noise of RF oscillators is highly dependent on their power supply quality [5]. This need will be challenging to satisfy in a large scale QC since the supply signals, going from the supply sources in the lab to the ICs inside the cryostat, are prone to supply voltage ripples, ground loops, electromagnetic interference from neighboring lines and dynamic load currents. A potential solution to this problem is the use of low noise supply sources with four-terminal sensing capability. However, this approach will not be practical in large scale QCs, where the number of interface connections between the lab equipment and the cryostat coldest area will be important assets. Alternatively, a regulated voltage could be generated inside the cryostat and be used to supply the ICs of the QC, while maintaining the power integrity of the system.

Hence, this paper presents the design and cryogenic electrical characterization of a voltage regulator and an integrated voltage reference that together can produce a regulated voltage

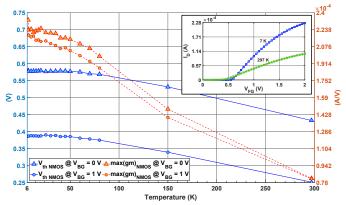

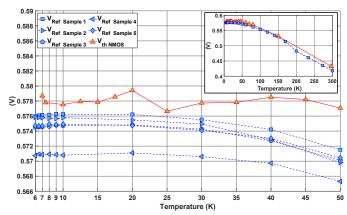

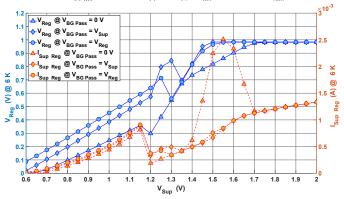

Fig. 1.  $V_{\rm th}$  and maximum  $g_m$  of I/O NMOS ( $W=1\,{\rm \mu m},~L=0.32\,{\rm \mu m})$  measured over temperature. Inset displays the  $I_{\rm D}$  versus  $V_{\rm FG}$  curve for 297 K and 7 K, at  $V_{\rm DS}=0.1\,{\rm V}$  and  $V_{\rm BG}=0\,{\rm V}$ .

at 6 K. Both circuits exploit two cryogenic MOS transistor phenomena, the threshold voltage  $(V_{\rm th})$  saturation and the transconductance  $(g_m)$  increase. The circuits have a verified operating range from 6 K to 50 K and were developed in a  $22\,\mathrm{nm}$  FDSOI technology.

# II. CRYOGENIC $V_{\text{th}}$ SATURATION AND $g_m$ INCREASE

As part of the circuit design methodology, an I/O NMOS transistor ( $W=1\,\mu\mathrm{m},\,L=0.32\,\mu\mathrm{m}$ ) was characterized versus temperature; details on the cryogenic DC characterization are reported in [6]. The circuits in this paper employ I/O transistors due to their higher voltage driving capability, in contrast to core transistors. For the device under test, Fig. 1 shows the evolution of its  $V_{\mathrm{th}}$  and maximum  $g_m$  along temperature.

As expected, the device  $V_{\rm th}$  increases with temperature reduction [7], [8]. However,  $V_{\rm th}$  saturation starts at 60 K, with an average value of  $578\,\mathrm{mV}$ . This phenomenon also occurs when the back gate of the device is set to 1 V, with a  $V_{\rm th}$  saturation of  $387\,\mathrm{mV}$ . The cryogenic  $V_{\rm th}$  increase and saturation is attributed by [9] to the ionization energy increase and the carrier freezeout. Furthermore, [10] argues that the cryogenic  $V_{\rm th}$  behavior is due to the temperature dependence of the bulk Fermi potential and the density of interface traps. The  $V_{\rm th}$  saturation has been reported for other technologies, among them a commercial  $28\,\mathrm{nm}$  bulk CMOS technology [10]. While the cryogenic  $V_{\rm th}$  saturation on  $22\,\mathrm{nm}$  FDSOI technology is reported in [11], to the best of the authors knowledge, it has not being utilized

for the design of cryogenic analog circuits. Regarding the device  $g_m$ , its maximum value increases by 184% at  $7 \, \mathrm{K}$ , compared to  $297 \, \mathrm{K}$ . A similar situation occurs when the device back gate is set to  $1 \, \mathrm{V}$ , but with a slight reduction of the  $g_m$  maximum value. The  $g_m$  increase at cryogenic temperatures is linked to the carriers mobility increase due to reduced phonon scattering; a phenomenon expected in NMOS and PMOS devices [10], [11].

### III. CIRCUIT DESIGN AND ELECTRICAL EVALUATION

## A. Voltage Reference

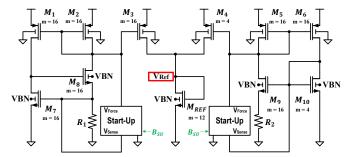

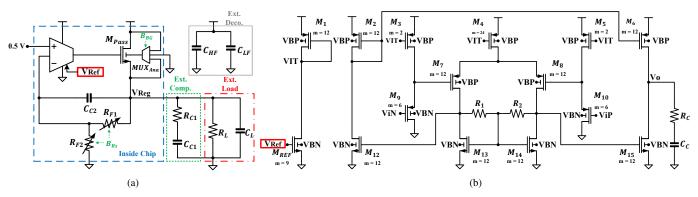

Cryogenic  $V_{\rm th}$  saturation is employed as working principle by the voltage reference circuit shown in Fig. 2. The circuit is composed of beta-multiplier and self-bias  $V_{\rm GS}$  current sources, that together bias a diode connected NMOS device to yield the reference voltage  $(V_{\text{Ref}})$ . The voltage reference circuit is simple and does not employ post-fabrication techniques to improve its  $V_{\text{\tiny Ref}}$  drift over temperature. It relies on the fact that a constant current biases and saturates the diode connected NMOS  $(M_{\text{REF}})$ , while the circuit is operated inside the  $V_{\text{th}}$ saturation temperature region. This is a common situation for ICs intended to be used in large scale QCs, since they are placed close to the physical quantum bits at environmental temperatures between 10 K and 4 K. Although self-heating is a concern at cryogenic temperatures, its effect is also proportional to the electrical power dissipated by the devices [12], [13]. Due to its low power dissipation, estimated to be 70 μW during the circuit design flow, a negligible self-heating is expected from this reference. Additionally, start-up circuits are used to prevent the current sources from latch-up. They can either operate autonomously or be manually triggered through configuration bits set via a JTAG interface.

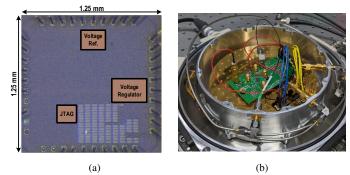

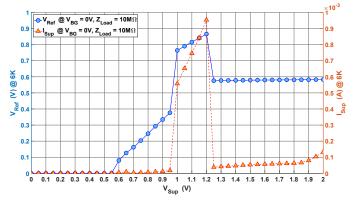

A prototype chip micrograph is shown in Fig. 3(a); the voltage reference, voltage regulator and JTAG interface are included in the chip. The cryogenic experimental setup is displayed in Fig. 3(b). Inside it, prototype chips are mounted on PCBs specially designed for good thermal coupling with the cryostat cold head. In order to measure and control the PCB temperature, a sensing diode is attached to the PCB and monitored during the electrical tests. Due to the cryostat cooling power limitation, the lowest PCB temperature is 6 K. The measured response from a prototype reference circuit to a supply voltage  $(V_{Sup})$  sweep is shown in Fig. 4 at 6 K. In specific, the output voltage  $(V_{\mathrm{Ref}})$  and supply current consumption  $(I_{Sup})$ , indicating that the circuit starts operating at  $V_{Sup}$  =  $1.25\,\mathrm{V}$  with  $V_\mathrm{Ref}$  =  $576\,\mathrm{mV}$  and  $I_\mathrm{Sup}$  =  $38.3\,\mu\mathrm{A}$ . Fig.5 shows the measured  $V_{\text{Ref}}$  over temperature, together with the  $V_{\text{th}}$  extracted from the I/O NMOS (Section II). As can be observed,  $V_{\mathrm{Ref}}$ from sample 1 follows a trend similar to the one of the I/O NMOS  $V_{\text{th}}$  and deviates on average by  $2.5\,\text{mV}$  from it at temperatures between 6 K to 50 K. In total, 5 ICs containing a reference circuit were tested. The responses of these samples are shown in Fig. 5 and they differ slightly between each other, but all follow the I/O NMOS  $V_{\rm th}$  trend over temperature. These measurements demonstrate the prototype reference practicality at environmental temperatures between 50 K and 6 K.

Fig. 2. Voltage reference based on cryogenic  $V_{\rm th}$  saturation.

Fig. 3. (a) Micrograph of a prototype chip. (b) Experimental setup: PCB with prototype chip, mounted onto the cryostat cold head.

Fig. 4. Measured output voltage and current consumption of voltage reference (sample 1) with respect to supply voltage  $(V_{\text{S}_{nm}})$ , at  $6\,\mathrm{K}$ .

Fig. 5. Measured output from voltage reference over the temperature range of interest (6 K to 50 K), with  $V_{\rm Sup}=1.25\,{\rm V}$  and  $V_{\rm BG}=0\,{\rm V}$ ; results correspond to 5 sample chips. Extracted  $V_{\rm th}$  from I/O NMOS ( $W=1\,{\rm \mu m}, L=0.32\,{\rm \mu m}$ ) is added for comparison. Inset displays sample 1 data over a wider temperature range (6 K to 300 K).

Fig. 6. Cryogenic voltage regulator. (a) The regulator is composed of an error amplifier, an NMOS pass element, a multiplexer and a resistive feedback network. Off-chip compensation elements (metal film based  $R_{C1}$  and polyphenylene-sulphide based  $C_{C1}$ ), with stable electrical characteristics over temperature, are used to guarantee stability at cryogenic temperatures. (b) Differential amplifier used by regulator; its tail current is biased by cryogenic reference (Fig. 2).

## B. Voltage Regulator

A circuit diagram describing the voltage regulator, designed for cryogenic temperatures, is shown in Fig.6(a). The regulator employs an NMOS pass element whose back-gate terminal connection can be shifted through an analog multiplexer controlled via JTAG. In this way it is possible to compensate for the  $V_{\rm th}$  increase experienced by the pass element at cryogenic temperatures and to reduce the supply voltage level required by the regulator to start its operation; threshold voltage tuning via the back-gate terminal is a characteristic offered by FDSOI MOS devices [14]. Although the use of an NMOS pass element will lead to a higher dropout voltage in contrast to a PMOS, it will also provide a superior power supply rejection ratio (PSRR); a requirement needed to supply high performance analog circuits [5], [15]. Additionally, the feedback resistors values  $(R_{\rm Fl} \ {\rm and} \ R_{\rm E2})$  can be modified for output voltage tuning via JTAG programming. Moreover, a cryogenic-stable off-chip compensation network, made up of a metal film resistor ( $R_{\rm Cl}=6.25\,\Omega$ ) and a polyphenylene-sulphide film capacitor ( $C_{\rm Cl}=47\,{\rm nF}$ ), guarantees the regulator stability at cryogenic temperatures [4].

The differential amplifier of the regulator, shown in Fig.6(b), employs voltage followers for level shifting at their inputs and resistive local common mode feedback at its core; its open loop gain  $(A_{DA})$  is approximated by Eq. 1 [16]. Since the regulator loop gain  $(A_{\rm LG})$  is proportional to  $A_{\rm DA}$  (Eq. 2), the load regulation (LR) and PSRR are also depending on  $A_{\scriptscriptstyle {

m DA}}$  via  $A_{\rm LG}$  (Eq. 3 and 4) [15]. As  $A_{\rm DA}$  is proportional to the  $g_m$  of the MOS devices, it is expected that at cryogenic temperatures its magnitude increases due to the  $g_m$  increase with temperature reduction (Section II), resulting in an improvement of the regulator LR and PSRR.

$$A_{\rm DA} \ \approx \ g_{m_{7,8}} \cdot (R_{_{1,2}} || r_{o_{7,8}} || r_{o_{13,14}}) \cdot g_{m_{12,15}} \cdot Z_{\rm out} \ (1)$$

$$A_{\text{LG}} \approx A_{\text{DA}} \cdot \frac{R_{\text{F2}}}{R_{\text{PL}} + R_{\text{PR}}}$$

(2)

$$LR \approx \frac{1}{a + A} \tag{3}$$

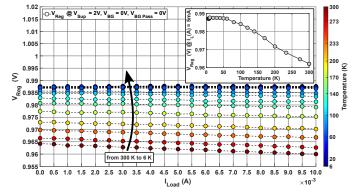

Fig. 7. Measured regulator output voltage ( $V_{\rm Reg}$ ) in relation to  $I_{\rm Load}$  and temperature, at  $V_{\rm IN\,Ref}=0.5\,{\rm V}$ ,  $R_{\rm F1}=R_{\rm F2}$ ,  $V_{\rm BG}=0\,{\rm V}$  and  $V_{\rm Sup}=2\,{\rm V}$ . Inset displays the measured  $V_{\rm Reg}$  at  $I_{\rm Load}=5\,{\rm mA}$ , between  $300\,{\rm K}$  and  $6\,{\rm K}$ .

Fig. 7 shows the measured response of the prototype regulator in relation to load current  $(I_{\rm Load})$  and temperature, with  $V_{

m IN\,Ref}=0.5\,{

m V}$  ,  $R_{

m FI}=R_{

m F2}$  ,  $V_{

m BG}=0\,{

m V}$  and  $V_{

m Sup}=2\,{

m V}$ .  $V_{

m IN\,Ref}$  is set to  $0.5\,{

m V}$  by means of an external voltage source in order to evaluate the regulator performance in regard to temperature. The mean regulator output voltage  $(V_{\text{Reg}})$  is  $962\,\text{mV}$  at  $300\,\text{K}$ and it increases to 987 mV at 6 K. These changes signal to an increase in  $A_{\rm LG}$  that reduces the regulator error and sets  $V_{\text{\tiny Reg}}$  closer to 1 V, the ideal output value; due to the amplifier input offset voltage,  $V_{\text{Reg}} \neq 1\,\text{V}$ . Similarly, the regulator LR changes from  $424\,\mathrm{mV/A}$  at  $300\,\mathrm{K}$ , to  $30\,\mathrm{mV/A}$  at  $6\,\mathrm{K}$ ; an improvement in the form of a 92.92 % decrease.

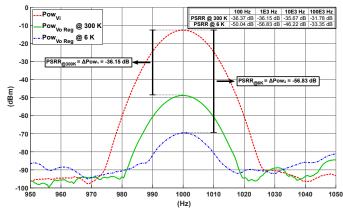

The regulator PSRR is shown in Fig. 8 for 1 kHz, at 300 K and 6 K. At 300 K, the measured PSRR is  $-36.15 \,\mathrm{dB}$ , while at  $6\,\mathrm{K}$  it is  $-56.83\,\mathrm{dB}$ , corresponding to an improvement of 20.68 dB. The inset in Fig. 8 indicates the measured PSRR for additional frequencies. Based on the measurements previously described and Eq. (1) - (4), it can be inferred that the  $g_m$ increase is the main factor for the cryogenic improvement of the regulator LR and PSRR. Furthermore, Fig. 9 shows the regulator response to a voltage supply sweep at 6 K, with different pass element back-gate configurations. With the backgate set to ground, the regulator needs  $V_{\rm Sup} = 1.75\,{\rm V}$  to start operation. In contrast, by setting the back-gate to the supply rail, the regulator needs  $V_{\rm Sup} = 1.5\,{\rm V}$  to operate. A reduction of 250 mV is obtained. The regulator has an idle

Fig. 8. Measured regulator PSRR via spectrum analysis at 1 kHz, for 300 K and 6 K, with  $V_{\rm N_Ref}=0.5\,\rm V$ ,  $R_{\rm Fl}=R_{\rm F2}$ ,  $V_{\rm RG}=0\,\rm V$  and  $V_{\rm Sun}=2\,\rm V$ .

Fig. 9. Measured regulator output voltage  $(V_{\rm Reg})$  and supply current  $(I_{\rm Sup\ Reg})$  in relation to supply voltage  $(V_{\rm Sup})$  and several back gate settings for the NMOS pass element, at  $6~{\rm K}$ .

power consumption of  $3.3\,\mathrm{mW}$ , produced by the enforced operation of the pass element in saturation due to cryogenic stability concerns. An improvement on power consumption can be attained by incorporating cryogenic simulation models into the regulator design flow. Unfortunately, cryogenic simulation models were not available for the development of the prototype chip presented in this paper. Despite this, the regulator is able to operate at temperatures between  $300\,\mathrm{K}$  and  $6\,\mathrm{K}$ .

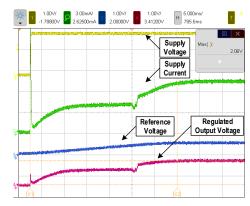

# C. Unified System for Cryogenic Voltage Regulation

Once verified the cryogenic characteristics of the reference and regulator circuits, their unified operation for voltage regulation is evaluated at  $6\,\mathrm{K}$  with  $V_{\mathrm{IN\,Ref}}=V_{\mathrm{Ref}}=576\,\mathrm{mV},$   $V_{\mathrm{Sup}}=2\,\mathrm{V},~V_{\mathrm{BG}}=V_{\mathrm{Sup}}$ ,  $R_{\mathrm{Fl}}=R_{\mathrm{F2}}$  and  $Z_{\mathrm{Load}}=220\,\Omega;$  one supply rail biases both circuits. The transient response measured from the system to a supply voltage pulse is shown in Fig. 10 and it is stable. The system delivers the regulated output voltage after  $27\,\mathrm{ms}$  due to slow response from the voltage reference circuit. Under static supply conditions,  $V_{\mathrm{Reg}}=1.15\,\mathrm{V}$  and  $I_{\mathrm{Sup}}=6.54\,\mathrm{mA}.$  The measured LR of the system is  $320\,\mathrm{mV/A},$  a value bigger than the result presented in Section III-B for  $6\,\mathrm{K},$  due to  $V_{\mathrm{IN\,Ref}}\neq0.5\,\mathrm{V}.$

## IV. CONCLUSIONS

The design and cryogenic characterization of a voltage reference and a voltage regulator, is reported in  $22\,\mathrm{nm}$  FDSOI.

Fig. 10. Measured transient response from the unified system for voltage regulation to a supply pulse with  $2\,\mathrm{V}$  amplitude, at  $6\,\mathrm{K}$ .

TABLE I Voltage reference comparison with state of the art.

|                         | Najafizadeh, et al.,<br>EDL, 2009 | Homulle, et al.,<br>SSCL, 2018 | van Stave<br>ESSCIR   | . , ,                 | Voltage Reference<br>in this work                    |

|-------------------------|-----------------------------------|--------------------------------|-----------------------|-----------------------|------------------------------------------------------|

| Technology              | SiGe BiCMOS                       | 40 nm CMOS                     | 40 nm CMOS            |                       | 22 nm FDSOI                                          |

| Reference Device        | SiGe HBT                          | Thick oxide DTMOS              | PMOS                  | DTMOS                 | NMOS                                                 |

| Operative Temp. Range   | 0.7 K – 293 K                     | 4 K – 300 K                    | 4 K – 300 K           | 4 K – 300 K           | 6 K – 50 K                                           |

| VSup min.               | 3.3 V                             | 1.8 V                          | 0.97 V                | 0.9 V                 | 1.25 V                                               |

| VRef                    | 1.156 V @ 0.7 mK                  | 0.81 V @ 4 K                   | 0.71 V @ 4 K          | 0.6 V @ 4 K           | 0.576 V @ 6 K                                        |

| Power Consumption       | 130.35 µW                         | 132 µW                         | 7.37 µW               | 7. 26 µW              | 47.88 μW                                             |

| Line Regulation         | Not provided                      | 8.3 %/V                        | 1.2 %/V               | 1.1 %/V               | 1.652 %/V<br>@ ZLOAD = 10MΩ,<br>VSup = [1.25 V, 2 V] |

| Temperature Coefficient | 160 ppm/K                         | 834 ppm/K                      | 539 ppm/K             | 436 ppm/K             | 300 ppm/K<br>@ Temp = [6 K, 50 K]                    |

| PSRR                    | Not provided                      | -23.4 dB<br>@ 4 K              | Not provided          | Not provided          | -46.14 dB<br>@ 6K, 1 kHz                             |

| Area                    | Not provided                      | 0.0004 mm <sup>2</sup>         | 0.009 mm <sup>2</sup> | 0.009 mm <sup>2</sup> | 0.006 mm <sup>2</sup>                                |

TABLE II Voltage regulator comparison with state of the art.

|                           | Homuli<br>Cryogen                                      | Voltage Regulator<br>in this work                       |                                                                           |  |

|---------------------------|--------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------|--|

| Technology                | Discrete compon                                        | ents based design                                       | 22 nm FDSOI                                                               |  |

| Pass Element              | NMOS (1                                                | TSM2314)                                                | NMOS                                                                      |  |

| Nominal VSup              | VDD = 3.3 V<br>VIN = 1.5 V (                           | 2 V                                                     |                                                                           |  |

| Error Amp.                | AD8605                                                 | TLV271                                                  | Custom                                                                    |  |

| VReg                      | 1.0086 V @4 K,<br>VREF = 0.6 V, ZLOAD = 100Ω           | 1.0106 V @4 K,<br>VREF = 0.6 V, ZLOAD = 100 Ω           | 0.987 V @6 K, VREF = 0.5 V,<br>VBGPass = 0V, ILOAD= 5mA                   |  |

| Idle Power<br>Consumption | 4.46 mW @4 K                                           | 0.1 mW @4 K                                             | 3.3 mW @6 K                                                               |  |

| Max. Load<br>Current      | 300 mA @4 K                                            | 300 mA @4 K                                             | 10 mA @6 K                                                                |  |

| Load<br>Regulation        | 1.59 mV/A @4 K,<br>ILOAD = [0 A, 300 mA]               | 0.81 mV/A @4 K,<br>ILOAD = [0 A, 300 mA]                | 22 mV/A @6 K, ILOAD = [0 A, 10mA],<br>VREF= 0.5 V, VBGPass=0V, VSup = 2 V |  |

| PSRR                      | -75.1 dB<br>@4 K, VREF = 0.6 V,<br>ZLOAD = 100Ω, 1 kHz | -76.4 dB<br>@4 K, VREF = 0.6 V,<br>ZLOAD = 100 Ω, 1 kHz | -56.83 dB<br>@6 K, VREF = 0.5 V,<br>VBGPass = 0V, VSup = 2 V, 1 kHz       |  |

| Area                      | Not provided                                           | Not provided                                            | 0.075 mm <sup>2</sup>                                                     |  |

| Build-in<br>VRegTuning    | No                                                     | No                                                      | Yes                                                                       |  |

The circuits make an effective use of the cryogenic  $V_{\rm th}$  saturation and  $g_m$  increase experienced by the MOS devices, as demonstrated in Section III. A comparison between the circuits in this paper and the state of the art is given in Tables I and II [4], [17], [18], [19]. The reference is simple and has a competitive temperature coefficient of  $300~{\rm ppm/K}$ , when operated between  $50~{\rm K}$  and  $6~{\rm K}$ . The regulator LR and PSRR fall behind the state of the art values. However, the regulator in this paper operate with lower  $V_{\rm sup}$  and, excluding the compensation network, its components are integrated on chip. Furthermore, with the circuits unified operation it is possible to generate a regulated voltage of  $1.15~{\rm V}$  at  $6~{\rm K}$  with

maximum output current capability of  $10\,\mathrm{mA}$ . Finally, the studied circuits served as exploration vehicles to gain insight into the design and electrical characterization of cryogenic analog integrated circuits, allowing the design of optimized cryogenic circuits in the future.

#### ACKNOWLEDGEMENT

The authors would like to thank Dr. Carsten Degenhardt for his useful discussions and comments. Furthermore, the authors thank the technical assistance from Christian Roth and Markus Harff on the electrical characterization of the ICs.

#### REFERENCES

- E. Charbon, F. Sebastiano, A. Vladimirescu, H. Homulle, S. Visser, L. Song, and R. M. Incandela, "Cryo-cmos for quantum computing," in 2016 IEEE International Electron Devices Meeting (IEDM), 2016, pp. 13.5.1–13.5.4.

- [2] B. Patra et al., "19.1 a scalable cryo-cmos 2-to-20ghz digitally intensive controller for 4×32 frequency multiplexed spin qubits/transmons in 22nm finfet technology for quantum computers," in 2020 IEEE ISSCC, 2020.

- [3] H. Homulle, S. Visser, B. Patra, and E. Charbon, "Design techniques for a stable operation of cryogenic field-programmable gate arrays," *Review of Scientific Instruments*, vol. 89, no. 1, p. 014703, 2018.

- [4] H. Homulle and E. Charbon, "Cryogenic low-dropout voltage regulators for stable low-temperature electronics," *Cryogenics*, vol. 95, 2018.

- [5] A. Urso, Y. Chen, J. F. Dijkhuis, Y.-H. Liu, M. Babaie, and W. A. Serdijn, "Analysis and design of power supply circuits for rf oscillators," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 67, no. 12, pp. 4233–4246, 2020.

- [6] A. R. Cabrera-Galicia, A. Ashok, P. Vliex, C. Degenhardt, A. Kruth, A. Artanov, and S. van Waasen, "Towards the development of cryogenic integrated power management units," in 2022 IEEE 15th Workshop on Low Temperature Electronics (WOLTE), 2022, pp. 1–4.

- [7] E. A. Gutierrez-D, J. Deen, and C. Claeys, Low temperature electronics: physics, devices, circuits, and applications. Elsevier, 2000.

- [8] A. Beckers, F. Jazaeri, H. Bohuslavskyi, L. Hutin, S. De Franceschi, and C. Enz, "Design-oriented modeling of 28 nm fdsoi cmos technology down to 4.2 k for quantum computing," in 2018 Joint International EU-ROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), 2018, pp. 1–4.

- [9] R. M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and compact modeling of nanometer cmos transistors at deep-cryogenic temperatures," *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 996–1006, 2018.

- [10] A. Beckers et al., "Physical model of low-temperature to cryogenic threshold voltage in mosfets," IEEE JEDS, vol. 8, 2020.

- [11] W. Chakraborty, K. A. Aabrar, J. Gomez, R. Saligram, A. Raychowd-hury, P. Fay, and S. Datta, "Characterization and modeling of 22 nm fdsoi cryogenic rf cmos," *IEEE Journal on Exploratory Solid-State Computational Devices and Circuits*, vol. 7, no. 2, pp. 184–192, 2021.

- [12] K. Triantopoulos et al., "Self-heating effect in fdsoi transistors down to cryogenic operation at 4.2 k," IEEE TED, vol. 66, no. 8, 2019.

- [13] A. A. Artanov et al., "Self-heating effect in a 65 nm mosfet at cryogenic temperatures," IEEE TED, vol. 69, no. 3, 2022.

- [14] R. Carter et al., "22nm fdsoi technology for emerging mobile, internetof-things, and rf applications," in 2016 IEEE IEDM, 2016.

- [15] B. Razavi, "The low dropout regulator [a circuit for all seasons]," *IEEE Solid-State Circuits Magazine*, vol. 11, no. 2, 2019.

- [16] J. Ramirez-Angulo and M. Holmes, "Simple technique using local cmfb to enhance slew rate and bandwidth of one-stage cmos op-amps," *Electronics Letters*, vol. 38, no. 23, 2002.

- [17] L. Najafizadeh, J. S. Adams, S. D. Phillips, K. A. Moen, J. D. Cressler, S. Aslam, T. R. Stevenson, and R. M. Meloy, "Sub-1-k operation of sige transistors and circuits," *IEEE Electron Device Letters*, vol. 30, no. 5, pp. 508–510, 2009.

- [18] H. Homulle, F. Sebastiano, and E. Charbon, "Deep-cryogenic voltage references in 40-nm cmos," *IEEE Solid-State Circuits Letters*, vol. 1, no. 5, pp. 110–113, 2018.

[19] J. van Staveren, C. García Almudever, G. Scappucci, M. Veldhorst, M. Babaie, E. Charbon, and F. Sebastiano, "Voltage references for the ultra-wide temperature range from 4.2k to 300k in 40-nm cmos," in ESSCIRC 2019 - IEEE 45th European Solid State Circuits Conference (ESSCIRC), 2019, pp. 37–40.