## **Evaluation of Cryogenic Models for FDSOI CMOS Transistors**

P. Chava<sup>1</sup>, H. Alius<sup>2</sup>, J. Bühler<sup>1</sup>, A. R. Cabrera-Galicia<sup>1</sup>, C. Degenhardt<sup>1</sup>, T. Gneiting<sup>2</sup>, M. Harff<sup>1</sup>, T. Heide<sup>3</sup>, P. Javorka<sup>4</sup>, M. Lederer<sup>5</sup>, S. Lehmann<sup>4</sup>, M. Simon<sup>5</sup>, M. Su<sup>2</sup>, P. Vliex<sup>1</sup>, S. van Waasen<sup>1,6</sup>, C. Witt<sup>7</sup>, D. Zetzsche<sup>3</sup>

<sup>1</sup>Central Institute of Engineering, Electronics and Analytics, Electronics Systems (ZEA-2),

Forschungszentrum Jülich GmbH, 52428, Jülich, Germany

<sup>2</sup>AdMOS GmbH, 72636 Frickenhausen, Germany

<sup>3</sup>Raycics GmbH, 01069 Dresden, Germany

<sup>4</sup>Global Foundries, 01109, Dresden, Germany

<sup>5</sup> Fraunhofer Institute for Photonic Microsystems IPMS, Center Nanoelectronic Technologies (CNT), 01109, Dresden, Germany

<sup>6</sup>Faculty of Engineering, Communication Systems, University Duisburg-Essen, 47057 Duisburg, Germany

Scalable quantum computers demand innovative solutions for tackling the wiring bottleneck to control an increasing number of qubits. Cryogenic electronics based on CMOS technologies are promising candidates which can operate down to deep-cryogenic temperatures and act as a communication and control interface to the quantum layer [1,2]. However, the performance of transistors used in these circuits is altered significantly when cooling from room temperature to cryogenic temperatures, which motivates accurate cryogenic modeling of transistors.

GlobalFoundries, Kapeldreef 75, 3001 Leuven, Belgium

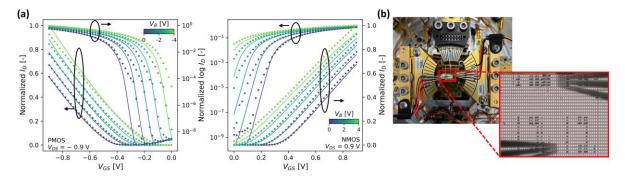

We will report on cryogenic models tailored specifically for fully depleted silicon-on-insulator (FDSOI) transistors. We performed extensive DC characterization of transistors with subsequent modeling using the BSIM-IMG 102-9.6 model, which is the first version with a built-in cryogenic extension [3]. The preliminary models effectively represent the DC device behavior from 7 K up to room temperature. These models are used in industry standard EDA and simulation software, like Cadence Spectre. With the presented cryogenic models, we will show simulations at cryogenic temperatures. We will also compare the simulation results with the measured performance of a test chip in the temperature range from 7 K up to room temperature.

**Fig. 1:** (a) Measured (markers) and modeled (lines) transfer characteristics of a short-channel PMOS and NMOS transistor for different back gate bias  $(V_B)$  at T=7 K. (b) Measurement setup inside the cryogenic chamber along with a micrograph of the die.

## References

- 1. J. Anders et al., IEEE Transactions on Quantum Engineering, vol. 4, pp. 1-30, 2023.

- 2. E. Charbon et al., IEEE International Electron Devices Meeting (IEDM), pp. 13.5.1-4, 2016.

- 3. Hu, Chenming, et al, Woodhead Publishing, 2019.

## Acknowledgements

This work was funded by the German Federal Ministry of Education and Research (BMBF), funding program "Quantum technologies - from basic research to market", project QSolid (Grant No. 13N16149).