pubs.acs.org/NanoLett Letter

# Ultrasteep Slope Cryogenic FETs Based on Bilayer Graphene

Eike Icking, David Emmerich, Kenji Watanabe, Takashi Taniguchi, Bernd Beschoten, Max C. Lemme, Joachim Knoch, and Christoph Stampfer\*

Cite This: Nano Lett. 2024, 24, 11454-11461

**ACCESS** I

III Metrics & More

Article Recommendations

Supporting Information

ABSTRACT: Cryogenic field-effect transistors (FETs) offer great potential for applications, the most notable example being classical control electronics for quantum information processors. For the latter, on-chip FETs with low power consumption are crucial. This requires operating voltages in the millivolt range, which are only achievable in devices with ultrasteep subthreshold slopes. However, in conventional cryogenic metal-oxide-semiconductor (MOS)FETs based on bulk material, the experimentally achieved inverse subthreshold slopes saturate around a few mV/dec due to disorder and charged defects at the MOS interface. FETs based on two-dimensional materials offer a promising alternative. Here, we show that FETs based on Bernal stacked bilayer graphene encapsulated in hexagonal boron nitride and

graphite gates exhibit inverse subthreshold slopes of down to 250  $\mu$ V/dec at 0.1 K, approaching the Boltzmann limit. This result indicates an effective suppression of band tailing in van der Waals heterostructures without bulk interfaces, leading to superior device performance at cryogenic temperature.

KEYWORDS: Bernal stacked bilayer graphene, band gap, subthreshold slope, disorder

Field-effect transistors operable at cryogenic temperatures are an ongoing area of research and are an ongoing area of research with potential applications in outer space electronic devices, 1-5 semiconductor-superconducting coupled systems,<sup>6</sup> scientific instruments such as infrared sensors,<sup>5,7,8</sup> and notably control electronics in quantum computing.<sup>9–14</sup> The distinct advantages of operating at cryogenic temperatures include reduced power dissipation, minimized thermal noise, and faster signal transmission. 1,15,16 The significance of cryogenic control electronics is especially apparent in the context of quantum information processing, where the availability of control electronics in close proximity to the qubits is seen as a necessary condition for operating large quantum processors with thousands of qubits. 11,14,17 However, developing cryogenic electronics for quantum computing applications poses significant challenges due to the limited cooling power of dilution refrigerators. One of the requirements is to reduce the operational voltage range of the FETs into the mV range,<sup>21</sup> which, in turn, requires devices with ultrasteep subthreshold slopes. Temperature broadening effects impose a lower limit-the so-called Boltzmann limit-to the inverse subthreshold slope (SS) given by  $SS_{BL} = k_BT/e$ . ln(10), where T is the operating temperature and  $k_B$  the Boltzmann constant. Thus, the inverse SS is expected to decrease from 60 mV/dec at room temperature to as low as, e.g., 20  $\mu$ V/dec at 0.1 K. However, experiments with conventional FET devices optimized for low-temperature operation have shown that the inverse SS saturates at considerably higher values in the order of 10 mV/dec at

cryogenic temperature.<sup>22-25</sup> This saturation originates mainly from static disorder at the metal-oxide-semiconductor (MOS) interface (due to, e.g., surface roughness, charged defects,etc.). <sup>23,24,24–27</sup> This contributes to the formation of a finite density of states (DOS) near the band edges, which decays exponentially into the band gap.<sup>28</sup> This so-called band-tailing leads to deteriorated off-state behavior and limits the achievable SS. This effect is further enhanced by dopants, which could either freeze out or become partially ionized. 21,29 Interface engineering can improve the MOS interface,<sup>30</sup> but in MOSFETs based on bulk materials, inherent disorder at the interfaces and charged defects within bulk dielectrics cannot be fully eliminated.

FETs based entirely on van der Waals (vdW) materials are a promising alternative because these materials offer atomically clean interfaces, as there are no dangling bonds in the vertical direction. Particularly promising for cryogenic applications are vdW-heterostructures based on Bernal stacked bilayer graphene (BLG).34 Indeed, it has been shown that by encapsulating BLG into hexagonal boron nitride (hBN) and

Received: May 29, 2024 Revised: August 7, 2024 Accepted: August 13, 2024 Published: September 4, 2024

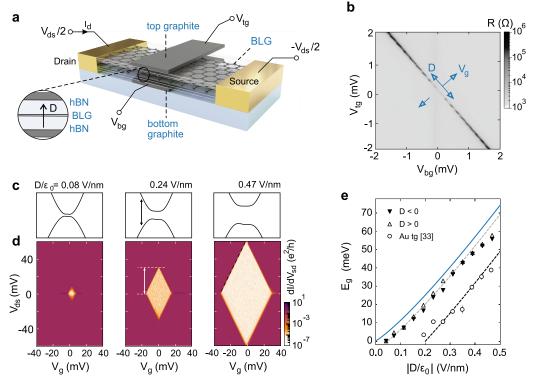

Figure 1. (a) Schematic illustration of a bilayer graphene-based FET. In the active area of the device, the hBN-BLG-hBN heterostructure (see inset) is sandwiched between a top and bottom graphite gate. These gates allow for an independent tuning of the displacement field D and the effective gate voltage  $V_{\rm g}$ . The drain-source voltage  $V_{\rm ds}$  is applied symmetrically in all our measurements. (b) Resistance ( $R = V_{\rm ds}/I_{\rm d}$ ) of the BLG as a function of  $V_{\rm bg}$  and  $V_{\rm tg}$  at T=1.6 K and  $V_{\rm ds}=1$  mV. The blue arrows indicate the directions of increasing displacement field D and  $V_{\rm g}$ . (c) Calculated band structure of BLG around one of the band minima for different displacement fields (see labels). (d) Differential conductance  $dI/dV_{\rm ds}$  as a function of  $V_{\rm ds}$  and  $V_{\rm g}$  (at T=0.1 K) for different displacement fields (see labels in c). The band gap  $E_{\rm g}$  can be extracted from the extension of the diamond along the  $V_{\rm ds}$  axis (see label). (e) Extracted  $E_{\rm g}$  as a function of  $|D/\varepsilon_0|$ . The experimental data are in good agreement with theory calculated according to ref 31 using  $\varepsilon_{\rm BLG}=1$  (blue line) including an offset of 5 meV (gray dashed line). Note that for the same displacement field, the achieved band gap is almost 20 meV higher compared to state-of-the-art BLG devices with gold top gates (open circles taken from ref 32).

by placing it on graphite (Gr), it is possible to open a tunable, ultraclean, and spatially homogeneous band gap in BLG by applying an out-of-plane electric displacement field. 31,35,36 Such BLG-based heterostructures can be seen as an electrostatically tunable semiconductor. 32,37,38 The high device quality allowed the realization of BLG-based quantum point contacts<sup>38,39</sup> and quantum dot devices.<sup>40–42</sup> Further incorporating graphite top gates (tg) instead of state-of-the-art gold top gates in the BLG heterostructures promises a further reduction of disorder as recent publications reported magnetic and even superconducting phases hosted in the valence and conduction bands of BLG. 43-45 In this work, we demonstrate the enhanced device quality of dual graphite-gated BLG, evident in ultraclean band gaps and ultrasmall inverse subthreshold slopes, establishing vdW-material-based heterostructures as an ideal platform for cryogenic FETs. We use finite bias spectroscopy to show that the band gap tunability is enhanced in pure vdW BLG heterostructures with almost no residual disorder. By extracting the inverse subthreshold slopes, we obtain values as low as 250  $\mu$ V/dec at T = 0.1 K, which is only an order of magnitude larger than the Boltzmann limit of 20  $\mu$ V/dec at this temperature. These results demonstrate the effective suppression of band tailing, leading to superior cryogenic device behavior of FETs based on vdW materials compared to conventional FETs.

The studied devices are fabricated by a standard dry van-der-Waals transfer technique. 46,47 The process involves the sequential stacking of hBN, graphite and BLG flakes produced by mechanical exfoliation.<sup>48</sup> First, a large hBN flake is selected to completely cover the top graphite gate, which is picked up in the second step. The (top) graphite gate is encapsulated in another hBN flake which acts as the top gate dielectric. We then pick up the BLG, a third hBN flake (bottom gate dielectric), and the bottom graphite gate and transfer the vdW heterostructure to a Si<sup>++</sup>/SiO<sub>2</sub> substrate. The exact thicknesses of the used hBN dielectric layers (mainly ≈20 nm) can be found in the Table S1. Complete encapsulation of the BLG in hBN is essential to prevent degradation and short circuits to the graphite gates. One-dimensional side contacts are then fabricated using electron-beam lithography, CF<sub>4</sub>-based reactive ion etching and metal evaporation followed by lift-off.<sup>46</sup> A schematic of the final device, including the gating and contacting scheme, is shown in Figure 1a (an optical image can be found in the Figure S1). If not stated otherwise, all measurements were performed at T = 0.1 K in a dilution refrigerator with a two-terminal configuration, where we applied the drain-source voltage symmetrically (for more information on the measurement setup, see ref 32).

As a first electrical characterization, we measure the drain current  $I_{\rm d}$  as a function of top and bottom gate voltage by applying a small drain-source voltage  $V_{\rm ds}$  = 100  $\mu$ V. Figure 1b

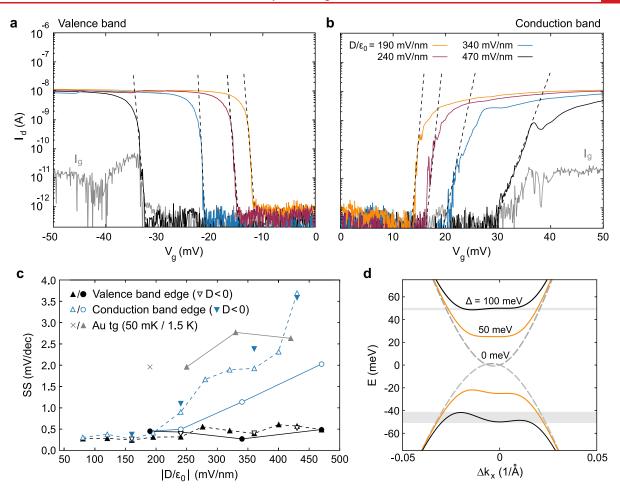

Figure 2. (a, b) Drain current as a function of  $V_{\rm g}$  for four different displacement fields (see different colors and labels in panel b) near the valence band edge (panel a) and the conduction band edge (panel b). The gate leakage current is shown as the gray trace exemplarily for  $D/\varepsilon_0$  = 470 mV/nm (see also Figure S4). Measurements were taken at  $V_{\rm ds}$  = 0.1 mV and T = 0.1 K. (c) Extracted minimal inverse subthreshold slope as a function of the displacement field for both, the valence (black) and conduction (blue) band edges. The black-filled circles and blue circles correspond to data directly extracted from the measurements shown in panels a and b (see black dashed lines), respectively. The upward-pointing triangles are extracted from similar measurements at slightly higher  $V_{\rm ds}\approx 0.5$  mV. Both measurements result in values around 0.3 mV/dec at the valence band edge. At the conduction band edge the  $SS_{\rm min}$  values show an increase with increasing D. Downward-pointing triangles denote SS extracted for negative displacement fields. The gray symbols represent the SS extracted from two devices with a gold top gate at the valence band edge (cross: first device measured at 50 mK, gray upward-pointing triangles: second device measured at 1.5 K). (d) Calculated band structure for different onsite potential differences  $\Delta$  between the BLG layers.  $\Delta k_x$  represents the momentum relative to the K and K' points. Due to trigonal warping effects,  $\Delta k_x$  the bands show an asymmetric deformation if a band gap is present. With increasing onsite potential difference, the asymmetry of the deformation increases, indicating a possible origin of the asymmetry in inverse subthreshold slope values.

shows the resulting map of the BLG resistance R =  $V_{ds}/I_{d}$ . Here, we observe a diagonal feature of increased resistance with a slope  $\beta = 1.22$ , which gives us directly the relative gate lever arm  $\beta$  =  $\alpha_{\rm bg}/\alpha_{\rm tg}$ , where  $\alpha_{\rm bg}$  and  $\alpha_{\rm tg}$  denote the gate leverarms of the top and bottom gate and can be extracted from quantum Hall measurements<sup>49-51</sup> (for more information, see Supporting Information). The increasing width of the region of maximum resistance with increasing gate voltages is direct evidence for the formation and tuning of the BLG band gap with increasing out-of-plane displacement field D (see also band structure calculations in Figure 1c). The displacement field in the dual-gated BLG-based vdW heterostructure is given by  $D = e\alpha_{\rm tg}[\beta(V_{\rm bg} - V_{\rm bg}^0) - (V_{\rm tg} - V_{\rm tg}^0)]/2$ , and the effective gate voltage is given by  $V_{\rm g} = [\beta(V_{\rm bg} - V_{\rm bg}^0) + (V_{\rm tg} - V_{\rm tg}^0)]/(1 + V_{\rm tg}^0)]/(1 + V_{\rm tg}^0)$  $\beta$ ), which tunes the electrochemical potential in the band gap of the BLG,  $\mu \approx eV_{\rm g}$ . Here,  $\varepsilon_0$  is the vacuum permittivity, and the parameters  $V_{\rm tg}^0$  and  $V_{\rm bg}^0$  account for the offsets of the charge neutrality point from  $V_{\rm tg} = V_{\rm bg} = 0$ .

To study the band gap opening in our devices as a function of the displacement field D, we perform finite bias spectroscopy measurements and investigate the differential conductance  $dI/dV_{\rm ds}$  as a function of the effective gating potential  $V_{\rm g}$  and the applied drain-source voltage  $V_{\rm ds}$  for different fixed displacement fields D, see Figure 1d. A distinct diamond-shaped region of suppressed conductance emerges, which has a high degree of symmetry and sharp edges and scales well with the applied displacement field. The outlines of the diamonds (black dashed lines in Figure 1d) show a slope of  $\approx$ 2, highlighting that  $V_{\rm g}$  directly tunes the electrochemical potential  $\mu$  within the band gap and indicating that the band gap is as good as free of any trap states. In the Supporting Information, we show that the slope of the diamond outlines is indeed constant ( $\approx$  2) for all displacement fields  $D/\varepsilon_0 \gtrsim 0.2$  V/nm.

From the extension of the diamonds on the  $V_{\rm ds}$  axis, we can directly extract the size of the band gap  $E_{\rm gr}^{32}$  which are shown

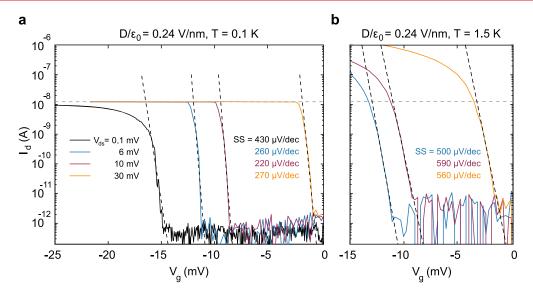

Figure 3. (a, b) Drain current as a function of  $V_g$  at the valence band edge for different applied drain-source voltages  $V_{\rm ds}$  at a fixed displacement field  $D/\varepsilon_0 \approx 0.24$  V/nm. The data shown in panel a were taken in a dilution refrigerator at T=0.1 K, while those presented in panel b were taken in a pumped <sup>4</sup>He cryostat at T=1.5 K. The first setup limits the on-current to roughly  $10^{-8}$  A. The second system allows higher on-currents of 1  $\mu$ A. However, we observe a higher noise level resulting in a slightly increased off-current.

in Figure 1e for positive (filled triangles) and negative displacement fields (empty triangles). They agree reasonably well with the theoretical prediction assuming an effective dielectric constant of BLG of  $\varepsilon_{\rm BLG}=1$  (blue line, for more information, see Supporting Information.) except for a small offset of 5 meV (gray dashed line), which might be due to some residual disorder or interaction effects. Measurements on a second graphite top-gated device reveal the same behavior (see Figure S9).

In Figure 1e we also report the results of measurements performed on a similar BLG device but with the top gate made of gold instead of graphite (see ref 32). It is noteworthy that the extracted band gap for the device with graphite gates is almost 20 meV higher than that extracted for the device with a gold top gate for the same displacement fields, highlighting the importance of clean vdW-interfaces. Furthermore, the observed extracted band gap  $E_{\rm g}$  persists down to lower displacement fields  $D/\varepsilon_0 \approx 50$  mV/nm compared to devices with a gold top gate.

The high tuning efficiency of the band gap in graphite dual-gated BLG combined with the high symmetry of the diamonds from the bias spectroscopy measurements demonstrates that BLG heterostructures built entirely from vdW materials, including top and bottom gates, outperform BLG devices with non-vdW materials thanks to much cleaner interfaces, allowing them to achieve unprecedented levels of device quality.

The finite bias spectroscopy measurements show that the edges of the diamonds are sharply defined, which promises excellent switching efficiency of FETs based on dual graphitegated BLG when using  $V_{\rm g}$  as the tuning parameter. To extract the inverse subthreshold slope, we measure the drain current  $I_{\rm d}$  as a function of  $V_{\rm g}$  for fixed D-field and  $V_{\rm ds}\approx 0.1$  mV at both band edges, see Figures 2a and 2b. From the linear fits of the slopes (black dashed lines), we extract the inverse subthreshold slope SS =  $(\partial (\log_{10}(I_{\rm d})/\partial V_{\rm g})^{-1}$ . The resulting values for the valence and conduction band are plotted in Figure 2c.

At the valence band edge, we extract record low values of SS  $\approx 270-500 \ \mu\text{V/dec}$ , roughly 1 order of magnitude above the

Boltzmann limit  $SS_{BL}(0.1~K)=20~\mu V/dec$ . For comparison, the saturation limit of conventional FETs based on non-vdW materials at  $T\approx 0.1~K$  is in the order of a few mV/dec. We repeat similar measurements for slightly higher drain-source voltages  $V_{\rm ds}\approx 0.5~{\rm mV}$ . The results are also shown in Figure 2c as upward-pointing triangles. They agree overall with the values from the measurements at  $V_{\rm ds}=0.1~{\rm mV}$ , with inverse subthreshold slopes at the valence band around SS  $\approx 250~{\rm to}~500~\mu V/{\rm dec}$ . The very low SS value indicates that band tailing is suppressed for devices with only vdW interfaces. This is also supported by the fact that samples with a gold top gate (i.e., an interface between a vdW and a bulk material) show significantly higher SS values for comparable D-fields at the valence band edge (see the cross and gray upward-pointing triangles in Figure 2c).

It is remarkable to observe that while the SS extracted at the valence band edge does not show a significant dependency on the applied displacement field D, the values extracted at the conduction band edge show a considerable increase from SS  $\approx$ 500  $\mu$ V/dec up to SS  $\approx 2.8$  mV/dec with increasing D. This displacement field-dependent asymmetry of the SS values is related to the electron-hole asymmetry of the BLG band structure. In principle, this asymmetry could also be due to a top-bottom asymmetry of (weak) interface disorder in the vdW heterostructure, since transport near the band edges is dominated by orbitals in only one of the two graphene layers. For example, for a positive D-field, transport at the conductance (valence) band edge is carried only by the top (bottom) layer of the BLG.<sup>32</sup> Changing the D-field direction reverses the band-edge to layer assignment. This allows us to experimentally exclude such a possible nonuniformity of the interface disorder, as we observe the same asymmetry in the SS values for the conductance and valence band edge also for negative D-fields (see downward pointing triangles in Figure 2c), in good agreement with the values for positive D-fields, thus strongly emphasizing the importance of the asymmetry in the BLG band structure. In Figure 2d we show the calculated band structure as a function of the onsite potential difference between the layers  $\Delta(D)$ , which can be directly tuned with the

applied displacement field D (for more information on the calculations, see Supporting Information). With increasing  $\Delta(D)$ , the bands undergo an increasingly asymmetric deformation due to the trigonal-warping effect. 33,52 As a consequence, the bands change from a hyperbolic shape at low  $\Delta(D)$  to an asymmetric Mexican-hat shape for high  $\Delta(D)$ ,<sup>31</sup> see Figure 2d. With increasing band deformation, parts of the bands close to the K and K' points of the Brillouin zone become flat. Recent studies have shown that these flat bands give rise to a rich phase diagram in BLG, where magnetic and superconducting phases emerge. 43-45 The emerging phases could act phenomenologically similar to the interface-induced disorder, resulting in effective tail states at the band edges and degradation of the SS. The flat parts of the bands are right at the conduction band edge, but slightly deeper in the valence band: for example, for  $\Delta = 100$  meV in Figure 2d, the local valence band maximum is much more pronounced than the local conduction band minimum (see gray shaded areas). Consequently, the resulting phase diagrams also exhibit an asymmetry similar to our SS values, 45 which suggests that the asymmetric band deformation could cause the SS asymmetry in our measurements. We observed the same behavior for a second device, although at slightly different D-fields (see Figure S10), most likely due to sample-to-sample variations. Regardless, we would like to emphasize that this consistent asymmetry is in itself an indicator of the overall low disorder in our devices.

While our device presents excellent SS values, the measured on-off ratio in Figure 2a and b is only about 10<sup>4</sup> to 10<sup>5</sup>, which is a direct consequence of the low on-current of about  $I_{\rm d} \approx$ 10<sup>-8</sup> A. This low current level is partially due to the small size of the device contacts, which are circularly etched vias through the hBN, with a diameter of just 1  $\mu$ m. However, it is mainly because the measured current is limited by our measurement setup, which is optimized for low-noise, small-current measurements but also imposes a sharp limit of about 10<sup>-8</sup> A, see Figure 3a. In a different setup at higher temperatures T = 1.5 K, we observe on-currents of up to 1  $\mu$ A in the very same device for large  $V_{\rm ds}$  = 30 mV, see Figure 3b, indicating that higher currents are possible also with the contact geometry used. This is also confirmed by measurements in a second device of similar design, where we measure currents up to 1  $\mu$ A even at T = 0.1 K in a different low-temperature setup (see Figure S11).

The measurements presented in Figure 3 also show that the threshold voltage shifts to lower values of  $V_{\rm g}$  with increasing  $V_{\rm ds}$ , without significantly affecting SS, see Figure 3a (more data are provided in Sec. 3 in the Supporting Information). This implies that—despite the small on-current—the device presented in this manuscript could be operated at  $T=0.1~{\rm K}$  as a FET with an on—off ratio of at least  $10^5$  and an operational voltage range of only 3–4 mV by suitably choosing the drain-source voltage  $V_{\rm ds}$ , thanks to the small SS  $\approx 250~{\mu}{\rm V/dec}$  At  $T=1.5~{\rm K}$ , reaching an on—off ratio of  $10^5~{\rm will}$  require operational voltages of 6–7 mV due to a slightly higher noise level and slightly higher SS  $\approx 500~{\mu}{\rm V/dec}$ .

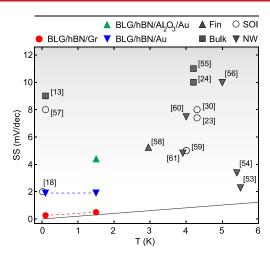

Finally, we summarize in Figure 4 the minimum inverse SS for different transistor device architectures reported in the literature (empty dots) as a function of temperature for low  $T \le 6$  K. The best performing conventional FET devices, based on silicon-on-insulator or nanowires, allow to reach SS  $\approx 2$  mV/dec. These values are almost an order of magnitude higher than the 250  $\mu$ V/dec of the BLG-based devices reported in this

**Figure 4.** Comparison of the extracted low-temperature SS values for different types of FET devices. The red dots correspond to the device presented in this paper. The blue triangles refer to a similar device but where the top gate was made of gold instead of graphite, and the green triangle refers to a third BLG device with an additional  $Al_2O_3$  layer between the hBN and the gold gate. The empty symboles correspond to SS values reported in the literature for FETs based on different technologies (silicon on insulator (SOI), bulk CMOS, Fin, and nanowire FETs<sup>13,18,23,25,30,53-61</sup>). FETs based on vdW heterostructures outperform all other technologies in terms of SS at cryogenic temperatures. The solid black line is the theoretical Boltzmann limit  $SS_{BL} = k_BT/e \ln(10)$ .

work (red dots). The theoretical Boltzmann limit is included as a solid line. At T=1.5 K, the Boltzmann limit is  $\mathrm{SS_{BL}}\approx 300$   $\mu\mathrm{V/dec}$ , only slightly less than the inverse subthreshold slope of our device (SS  $\approx 500~\mu\mathrm{V/dec}$ ). We attribute this improvement in SS directly to the reduced interface disorder in devices based on pure vdW heterostructures, i.e., without bulk interfaces to metal or oxides. The detrimental effect of bulk interfaces is well illustrated by the much higher SS values of BLG devices, where the top gate was made of gold instead of graphite (blue triangles in Figure 4). A BLG device with an additional  $\mathrm{Al_2O_3}$  between the metal top gate and the top hBN performed even worse (green triangle).

In summary, we have demonstrated that BLG devices based on pure vdW materials exhibit excellent band gap tunability and have provided evidence that 2D material-based FETs offer superior device behavior at cryogenic temperatures, with SS in the order of 250  $\mu V/{\rm dec}$ , only 1 order of magnitude above the Boltzmann limit of SS $_{\rm BL}\approx 20~\mu V/{\rm dec}$  at T=0.1 K. The ability to also electrostatically confine carriers in BLG $^{38,40,42}$  and the excellent performance as a field-effect transistor make this type of device an ideal platform for cryogenic applications and calls for further device design improvements that allow for downscaling and circuit integration. Moreover, we expect this work to trigger the exploration of pure vdW heterostructure FETs based on true 2D semiconductors, such as the transition metal dichalcogenides MoS $_2$  and WSe $_2$ .

## ASSOCIATED CONTENT

#### **Data Availability Statement**

The data supporting the findings are available in a Zenodo repository under accession code 10.5281/zenodo.10526847.

### Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acs.nanolett.4c02463.

Equations used to calculate the band gap and band structure in bilayer graphene as a function of the displacement field, additional information for the first sample, comparable data for a second device, and the drain-current traces for the BLG devices with Au top gate and additional  $Al_2O_3$  dielectric (PDF)

## AUTHOR INFORMATION

#### **Corresponding Author**

Christoph Stampfer — JARA-FIT and 2nd Institute of Physics, RWTH Aachen University, 52074 Aachen, Germany; Peter Grünberg Institute (PGI-9), Forschungszentrum Jülich, 52425 Jülich, Germany; orcid.org/0000-0002-4958-7362; Email: stampfer@physik.rwth-aachen.de

#### **Authors**

Eike Icking — JARA-FIT and 2nd Institute of Physics, RWTH Aachen University, 52074 Aachen, Germany; Peter Grünberg Institute (PGI-9), Forschungszentrum Jülich, 52425 Jülich, Germany; orcid.org/0000-0002-6923-0854

David Emmerich – JARA-FIT and 2nd Institute of Physics, RWTH Aachen University, 52074 Aachen, Germany; Peter Grünberg Institute (PGI-9), Forschungszentrum Jülich, 52425 Jülich, Germany

Kenji Watanabe – Research Center for Electronic and Optical Materials, National Institute for Materials Science, Tsukuba 305-0044, Japan

Takashi Taniguchi — Research Center for Materials Nanoarchitectonics, National Institute for Materials Science, Tsukuba 305-0044, Japan; orcid.org/0000-0002-1467-3105

Bernd Beschoten – JARA-FIT and 2nd Institute of Physics, RWTH Aachen University, 52074 Aachen, Germany; orcid.org/0000-0003-2359-2718

Max C. Lemme – Chair of Electronic Devices, RWTH Aachen University, 52074 Aachen, Germany; AMO GmbH, 52074 Aachen, Germany; © orcid.org/0000-0003-4552-2411

Joachim Knoch – IHT, RWTH Aachen University, 52074 Aachen, Germany

Complete contact information is available at: https://pubs.acs.org/10.1021/acs.nanolett.4c02463

#### **Notes**

The authors declare no competing financial interest.

# **■** ACKNOWLEDGMENTS

The authors thank S. Trellenkamp and F. Lentz for their support in device fabrication. This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No. 881603 (Graphene Flagship), from the European Research Council (ERC) under grant agreement No. 820254, the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) under Germany's Excellence Strategy - Cluster of Excellence Matter and Light for Quantum Computing (ML4Q) EXC 2004/1-390534769, by the FLAG-ERA grant PhotoTBG, by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) - 471733165, by the FLAG-ERA grant TATTOOS, by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) - 437214324, from the EU project ATTOSWITCH under grant No. 101135571, and by the Helmholtz Nano Facility. 62 K.W. and

T.T. acknowledge support from the JSPS KAKENHI (Grant Numbers 20H00354, 21H05233 and 23H02052) and World Premier International Research Center Initiative (WPI), MEXT, Japan.

### REFERENCES

- (1) Gutiérrez-D, E.; Claeys, C.; Simoen, E. In *Low Temperature Electronics*; Gutiérrez-D, E. A., Deen, M. J., Claeys, C., Eds.; Academic Press: San Diego, 2001; pp 105–257.

- (2) Chen, T.; Zhu, C.; Najafizadeh, L.; Jun, B.; Ahmed, A.; Diestelhorst, R.; Espinel, G.; Cressler, J. D. CMOS reliability issues for emerging cryogenic Lunar electronics applications. *Solid-State Electron.* **2006**, *50*, 959–963.

- (3) Patterson, R.; Hammoud, A.; Elbuluk, M. Assessment of electronics for cryogenic space exploration missions. *Cryogenics* **2006**, 46, 231–236.

- (4) Bourne, J.; Schupbach, R.; Hollosi, B.; Di, J.; Lostetter, A.; Mantooth, H. A. Ultra-Wide Temperature (-230°C to 130°C) DC-Motor Drive with SiGe Asynchronous Controller. In 2008 IEEE Aerospace Conference; IEEE, 2008' pp 1–15...

- (5) Han, Y.; Zhang, A. Cryogenic technology for infrared detection in space. Sci. Rep. 2022, 12, 2349.

- (6) Feng, Y.; Zhou, P.; Liu, H.; Sun, J.; Jiang, T. Characterization and modelling of MOSFET operating at cryogenic temperature for hybrid superconductor-CMOS circuits. *Semicond. Sci. Technol.* **2004**, *19*, 1381.

- (7) Zocca, F.; Pullia, A.; Riboldi, S.; D'Andragora, A.; Cattadori, C. Setup of cryogenic front-end electronic systems for germanium detectors read-out. 2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC); IEEE, 2009' pp 368–372.

- (8) Wada, T.; Nagata, H.; Ikeda, H.; Arai, Y.; Ohno, M.; Nagase, K. Development of Low Power Cryogenic Readout Integrated Circuits Using Fully-Depleted-Silicon-on-Insulator CMOS Technology for Far-Infrared Image Sensors. *Journal of Low Temperature Physics* **2012**, 167, 602–608.

- (9) Homulle, H.; Visser, S.; Patra, B.; Ferrari, G.; Prati, E.; Sebastiano, F.; Charbon, E. A reconfigurable cryogenic platform for the classical control of quantum processors. *Rev. Sci. Instrum.* **2017**, 88, 045103.

- (10) Almudever, C. G.; Lao, L.; Fu, X.; Khammassi, N.; Ashraf, I.; Iorga, D.; Varsamopoulos, S.; Eichler, C.; Wallraff, A.; Geck, L.; Kruth, A.; Knoch, J.; Bluhm, H.; Bertels, K. The engineering challenges in quantum computing. In *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, 2017; pp 836–845.

- (11) Vandersypen, L. M. K.; Bluhm, H.; Clarke, J. S.; Dzurak, A. S.; Ishihara, R.; Morello, A.; Reilly, D. J.; Schreiber, L. R.; Veldhorst, M. Interfacing spin qubits in quantum dots and donors—hot, dense, and coherent. *npj Quantum Inf.* **2017**, *3*, 1–10.

- (12) Patra, B.; Incandela, R. M.; van Dijk, J. P. G.; Homulle, H. A. R.; Song, L.; Shahmohammadi, M.; Staszewski, R. B.; Vladimirescu, A.; Babaie, M.; Sebastiano, F.; Charbon, E. Cryo-CMOS Circuits and Systems for Quantum Computing Applications. *IEEE Journal of Solid-State Circuits* **2018**, *53*, 309–321.

- (13) Incandela, R. M.; Song, L.; Homulle, H.; Charbon, E.; Vladimirescu, A.; Sebastiano, F. Characterization and Compact Modeling of Nanometer CMOS Transistors at Deep-Cryogenic Temperatures. *IEEE Journal of the Electron Devices Society* **2018**, 6, 996–1006.

- (14) Boter, J. M.; Dehollain, J. P.; van Dijk, J. P.; Xu, Y.; Hensgens, T.; Versluis, R.; Naus, H. W.; Clarke, J. S.; Veldhorst, M.; Sebastiano, F.; Vandersypen, L. M. Spiderweb Array: ASparse Spin-Qubit Array. *Phys. Rev. Appl.* **2022**, *18*, 024053.

- (15) Balestra, F.; Ghibaudo, G. Device and Circuit Cryogenic Operation for Low Temperature Electronics; Springer, 2001.

- (16) Rajashekara, K.; Akin, B. A review of cryogenic power electronics status and applications. In 2013 International Electric Machines & Drives Conference, 2013; pp 899–904.

- (17) Charbon, E.; Sebastiano, F.; Vladimirescu, A.; Homulle, H.; Visser, S.; Song, L.; Incandela, R. M. Cryo-CMOS for quantum computing. In 2016 IEEE International Electron Devices Meeting (IEDM), 2016; 13.5.1–13.5.4.

- (18) Galy, P.; Camirand Lemyre, J.; Lemieux, P.; Arnaud, F.; Drouin, D.; Pioro-Ladrière, M. Cryogenic Temperature Characterization of a 28-nm FD-SOI Dedicated Structure for Advanced CMOS and Quantum Technologies Co-Integration. *IEEE Journal of the Electron Devices Society* **2018**, *6*, 594–600.

- (19) Hollmann, A.; Jirovec, D.; Kucharski, M.; Kissinger, D.; Fischer, G.; Schreiber, L. R. 30 GHz-voltage controlled oscillator operating at 4 K. Rev. Sci. Instrum. 2018, 89, 114701.

- (20) Guevel, L. L.; Billiot, G.; Jehl, X.; De Franceschi, S.; Zurita, M.; Thonnart, Y.; Vinet, M.; Sanquer, M.; Maurand, R.; Jansen, A. G. M.; Pillonnet, G. 19.2 A 110mK 295µW 28nm FDSOI CMOS Quantum Integrated Circuit with a 2.8 GHz Excitation and nA Current Sensing of an On-Chip Double Quantum Dot. In 2020 IEEE International Solid- State Circuits Conference (ISSCC), 2020; pp 306–308.

- (21) Knoch, J.; Richstein, B.; Han, Y.; Frentzen, M.; Rainer Schreiber, L.; Klos, J.; Raffauf, L.; Wilck, N.; König, D.; Zhao, Q.-T. Toward Low-Power Cryogenic Metal-Oxide Semiconductor Field-Effect Transistors. *physica status solidi* (a) **2023**, 220, 2300069.

- (22) Achour, H.; Talmat, R.; Cretu, B.; Routoure, J.-M.; Benfdila, A.; Carin, R.; Collaert, N.; Simoen, E.; Mercha, A.; Claey, C. DC and low frequency noise performances of SOI p-FinFETs at very low temperature. *Solid-State Electron.* **2013**, *90*, 160–165.

- (23) Bohuslavskyi, H.; et al. Cryogenic Subthreshold Swing Saturation in FD-SOI MOSFETs Described With Band Broadening. *IEEE Electron Device Lett.* **2019**, *40*, 784–787.

- (24) Beckers, A.; Jazaeri, F.; Enz, C. Inflection Phenomenon in Cryogenic MOSFET Behavior. *IEEE Trans. Electron Devices* **2020**, *67*, 1357–1360.

- (25) Beckers, A.; Jazaeri, F.; Enz, C. Theoretical Limit of Low Temperature Subthreshold Swing in Field-Effect Transistors. *IEEE Electron Device Lett.* **2020**, *41*, 276–279.

- (26) Kamgar, A. Subthreshold behavior of silicon MOSFETs at 4.2 K. Solid-State Electron. 1982, 25, 537-539.

- (27) Ghibaudo, G.; Aouad, M.; Casse, M.; Martinie, S.; Poiroux, T.; Balestra, F. On the modelling of temperature dependence of subthreshold swing in MOSFETs down to cryogenic temperature. *Solid-State Electron.* **2020**, *170*, 107820.

- (28) Hill, R. M. Charge transport in band tails. *Thin Solid Films* 1978, 51, 133–140.

- (29) Beckers, A.; Jazaeri, F.; Enz, C. Cryogenic MOSFET Threshold Voltage Model. In ESSDERC 2019 49th European Solid-State Device Research Conference (ESSDERC), 2019; pp 94–97.

- (30) Richstein, B.; Han, Y.; Zhao, Q.; Hellmich, L.; Klos, J.; Scholz, S.; Schreiber, L. R.; Knoch, J. Interface Engineering for Steep Slope Cryogenic MOSFETs. *IEEE Electron Device Lett.* **2022**, 43, 2149–2152.

- (31) McCann, E.; Koshino, M. The electronic properties of bilayer graphene. Rep. Prog. Phys. 2013, 76, 056503.

- (32) Icking, E.; Banszerus, L.; Wörtche, F.; Volmer, F.; Schmidt, P.; Steiner, C.; Engels, S.; Hesselmann, J.; Goldsche, M.; Watanabe, K.; Taniguchi, T.; Volk, C.; Beschoten, B.; Stampfer, C. Transport Spectroscopy of Ultraclean Tunable Band Gaps in Bilayer Graphene. *Advanced Electronic Materials* **2022**, *8*, 2200510.

- (33) Varlet, A.; Bischoff, D.; Simonet, P.; Watanabe, K.; Taniguchi, T.; Ihn, T.; Ensslin, K.; Mucha-Kruczyński, M.; Fal'ko, V. I. Anomalous Sequence of Quantum Hall Liquids Revealing a Tunable Lifshitz Transition in Bilayer Graphene. *Phys. Rev. Lett.* **2014**, *113*, 116602.

- (34) Knoch, J.; Richstein, B.; Han, Y.; Jungemann, C.; Icking, E.; Schreiber, L.; Xue, R.; Tu, J.-S.; Gökcel, T.; Neugebauer, J.; Stampfer, C.; Zhao, Q. On the Performance of Low Power Cryogenic Electronics for Scalable Quantum Information Processors. In 2023 IEEE Nanotechnology Materials and Devices Conference (NMDC), 2023; pp 440–445.

- (35) McCann, E.; Fal'ko, V. I. Landau-Level Degeneracy and Quantum Hall Effect in a Graphite Bilayer. *Phys. Rev. Lett.* **2006**, *96*, 086805.

- (36) Jung, J.; MacDonald, A. H. Accurate tight-binding models for the  $\pi$  bands of bilayer graphene. *Phys. Rev. B* **2014**, *89*, 035405.

- (37) Li, J.; Wang, K.; McFaul, K. J.; Zern, Z.; Ren, Y.; Watanabe, K.; Taniguchi, T.; Qiao, Z.; Zhu, J. Gate-controlled topological conducting channels in bilayer graphene Nature Nanotechnology. *Nat. Nanotechnol.* **2016**, *11*, 1060–1065.

- (38) Overweg, H.; Knothe, A.; Fabian, T.; Linhart, L.; Rickhaus, P.; Wernli, L.; Watanabe, K.; Taniguchi, T.; Sánchez, D.; Burgdörfer, J.; Libisch, F.; Fal'ko, V. I.; Ensslin, K.; Ihn, T. Topologically Nontrivial Valley States in Bilayer Graphene Quantum Point Contacts. *Phys. Rev. Lett.* 2018, 121, 257702.

- (39) Banszerus, L.; Frohn, B.; Fabian, T.; Somanchi, S.; Epping, A.; Müller, M.; Neumaier, D.; Watanabe, K.; Taniguchi, T.; Libisch, F.; Beschoten, B.; Hassler, F.; Stampfer, C. Observation of the Spin-Orbit Gap in Bilayer Graphene by One-Dimensional Ballistic Transport. *Phys. Rev. Lett.* **2020**, *124*, 177701.

- (40) Eich, M.; Pisoni, R.; Pally, A.; Overweg, H.; Kurzmann, A.; Lee, Y.; Rickhaus, P.; Watanabe, K.; Taniguchi, T.; Ensslin, K.; Ihn, T. Coupled Quantum Dots in Bilayer Graphene. *Nano Lett.* **2018**, *18*, 5042–5048.

- (41) Banszerus, L.; Frohn, B.; Epping, A.; Neumaier, D.; Watanabe, K.; Taniguchi, T.; Stampfer, C. Gate-Defined Electron—Hole Double Dots in Bilayer Graphene. *Nano Lett.* **2018**, *18*, 4785–4790.

- (42) Banszerus, L.; Möller, S.; Hecker, K.; Icking, E.; Watanabe, K.; Taniguchi, T.; Hassler, F.; Volk, C.; Stampfer, C. Particle—hole symmetry protects spin-valley blockade in graphene quantum dots. *Nature* **2023**, *618*, 51–56.

- (43) Zhou, H.; Holleis, L.; Saito, Y.; Cohen, L.; Huynh, W.; Patterson, C. L.; Yang, F.; Taniguchi, T.; Watanabe, K.; Young, A. F. Isospin magnetism and spin-polarized superconductivity in Bernal bilayer graphene. *Science* **2022**, *375*, 774–778.

- (44) Seiler, A. M.; Geisenhof, F. R.; Winterer, F.; Watanabe, K.; Taniguchi, T.; Xu, T.; Zhang, F.; Weitz, R. T. Quantum cascade of correlated phases in trigonally warped bilayer graphene. *Nature* **2022**, 608. 298–302.

- (45) de la Barrera, S. C.; Aronson, S.; Zheng, Z.; Watanabe, K.; Taniguchi, T.; Ma, Q.; Jarillo-Herrero, P.; Ashoori, R. Cascade of isospin phase transitions in Bernal-stacked bilayer graphene at zero magnetic field. *Nat. Phys.* **2022**, *18*, 771–775.

- (46) Wang, L.; Meric, I.; Huang, P. Y.; Gao, Q.; Gao, Y.; Tran, H.; Taniguchi, T.; Watanabe, K.; Campos, L. M.; Muller, D. A.; Guo, J.; Kim, P.; Hone, J.; Shepard, K. L.; Dean, C. R. One-Dimensional Electrical Contact to a Two-Dimensional Material. *Science* **2013**, *342*, 614–617.

- (47) Purdie, D. G.; Pugno, N. M.; Taniguchi, T.; Watanabe, K.; Ferrari, A. C.; Lombardo, A. Cleaning interfaces in layered materials heterostructures. *Nat. Commun.* **2018**, *9*, 1–12.

- (48) Novoselov, K. S.; Geim, A. K.; Morozov, S.; Jiang, D.; Zhang, Y.; Dubonos, S.; Grigorieva, I.; Firsov, A. Electric field effect in atomically thin carbon films. *Science* **2004**, *306*, 666–669.

- (49) Zhao, Y.; Cadden-Zimansky, P.; Jiang, Z.; Kim, P. Symmetry Breaking in the Zero-Energy Landau Level in Bilayer Graphene. *Phys. Rev. Lett.* **2010**, *104*, 066801.

- (50) Sonntag, J.; Reichardt, S.; Wirtz, L.; Beschoten, B.; Katsnelson, M. I.; Libisch, F.; Stampfer, C. Impact of Many-Body Effects on Landau Levels in Graphene. *Phys. Rev. Lett.* **2018**, *120*, 187701.

- (51) Schmitz, M.; Ouaj, T.; Winter, Z.; Rubi, K.; Watanabe, K.; Taniguchi, T.; Zeitler, U.; Beschoten, B.; Stampfer, C. Fractional quantum Hall effect in CVD-grown graphene. 2D Mater. 2020, 7, 041007.

- (52) Varlet, A.; Mucha-Kruczyński, M.; Bischoff, D.; Simonet, P.; Taniguchi, T.; Watanabe, K.; Fal'ko, V.; Ihn, T.; Ensslin, K. Tunable Fermi surface topology and Lifshitz transition in bilayer graphene. *Synth. Met.* **2015**, *210*, 19–31.

- (53) Han, Y.; Sun, J.; Bae, J.-H.; Grützmacher, D.; Knoch, J.; Zhao, Q.-T. High Performance 5 nm Si Nanowire FETs with a Record Small

- SS = 2.3 mV/dec and High Transconductance at 5.5 K Enabled by Dopant Segregated Silicide Source/Drain. In 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2023; pp 1–2.

- (54) Han, Y.; Sun, J.; Richstein, B.; Allibert, F.; Radu, I.; Bae, J.-H.; Grützmacher, D.; Knoch, J.; Zhao, Q.-T. Steep Switching Si Nanowire p-FETs With Dopant Segregated Silicide Source/Drain at Cryogenic Temperature. *IEEE Electron Device Lett.* **2022**, 43, 1187–1190.

- (55) Beckers, A.; Jazaeri, F.; Enz, C. Characterization and Modeling of 28-nm Bulk CMOS Technology Down to 4.2 K. *IEEE Journal of the Electron Devices Society* **2018**, *6*, 1007–1018.

- (56) Singh, N.; Lim, F. Y.; Fang, W. W.; Rustagi, S. C.; Bera, L. K.; Agarwal, A.; Tung, C. H.; Hoe, K. M.; Omampuliyur, S. R.; Tripathi, D.; Adeyeye, A. O.; Lo, G. Q.; Balasubramanian, N.; Kwong, D. L. Ultra-Narrow Silicon Nanowire Gate-All-Around CMOS Devices: Impact of Diameter, Channel-Orientation and Low Temperature on Device Performance. In 2006 International Electron Devices Meeting, 2006; pp 1–4.

- (57) Paz, B. C. Variability Evaluation of 28nm FD-SOI Technology at Cryogenic Temperatures down to 100mK for Quantum Computing. In 2020 IEEE Symposium on VLSI Technology, 2020; pp 1–2.

- (58) Han, H.-C.; Jazaeri, F.; D'Amico, A.; Baschirotto, A.; Charbon, E.; Enz, C. Cryogenic Characterization of 16 nm FinFET Technology for Quantum Computing. In ESSDERC 2021 IEEE 51st European Solid-State Device Research Conference (ESSDERC), 2021; pp 71–74.

- (59) Habicht, S.; Feste, S.; Zhao, Q.-T.; Buca, D.; Mantl, S. Electrical characterization of  $\Omega$ -gated uniaxial tensile strained Si nanowire-array metal-oxide-semiconductor field effect transistors with < 100>- and < 110> channel orientations. *Thin Solid Films* **2012**, *520*, 3332–3336.

- (60) Sekiguchi, S.; Ahn, M.-J.; Mizutani, T.; Saraya, T.; Kobayashi, M.; Hiramoto, T. Subthreshold Swing in Silicon Gate-All-Around Nanowire and Fully Depleted SOI MOSFETs at Cryogenic Temperature. *IEEE Journal of the Electron Devices Society* **2021**, *9*, 1151–1154.

- (61) Paz, B. C.; Cassé, M.; Haendler, S.; Juge, A.; Vincent, E.; Galy, P.; Arnaud, F.; Ghibaudo, G.; Vinet, M.; de Franceschi, S.; Meunier, T.; Gaillard, F. Front and back channels coupling and transport on 28 nm FD-SOI MOSFETs down to liquid-He temperature. *Solid-State Electron.* **2021**, *186*, 108071.

- (62) Albrecht, W.; Moers, J.; Hermanns, B. HNF Helmholtz Nano Facility. *Journal of Large-Scale Research Facilities* **2017**, 3, A112.