#### **TOPICAL REVIEW • OPEN ACCESS**

# Technical survey of end-to-end signal processing in BCIs using invasive MEAs

To cite this article: Andreas Erbslöh et al 2024 J. Neural Eng. 21 051003

View the <u>article online</u> for updates and enhancements.

### You may also like

- Real-time TMS-EEG for brain statecontrolled research and precision treatment: a narrative review and guide Miles Wischnewski, Sina Shirinpour, Ivan Alekseichuk et al.

- Review of deep representation learning techniques for brain—computer interfaces Pierre Guetschel, Sara Ahmadi and Michael Tangermann

- Neural decoding and feature selection methods for closed-loop control of avoidance behavior Jinhan Liu, Rebecca Younk, Lauren M Drahos et al.

## Journal of Neural Engineering

#### **OPEN ACCESS**

#### RECEIVED

17 July 2023

#### REVISED

13 August 2024

ACCEPTED FOR PUBLICATION 26 September 2024

15 October 2024

Original Content from this work may be used under the terms of the Attribution 4.0 licence.

Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

#### **TOPICAL REVIEW**

# Technical survey of end-to-end signal processing in BCIs using invasive MEAs

Andreas Erbslöh<sup>1,5,\*</sup>, Leo Buron<sup>1,5,\*</sup>, Zia Ur-Rehman<sup>2,5,\*</sup>, Simon Musall<sup>3</sup>, Camilla Hrycak<sup>1</sup>, Philipp Löhler<sup>1</sup>, Christian Klaes<sup>2</sup>, Karsten Seidl<sup>1,4</sup> and Gregor Schiele<sup>1</sup>

- University of Duisburg-Essen, Duisburg, Germany

- Ruhr University Bochum, Bochum, Germany

- Research Centre Jülich, Jülich, Germany

- Fraunhofer Institute for Microelectronic Circuits and Systems, Duisburg, Germany

- These authors contributed equally.

- Authors to whom any correspondence should be addressed.

E-mail: andreas.erbsloeh@uni-due.de, leo.buron@uni-due.de and zia.ur-rehman@ruhr-uni-bochum.de

Keywords: extracellular recording, low-power electronic, spike sorting, neural decoder, deep learning, neural signal processing, embedded systems

#### **Abstract**

Modern brain-computer interfaces and neural implants allow interaction between the tissue, the user and the environment, where people suffer from neurodegenerative diseases or injuries. This interaction can be achieved by using penetrating/invasive microelectrodes for extracellular recordings and stimulation, such as Utah or Michigan arrays. The application-specific signal processing of the extracellular recording enables the detection of interactions and enables user interaction. For example, it allows to read out movement intentions from recordings of brain signals for controlling a prosthesis or an exoskeleton. To enable this, computationally complex algorithms are used in research that cannot be executed on-chip or on embedded systems. Therefore, an optimization of the end-to-end processing pipeline, from the signal condition on the electrode array over the analog pre-processing to spike-sorting and finally the neural decoding process, is necessary for hardware inference in order to enable a local signal processing in real-time and to enable a compact system for achieving a high comfort level. This paper presents a survey of system architectures and algorithms for end-to-end signal processing pipelines of neural activity on the hardware of such neural devices, including (i) on-chip signal pre-processing, (ii) spike-sorting on-chip or on embedded hardware and (iii) neural decoding on workstations. A particular focus for the hardware implementation is on low-power electronic design and artifact-robust algorithms with low computational effort and very short latency. For this, current challenges and possible solutions with support of novel machine learning techniques are presented in brief. In addition, we describe our future vision for next-generation BCIs.

| Used abbreviations |                                 | CIFF | Cascade of Integrators with Feed-Forward |

|--------------------|---------------------------------|------|------------------------------------------|

| AC                 | Alternative Current             | CL   | Competitive Learning                     |

| ADC                | Analog-Digital Converter        | CMOS | Complementary                            |

| AFD                | Aligned first derivative        |      | Metal-Oxide-Semiconductor                |

| ASIC               | Application-Specific Integrated | CPU  | Central Processing Unit                  |

|                    | Circuit                         | CNN  | Convolutional Neural Networks            |

| ASO                | Amplitude Slope Operator        | DAC  | Digital-Analog-Converter                 |

| AT                 | Amplitude Thresholding          | DBS  | Deep Brain Stimulation                   |

| BCI                | Brain-Computer-Interfaces       | DC   | Direct Current                           |

| CAR                | Common Average Reference        | DSL  | DC Servo Loop                            |

| CAOM               | Cluster Accept and Merge        | ECoG | Electrocorticography                     |

| CCA                | Canonical Correlation Analysis  | EDO  | Electrode Drift Offset                   |

|                    |                                 |      |                                          |

| EEG      | Electroencephalograph                                            |

|----------|------------------------------------------------------------------|

| EMG      | Electromyography                                                 |

| ENOB     | Effective Number of Bits                                         |

| EF       | Error Feedback                                                   |

| EOC      | End of Conversion                                                |

| ESN      | Echo State Network                                               |

|          |                                                                  |

| FE       | Feature Extraction                                               |

| FIR      | Finite-Impulse-Response                                          |

| fMRI     | Functional Magnetic Resonance                                    |

|          | Imaging                                                          |

| fNIRS    | Functional Near-Infrared                                         |

|          | Spectroscopy                                                     |

| FSDE     | First and Second Derivative Extreme                              |

| FPGA     | Field Programmable Gate Array                                    |

| GANs     | Generative Adversarial Network                                   |

| IIR      | Infinite-Impulse-Response                                        |

| KF       |                                                                  |

|          | Kalman Filter                                                    |

| KLDM     | Kullback-Leibler Divergence                                      |

|          | Minimization                                                     |

| LSB      | Least Significant Bit                                            |

| LFADS    | Latent Factor Analysis via Dynamical                             |

|          | Systems                                                          |

| LSTM     | Long Short-Term Memory                                           |

| MA       | Mean Absolute                                                    |

| MAD      | Median Absolute Derivation                                       |

| MEG      | Magnetoencephalography                                           |

| MCU      | Microcontroller                                                  |

|          |                                                                  |

| MSB      | Most Significant Bit                                             |

| MEA      | Microelectrode Array                                             |

| NEO      | Nonlinear Energy Operator                                        |

| NS-ADC   | Noise-Shaping ADC                                                |

| NTF      | Noise Transfer Function                                          |

| LFP      | Local Field Potentials                                           |

| OSR      | Oversampling Ratio                                               |

| OTA      | Operational Transconductance                                     |

|          | Amplifier                                                        |

| PCA      | Principle Component Analysis                                     |

| PDAC     | Peak Detection with Area                                         |

| 12110    | Computation                                                      |

| PVT      |                                                                  |

|          | Process, Voltage and Temperature<br>Recurrent Exponential-Family |

| rEFH     | - ·                                                              |

|          | Harmonium                                                        |

| ReFIT-KF | Recalibrated Feedback                                            |

|          | Intention-Trained KF                                             |

| RMS      | Root-mean-square                                                 |

| RNN      | Recurrent Neural Networks                                        |

| SAR      | Successive Approximation                                         |

| SDA      | Spike Detection Algorithm                                        |

| SFS      | Salient Features Selection                                       |

| SNN      | Spiking Neural Networks                                          |

| SNR      | Signal-to-noise ratio                                            |

| SVD      | Singular Value Decomposition                                     |

|          |                                                                  |

| SVM      | Support Vector Machines                                          |

| TM       | Template Matching                                                |

| Q-RNN    | Quasi Recurrent Neural Network                                   |

| VCM      | Common-Mode Voltage                                              |

| VKF      | Velocity Kalman Filter                                           |

| WD       | Window Discrimination                                            |

| ZCA      | Zero-Phase Component Analysis                                    |

|          |                                                                  |

#### 1. Introduction

Neurodegenerative diseases and injuries of the nervous system result in a reduction in the quality of life of patients. For many of these diseases, there are currently no long-term cures or treatments available. Today, neural devices can relieve symptoms and substantially increase patients' quality of life.

- Patients with Parkinson suffer from uncontrollable tremors, leading to significant restrictions in everyday movements. One treatment option is the deep brain stimulation (DBS) of the midbrain, in which dopaminergic neurons in the substantia nigra are stimulated electrically to recover motor control and reduce tremors [97].

- Patients with Retinopathia pigmentosa go blind in the long term due to the death of the photosensitive cell layers. Retinal implants with recording and stimulation capabilities can be used to restore sight by translating a data stream from an external camera into neural signals of the retina via electrical or optical stimulation [45].

- Spinal cord injuries can often cause severe paralysis which leads to restricted freedom of movement. By recording the activity of motor neurons in the brain, it is possible to predict movement intentions and control an exoskeleton [50] or a prosthesis [33].

- Patients with severe paralysis or cognitive disorders can also suffer from speech impairments, resulting in social isolation and a strong reduction in their quality of life. Here, brain-computer interfaces (BCIs) in the motor cortex can be used to record neural population activity and directly decode intended speech or handwriting patterns [138].

In all of these cases, a reliable and real-time closedloop signal processing of neural activity is necessary. In addition, a deeper understanding of neural information coding in different brain structures is required to further optimize decoder techniques. This would enable improved recognition of movement intentions or speech patterns to control an actuator or enhance targeted neurostimulation for haptic feedback or restoration of impaired sensory. To allow the seamless integration of such approaches into regular daily life advances in the implementation of endto-end processing pipelines and AI-powered decoding techniques for on-implant and wearable neural devices and BCIs are needed. With increased number of electrodes it is necessary to move the processing to the brain, because sending all digitized raw data from all electrodes would damage the tissue due to the needed transmission power. Thus, the number of features should be reduced as much as possible. Therefore, the main challenge is to transfer the methods from a remote processor to resourcerestricted hardware platforms, like an applicationspecific integrated circuit (ASIC) which have the highest power efficiency and the highest resourceoptimization. There, the algorithm have to be optimized on their power consumption, computational resources (memory, area) and latency. Thus, the memory and computational effort have to be minimized to fit on small devices with low power techniques. In addition, the algorithms need to be adaptable to allow robust performance over long time scales.

To achieve high accuracy and long-term robustness during runtime, sophisticated signal processing algorithms must be used which can be supported by state-of-the-art machine/deep learning techniques, A neural decoder is then used to isolate the relevant information in the biological neural network. Depending on the neural structure, different decoder techniques are required. Also, neural decoders can be used for adaptive or closed-loop stimulation to adjust the stimulation parameters during runtime to induce specific neural response patterns [71].

This survey paper provides an overview of system architectures and techniques for achieving a signal processing in BCIs by using penetrating microelectrode arrays (MEA). Here the techniques on different hardware platforms (workstation, embedded, onchip) of the end-to-end pipeline are discussed, from the analogue pre-processing stage with recording the neural input, spike sorting with spike detection, framing, feature extraction and clustering through to decoding movement intentions. The structure of this review is as follows: Chapter II explains the neural input, the pipeline and the corresponding requirements for the hardware implementation in more detail. Chapter III mentions methods for analogue processing with a focus on quantisation. Chapter IV covers neural signal pre-processing with spike sorting. Chapter V presents methods for neural decoding of motion intentions and chapter VI gives a brief outlook on future work.

#### 2. Concept of an end-to-end BCI

This section introduces the basics of neurosignals and the steps of a neural signal pipeline using in invasive BCIs. Therefore, this section is divided into (a) characteristics of detectable neurosignals, (b) a high-level description of a possible distributed system architecture of a neural signal processing pipeline and (c) an overview of the corresponding challenges and design requirements. This knowledge is still necessary for the next sections. Also, we also discuss two operation modes, offline versus online processing and their use cases.

#### 2.1. Characteristic of neural signals

Brain activities can be captured via invasive technologies like penetrating microelectrode array (MEA), e.g. in the motor cortex [125]. From recording extracellular neural activities, two important biosignal features are available on each electrode channel: Local field potentials (LFP) and action potentials (or spikes). The LFP is the recording signal of the constructive superposition of many neuronal activities inside the neural tissue. Typical characteristics

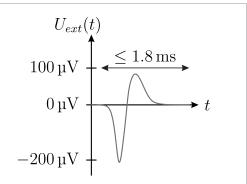

**Figure 1.** Timing of an extracellular spike waveform recorded from one channel of the invasive microelectrode array.

of this signal are peak-to-peak amplitudes  $\hat{U}_{pp}$  in the mV-range with low-frequency reactions in the time domain ( $\hat{U}_{pp} \leqslant 10\,\mathrm{mV}, 0.2\,\mathrm{Hz} \leqslant f \leqslant 200\,\mathrm{Hz}$ ). Spike activity serve as a stimulus transmission between individual neurons and are used for information transmission in neuronal networks ( $\hat{U}_{pp} \leqslant 500~\mu\mathrm{V}, 100\,\mathrm{Hz} \leqslant f \leqslant 7\,\mathrm{kHz}$ ). Figure 1 shows an example of a spike waveform from extracellular recordings. Such types of spikes have typical values peak-to-peak amplitude up to 300  $\mu\mathrm{V}$  within a time window range between 1.2 ms and 1.8 ms.

In general, the spike shape depends on several factors of (i) electrode-tissue behaviour  $\underline{H}_{\text{tissue}}$  (healthy of the tissue, distance between electrode and neuron), (ii) impedance characteristic from the electrode, and (iii) characteristics of the analog preprocessing (noise, gain, filtering, input impedance). Formula (1) shows the input signal present at the preamplifier, which is the sum of (i) the noise voltage  $\underline{U}_n$  through tissue/electrode and electronics and (ii) the voltage of the extracellular activities  $\underline{U}_{\rm ext}$ . The extracellular input is attenuated with

$$\underline{U}_{\text{in,pre}}(t) = \frac{\underline{Z}_{\text{pre}}}{\underline{Z}_{\text{pre}} + \underline{Z}_{\text{elec}}} \cdot \underline{U}_{\text{ext}}(t) + \underline{U}_{n}(t). \quad (1)$$

Therefore, the shape of the measured waveform from one neuron should be similar to the last few waveforms except for noise. However, the waveform may change over time due to electrode movement resulting in changed tissue impedance [7].

Typical values from recordings MEAs, like the Utah array by Blackrock Systems or Neuropixels by University College London, have an electrode impedance  $Z_{\rm elec}$  in the upper k $\Omega$ -range (e.g. Neuropixels with 149 k $\Omega$  at 1 kHz [22]). What these MEAs have in common is that the electrodes have a high impedance and a diameter of a few  $\mu$ m. This is necessary in order to be able to record neuronal activity well with high-density probes. For achieving a high signal quality, it is important that the input impedance of the pre-amplifier is 10-times larger than the electrode impedance.

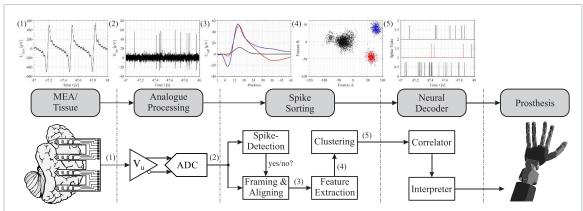

**Figure 2.** Illustration of an end-to-end neural signal processing pipeline from sensing the input from by multi-electrode array (MEA) over the analogue processing, the spike sorting as neural signal pre-processing and the neural decoding for readout the movement intentions from the motor cortex to control a prosthetic hand.

#### 2.2. Signal processing pipeline

In processing the spike activity of the extracellular recordings, the activities from multiple neurons that are close to the same electrode are often measured together. Spike sorting techniques are therefore used to detect and isolate neural signals from individual cells. This is done by extracting various features from the measured input signal, such as the shape and magnitude of the spike waveform, and then clustering the spikes that originate from different neurons. When electrodes are placed nearby (< 50  $\mu$ m distance) the same spikes can also be recorded by multiple electrodes, strongly facilitating clustering performance by taking into account the spread of the spike waveform across recording sites [93]). The amount of recorded neurons strongly depends on the recorded brain region. For example, 26-47 neurons can theoretically be recorded within a radius of 50  $\mu$ m around each electrode tip of the Utah array in the primary motor cortex in monkeys (neuron density varies from 50 000-90 000 neurons per mm<sup>2</sup> [144]) and even higher neuron density (300 000 neurons per mm<sup>2</sup>) can be found in the rat hippocampus [40]. However, due to tissue perturbations upon electrode insertion and theoretical limitations in isolating low-magnitude spikes, the number of correctly identified neurons is usually limited to 8-10 neuron units per recording site [89]. Ideally, spike clusters map to individual neurons but in reality, the spikes of multiple neurons with weaker signals can be indiscernible and are therefore often combined in the same cluster [102]. The identified clusters are therefore usually described as multi- or single-unit activity, to indicate how likely they are to reflect the activity of a single neuron [93]. The clustering output results in a so-called spike train, a sequence of time points where spikes from a given cluster are detected.

Figure 2 presents a signal chain for processing spike activities within an end-to-end BCI or modern experimental tools, like Utah-Array [124],

NeuroPixel probes [22] or NeuraLink's BCI-system [74]. In the following, the different steps of processing the bitstream of high-density MEA systems like NeuroPixels 2.0 (385 electrodes) are presented.

Analogue processing: All electrodes of the implanted MEA are connected to the recording front-end of the implant, in which all signals are first passed through the pre-amplifier, which removes some of the unwanted disturbances (e.g. movement artefacts, electronic noise) and the low-frequency LFP by bandpass filtering. Subsequently, the filtered spike activity can be digitized by an ADC with oversampling and noise-shaping to reduce the quantization noise of the ADC (signal in figure 2(2)). This raw data is sent telemetrically to a remote processor device [100]. For transmission of the raw data, high data rates in the upper MBit/s range are needed, which requires a high data transmission bandwidth and leads to high energy consumption. For example, the data rate per channel is in a range of 0.43 Mbit s<sup>-1</sup> (NeuroPixels, 163.8 Mbit s<sup>-1</sup> with 384 electrodes at 10-bit and 30 kHz) and 0.48 Mbit s<sup>-1</sup> (Blackrock Cerebus combined with the Utah array, 184.8 Mbit s<sup>-1</sup> with 96 electrodes at 16-bit and 30kHz) by using external data acquisition system. With an implantable data acquisition system for the Utah array, the data rate is reduced to 0.16Mbits<sup>-1</sup> [39] which provides long-term stable recording and strongly reduces energy consumption [16].

**Spike sorting:** The generated bitstream is preprocessed to reduce noise, artefacts, and cross-talk between recording channels. The resulting signal will be fed into the spike sorter pipeline. At this point, via a spike detection algorithm, a spike frame with the spike shape is captured from the bitstream (example in figure 2(3)) and processed in the next stage in order to determine the spike train. The spike

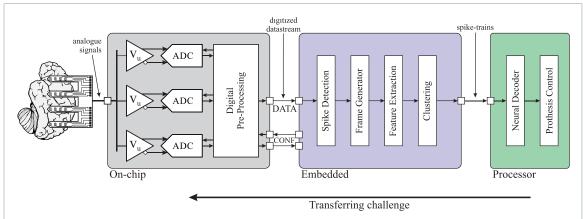

**Figure 3.** Illustration of the neural signal processing of the end-to-end BCI from system point-of-view in which the pre-amplifier has a voltage gain  $v_u$  and the analogue digital converter (ADC) for on-chip processing.

sorter is responsible for separating different neuronal responses from each other and from non-neural signals for each electrode usually implemented via feature extraction (FE) and clustering (example in figure 2(4)). In this process, specific characteristics (e.g. signal area, mean values, eigenvalues) are determined in a very computationally intensive way, and subsequently applied for clustering or classification to enable separation of spiking signals from individual neurons. To each detected time point of a spike frame, the corresponding cluster or classification number (spike-identifier) is determined to generate a spike tick (example in figure 2(5)). From the bitstream, a sequence of spike times from individual units is generated which serves as the input to a neural decoder.

**Neural decoder:** The resulting spike sequences from different neurons are then sent to the neuronal decoder, to allow the interpretation of movement intentions or responses to external stimulation from the neural activity. Another task of the decoder is that the detected spike frames can be assigned to the biological neuron type via a database to adapt the function of the existing neural structure. In addition, for long-term robust signal processing, several sensor inputs can be combined, e.g. EEG, ECoG, and LFP.

#### 2.3. System design and requirements

The used modules of the end-to-end BCI pipeline from the analog processing to the neural decoder can be understood as a modular system. In each stage, different methods can be chosen or cascaded to perform spike sorting and interpret the resulting neural signals. Each module impacts the performance parameters like accuracy, latency, computational effort, and total power consumption. For example, integrating the spike sorter into a wearable platform or ASIC could impair the sorting accuracy but significantly reduce the data rate by up to 600-fold per channel by directly transmitting spike trains instead of raw data bitstream. Moreover, integrated spike

sorting strongly decreases the latency, and power consumption of closed-loop applications. This survey paper gives an overview of these modular methods for performing spike sorting on different hardware systems. Figure 3 shows an example of a state-of-theart end-to-end BCI which also describes the trend of transferring all necessary algorithms from the remote processor to the on-implant electronic. This can be done in three stages. Firstly, they are developed on workstations with high computational power and full data quality (Datatype: float, high sampling rates, ...). Secondly, the methods are optimized for a wearable device with low computational power and quantized input. Finally, more power-, memory- and latency optimizations take place in order to implement these methods into an ASIC for in-body neural devices. For a unique comparison, we distinguish where the calculations are performed because the position of the computing platform favours different hardware. Thus, we distinguish between (i) on-implant electronics, usually ASICs, (hereinafter referred to as on-implant), (ii) an on-body wearable device, usually wearable computing platforms like MCUs and FPGAs, (referred to below as wearable), and (iii) a remote processing workstation (hereafter called remote processor). Also, we differentiate between ii.a) data processing in real-time (online) or ii.b) data analysis after measurements (offline). In the future, to increase patients' life quality, the end-to-end BCI pipeline should run on implanted hardware or wearable hardware. Therefore, this paper has three main contributions.

- Classification of the used analogue processing for digitizing neural activity.

- Classification of spike detection, feature extraction and clustering algorithms for on-implant online spike sorting.

- Share our vision on the future of on-implant online spike sorting. Focus on the transition from remote to wearable to on-implant online spike sorting.

Explanation of system architectures for neural signal processing in invasive BCIs.

The pipeline must be robust against environmental changes which include artefacts from muscle activity or electrical stimulation, modulation of signal shape due to bursting spike activity [18, 81] or electrode drift. The electrode drift changes in the signal shape due to physical movements of the electrode in the tissue. Some micrometers leads to a significant drop of the amplitude.

#### 3. Digitization of neural input

The first step for invasive BCIs is to digitize the input signal to enable neural signal processing, like spike detection or sorting, in digital manner. Such a recording front-end consists of analogue circuit and the design is crucial for the whole signal processing pipeline in wearable systems. The design choices have a huge impact on the signal quality and integrity. Thus, we discuss each component of recording front-end in detail with the related requirements.

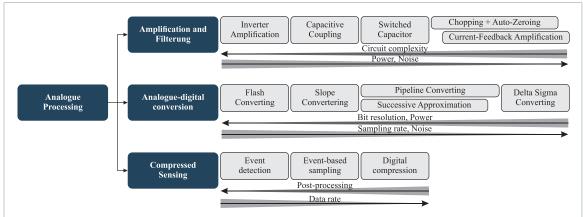

The analogue front-end of neural recording units can be divided into three modules: (i) Amplification and Filtering, (ii) Analogue-digital conversion and (iii) Compressed sensing. The last case includes other pre-processing techniques for artefact suppression and data-rate reduction which is discussed in the spike sorting chapter. At the end of this section, the topologies of recording front-ends for different MEAs is presented (low- vs. high-density). Figure 4 shows these modules including the relevant circuit topologies and methods, which is described in the following. In general, the research goal is to work on new system topologies in which there is an optimum between small chip area, low power consumption and low effective input noise with simultaneously high accuracy and artefact suppression for the following pipeline stages.

#### 3.1. Analogue amplification and filtering

The module of amplification and filtering in figure 4 shows the related topologies. These pre-amplifiers have a band-pass filter characteristic in order to capture the neural input signal with the following requirements.

- Input impedance: To avoid the signal attenuation and damages at the electrode, the input impedance of the pre-amplifier should be 10-times larger than the electrode impedance to prevent charge transfers into the electrode which causes an accelerated electrode ageing ( $\geq 10 \,\mathrm{M}\Omega$ ).

- **Input noise:** To achieve high signal-to-noise ratios, the effective input noise of the pre-amplifier  $\underline{U}_n$  should be less then 5  $\mu$ V in the filter bandwidth in order to have the electrode noise as a primary source.

• **Input offset:** The pre-amplifier should be robust against the electrode drift offset (EDO) and stimulation artefacts which moves in the range up to 100 mV [12].

For this, a simple amplifier can be realised with a one-transistor inverter, but this topology is highly sensitive to process, voltage and temperature variations (PVT). Also, the output voltage is very sensitive against changes on the power supply and it requires a DC voltage at the input for setting the working point which is not recommended for use in neural recording of high-density MEAs.

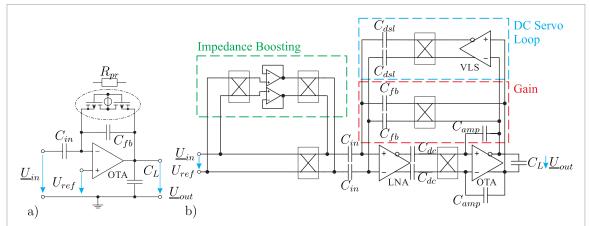

The impact of these drawbacks can be reduced by using feedback circuits with operational transconductance amplifier (OTA) combined with differential signal processing. A often-used topology is the capacitive-coupled amplifier with the circuit diagram in figure 5(a). The midband gain is set over the capacity ratio  $C_{\rm in}/C_{\rm fb}$  and the corner frequency of the low-pass  $f_{HP}$  can be adjusted via the transconductance of the OTA  $g_m$  and the capacity load at the output  $C_L$ . To achieve a high-pass corner frequency in the lower Hz-range, high ohmic resistors in the  $T\Omega$ range are realized with pseudo resistors but they are highly PVT-sensitive [34]. In [20], a tuneable version is presented which allows to modify the highpass corner frequency to the desired value and is PVTrobust. In general, these amplifier topologies is often used for low-power applications due to low charging current of the high-impedance capacities. This results in reducing the bias current of the OTA to values in the nA-range in order to save power and chip area by using the  $g_m/I_D$  design methodology. The final OTA design depends on the desired noise characteristic which requires large transistor areas of the load and the differential stage in order to reduce the level of thermal and 1/f noise. The disadvantages of this amplifier is that (i) no DC input processing is possible and (ii) input impedance ( $\underline{Z}_{pre} = (2\pi f C_{in})^{-1}$ ) in the lower M $\Omega$ -range are available. This range is not sufficient to avoid a signal attenuation and a charge transfer into the tissue.

To handle DC voltages, chopper-stabilized amplifiers are more effective due to the modulation and the demodulation of the input signal. Chopping takes place via polarity-shifting switches that perform amplitude modulation with a square wave function via a digital clock. This causes a conversion from DCto AC-signal and the other way around. Here, the carrier frequency is at the chopper frequency  $f_{ch}$ . In order to minimize the output offset, the duty cycle of the digital clock should be exactly 50%. At the output of the amplifier, the signal is a DC signal again and parasitic properties of the OTA (e.g. noise, offset, ...) are modulated up to  $f_{ch}$  which can be removed by a low-pass filter. This results in fewer design contraints of the OTA (smaller chip area and power consumption with the same noise characteristics)

**Figure 4.** Overview of the module Analogue Processing for digitizing and pre-processing the neural input with comparing different methods of (i) amplification and filtering, (ii) analogue-digital conversion and (iii) compressed sensing on common metrics (High — Low).

**Figure 5.** (a) CMOS circuit of a capacitive-coupled amplifier with pseudo resistance settling a low-frequency high-pass corner frequency (single-ended) - (b) CMOS circuit of capacitive-coupled chopper amplifier with input impedance boosting at the input and DC servo loop (DSL) in the feedback.

in order to compensate the increased circuit complexity. An auto-zero amplifier should be added in order to improve the noise properties at very low frequencies [90]. The disadvantages of choppers are that (i) the input impedance is even lower than with capacitive-coupled amplifiers  $(f_{\rm ch} > f_{\rm sig})$  [60, 101] and (ii) due to the switching of the parasitic capacities from the switches, the charge current will generate voltage ripples on the output. The impact of (ii) can be reduced by using small transistors and reducing the chopping frequency  $f_{\rm ch}$  [25].

Figure 5(b) shows the CMOS circuit diagram of the chopper-stabilized amplifier for neural application [79, 91]. Chopping takes place around the first low-noise OTA stage with a settable gain over the ratio  $C_{\rm in}/C_{\rm fb}$ . A DC servo loop (DSL) is used in the feedback for applying a high-pass filter characteristic in order to eliminate the electrode drift offset (EDO) in the range of  $\pm 100\,\rm mV$ . The desired corner frequency depends on the 0 dB-frequency ( $(R_{\rm pr}\,C_{\rm int})^{-1}$ ) of the integrator and the integrator gain  $C_{\rm dsl}/C_{\rm in}$ . The low-pass filter corner frequency is set by the OTA conductance  $g_m$  and the load capacity  $C_L$  at the output.

The capacity  $C_{\rm DC}$  adds an high-pass filter for blocking charge currents due to the active DSL in order to attenuate the ripples on the output voltage up to 60 dB [11]. A further method to reduce output ripples is to shift a time delay to the demodulator clock signal by the time constant of the ripple.

The module of impedance boosting tackles the problem of the low input impedance from previous topologies. A boosting can be achieved by adding (i) a positive feedback loop and (ii) an impedance buffer. In the following, the two methods are discussed briefly. The positive feedback loop is implemented easily by an additional path from the gain feedback to the input (left connection of the input capacity  $C_{\rm in}$ ) which decreases the effective input capacity by (1 - $C_{\rm pfb}/C_{\rm fb}$ ). The ratio  $C_{\rm pfb}/C_{\rm fb}$  must be nearly zero in order to increase the input impedance and to avoid instability [109] which can not be avoided absolutely due to the PVT changes. To prevent this instability problem, the method of impedance boosting can be used. Here, an additional voltage buffer path is included at the input in order to charge the input capacity for certain time points of the chopping [100].

This requires a changing of the modulator clock signal in which a dead time between each clock edge is added. During this dead time, the input capacity are charged from the buffers and in the rest time from the electrode input. With this technique, the initial input impedance can be increased exponentially by the ratio of the chopping period  $T_{\rm ch}$  to the dead time  $\Delta T$  [109]. The bottleneck of this method is that using two different voltage buffers occurs to different offset voltages on both paths. This leads to ripple artefacts on the output due to the DSL. A method to compensate this is reported in [100] on which a fully-differential buffer with with switching properties is used. The benefits are a reduction of the offset voltage from mVrange to  $\mu V$ -range and the offset on both signal parts are identical.

A further reduction in chip area and noise properties of chopping amplifiers can achieved by changing the amplification over the capacity feedback to a current feedback [109]. Therefore, also the input capacity is lower then capacitive-coupled chopper amplifiers which leads to reduced output ripples due to less charge current at the input. In addition, a decoupling between gain and input impedance is available.

#### 3.2. Analogue-digital converter

After amplification and filtering of the neural activities, these signals can be converted from the analogue domain into the digital domain for further processing within the end-to-end BCI. Figure 4 shows different analogue-digital conversion (ADC) techniques for neural application. In general, after the conversion the digital signal is presented over the ratio of the input signal to the voltage of the least significant bit (LSB) which depends on the applied voltage reference  $\Delta U_{\text{ref}} \ (= U_{\text{refP}} - U_{\text{refN}})$  and the ADC bit-resolution N. The residual voltage  $U_{\rm in}$  –  $U_{\rm ADC}$  is a converting error or defined as quantization noise. For ideal converters, it moves in the range of  $\{-1/2,1/2\} \cdot U_{LSB}$ . This has an impact on the effective input noise of the whole recording pipeline via (2).

$$U_{n,\text{eff}} = \sqrt{U_{n,\text{elec}}^2 + \left(\frac{U_{n,\text{amp}}}{v_u}\right)^2 + \left(\frac{U_{n,\text{ADC}}}{v_u}\right)^2}$$

(2)

To achieve a total effective input noise of  $20~\mu V_{\rm eff}$  with an electrode noise of  $18~\mu V_{\rm eff}$  and an amplifier noise of  $5~\mu V_{\rm eff}$ , the input-related LSB voltage must be lower then  $7.74~\mu V_{\rm eff}$ . This can be achieved with an 15-bit ADC at a reference voltage  $\Delta U_{\rm ref}$  of  $1.8~{\rm V}$  and a gain  $v_u$  of  $20~{\rm V/V}$ .

Figure 4 shows different techniques for analoguedigital conversion. Regarding to these estimation with the required bit resolution at sampling rates up to 3 kHz with an high energy-efficiency, only the methods of successive approximation (SAR) and delta sigma converting  $(\Delta\Sigma)$  are suitable for the neural applications applications. In the following, these two topologies are presented shortly.

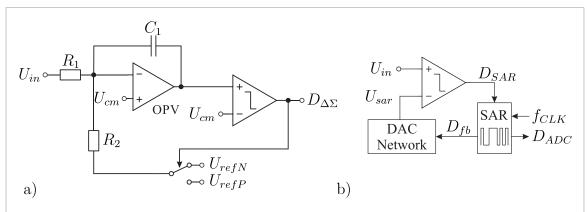

Figure 6(a) shows the setup of a first-order  $\Delta\Sigma$ converter. It integrates the difference between the input signal and the feedback signal over time. The corresponding output voltage is compared with a reference voltage by using a clocked comparator to generate a digital 1-bit bitstream  $D_{\Delta\Sigma}$ . This digital signal updates the feedback voltage between the reference voltages  $\{U_{\text{ref}P}, U_{\text{ref}N}\}$  of the ADC. This effects in a regulation of the difference voltage on the input to zero over the running time. In order to extract the analogue information from the pulse-density bitstream, a low-pass filtering in the digital domain is applied. This structure allows high bit resolution up to 24-bit with high accuracies, but this requires a very high oversampling rate (OSR) in combination with a decimation filtering and it needs a high-order modulator with multiple feedbacks to avoid stability problems. The big advantage of these structure is, that the integration of the residual voltage  $\Delta \Sigma$  causes a noise transformation, where the quantization noise is shifted from the low frequency range to higher frequencies. Due to the low-pass filtering, the impact of the shaped noise is suppressed. However, such converters have a high static power consumption and are usable in application for low sampling rates.

Figure 6(b) shows the setup of a SAR-ADC, consisting of a comparator, a capacitive digital-toanalogue converter (C-DAC) to generate an internal reference voltage  $U_{\rm sar}$  and the SAR logic. The advantages of the SAR ADC are that the power consumption is fully dynamic, the circuit complexity is lower and the design can be transferred quickly to smaller technology nodes. The disadvantage is that the resolution depends on the SAR logic and the bit resolution of the C-DAC. The SAR logic performs the binary search for driving the binary-weighted capacitances of the C-DAC to generate the digital output  $D_{ADC}$  in N conversion steps. The aim of the binary search is, that the difference between the input signal  $U_{in}$  and the generated voltage signal  $U_{\text{sar}}$  is closely to zero. This search is starting with the most significant bit (MSB) and it is updated from the result of the comparator from each conversion step. Control techniques of the binary search like the splitting the MSB-arrays and commonmode voltage (VCM)-based recovery [63] reduces the energy consumption per conversion with 99,53% and it leads to an area reduction up to 75% for the same bit-resolution.

Nowadays, the integration of the noise-shaping method into SAR ADCs is possible which results into a higher effective bit-resolution, reduced quantization noise (increased SNR) [48] and it enables an error-reduction method. This type of converters combine the benefits from  $\Delta \Sigma$ - (low noise) and SAR ADC (higher speed, high energy efficiency, low circuit complexity), which is a potential candidate for edge computing in Internet of Things- (IoT)

Figure 6. Electrical setup of (a) a delta-sigma analogue-digital converter (ADC) and (b) a successive approximation (SAR) ADC.

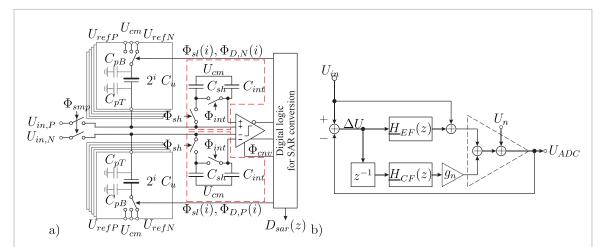

Figure 7. (a) CMOS circuit of the first order noise-shaping SAR ADC (extension in red lined box) with 4-input dynamic latch comparator - (b) Signal flow diagram for a EF and CIFF NS SAR-ADC with a 4-input comparator and a signal processing for the feedbacked residual voltage  $\Delta U$  (without digital decimator and low-pass filter at the output).

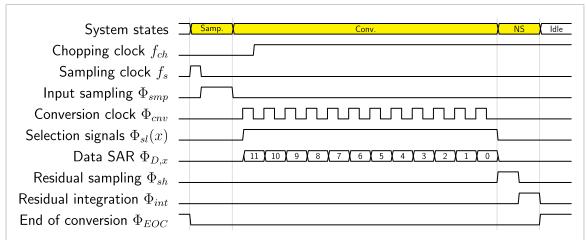

Figure 8. Timing diagram of the Successive Approximation Analog-Digital Converter (SAR ADC) control with noise shaping of the residual voltage  $\Delta U$  after each conversion step.

and medical applications. In the following, the circuit implementation of a noise-shaping SAR-ADC (NS-ADC) is presented shortly. The CMOS circuit is shown in figure 7(a) with the corresponding timing diagram in figure 8 of the control signals. In general, the input signal can be applied to the top-plate and bottom-plate of the DAC capacities. The benefit of

the top-plate charging is that a higher linearity can be achieved due to the lower parasitic capacities from the fabrication point-of-view, but for input sampling the input switches must be bootstrapped in order to reduce the parasitic discharging of the transistor. Important for the chopping pre-amplifier is that the impact of chopper artefacts/ripples on ADC output can be reduced by shifting the transition of the chopper to the conversion phase. In this time duration, the pre-amplifier is disconnected from the ADC input via the bootstrapped switch [99]. The execution steps of one full conversion including noise-shaping (additional circuits in the red box) are described below.

- Sampling: The conversion starts with the incoming flag of the sampling clock signal. During the sampling signal  $\Phi_{smp}$ , the top-plates of the DAC-capacities are charged with the input signals  $U_{\text{in},P}, U_{\text{in},N}$  on each side against the voltage  $U_{\rm cm}$ .

- Conversion: During the conversion, the bineary search is performed for an *N*-bit ADC output in *N* conversion steps. The most significant bit (MSB) is decided directly in the first step over the sign of the voltage difference from the input signals. In the residual steps, the difference from the input signal and the reference voltage is generated in dependency of the results from the previous conversion steps via setting the capacities. The corresponding voltage shift depends data signal of each bit  $\Phi_{D,x}(i)$ of the active selection signal  $\Phi_{\rm sl}(i)$ .

- Noise-shaping: After the conversion, the residual voltage of the top-plate capacitances represents the error voltage of this ADC sampling event. This voltage will be stored on an additional capacitance  $C_{\rm sh}$  which modifies the comparator outputs of the next conversion phase.

- End of conversion (EOC): After N conversion steps, the data word  $D_{sar}(z)$  is determined and the signal  $\Phi_{EOC}$  is active during the idle time before the next conversion will be triggered.

For performing noise shaping, different types of processing the residual voltage are available: residual integration with a cascade of integrators with feedforward (CIFF) and residue compensation with error feedback (EF). Both methods requires the residual voltage  $\Delta U$  after a complete conversion. It builds up from the difference of the applied input voltage and the determined SAR output  $D_{\text{sar}}$  (see (3)).

$$\Delta U = U_{\rm in}(z) - U_{\rm LSB} \cdot D_{\rm sar}(z). \tag{3}$$

In CIFF NS-ADCs, the residual voltage is sampled during the phase  $\Phi_{sh}$  and integrated during the phase  $\Phi_{int}$  Via a switched capacity circuit. This signal will be applied to the second comparator input for the next conversion step in which the comparator decision will be slightly adapted with the gain  $g_n$ in order to shift the comparator noise  $U_n$  to higher frequencies and to compensate DAC mismatches/errors during the runtime. Figure 7(a) shows the CMOS circuit diagram and figure 7(b) shows the signal flow diagram of such a CIFF NS-ADC.

$$D_{\text{out}}(z) = U_{\text{in}}(z) + \frac{U_n(z)}{1 + g_n z^{-1} \underline{H}_{\text{CF}}(z)}$$

(4)

$$D_{\text{out}}(z) = U_{\text{in}}(z) + (1 - \underline{H}_{\text{EF}}(z)) \ U_n(z)$$

(5)

$$\rightarrow D_{\text{out}}(z) = U_{\text{in}}(z) + \underbrace{\left(1 - z^{-1}\right)}_{=\text{NTF}} U_n(z). \tag{6}$$

The effectiveness of the noise shaping depends on the transfer function of the integrator  $\underline{H}_n$  in the feedback. Formula (6) shows the digital output of the NS-ADC with the output result in which the noise transfer function (NTF) can be modified. With an ideal integrator  $(\underline{H}_n = (1 - z^{-1})^{-1})$  the NTF is transformed into a first order high pass order. An improvement can be achieved by increasing the order number and by changing the transfer function in order to fit an optimum between in-band noise and out-of-band noise with FIR-IIR filtering [134]. Modern implementations are still using passive integration and summation in order to achieve minimum power consumption and to have a scaling-friendly technology [133].

$$FoM_w = \frac{P_{lgc} + P_{dac} + P_{cmp}}{2^{ENOB} \cdot \max(f_s)}$$

(7)

$$ENOB = \frac{SNDR - 1.72dB}{6.02dB}$$

(8)

$$ENOB = \frac{SNDR - 1.72dB}{6.02 dB}$$

$$FoM_s = SNDR + 10 \cdot \log \left(\frac{GBW}{P_{tot}}\right)$$

(8)

Important key metrics for the ADC characterization are the Walden figure of Merit FoMw and Schreier FoM<sub>s</sub>. The Walden FoM in (8) describes the power efficiency of ADCs in dependency of power consumption for one conversion cycle  $\Sigma P_x$ , the effective number of bits (ENOB) and the maximum sampling rate. With NS-ADC, a minimum FoM<sub>w</sub> of 4.63 fJ/conv-step is achieved [118]. The FoM<sub>s</sub> in (9) includes the harmonic distortion and SNR to the speed and power consumption. Here, the highest value of 183 dB are accessible. These values are achieved with passive NS SAR ADC (CIFF) by using capacitive stacking for summation and dynamic floating inverting buffers for sampling the residual voltage [133].

#### 3.3. Compressing techniques

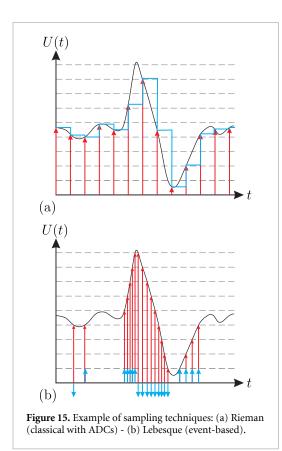

The last row of figure 4 shows some techniques for using compressed sensing are shown. In neural applications, an effective way to reduce the data rate is the introducing of the event detection which can also be used for event-based sampling. This can be done with the integration of an analogue spike detection, which is discussed in section 4.6.

Here, we want to mention the used compression technique in combination of an event detection in [73]. They present a method for robust readouts

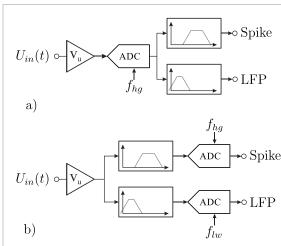

**Figure 9.** Different strategies in order to get spike activity and the low field potential from the neural input  $U_{\rm in}(t)$ : (a) Digital filtering - (b) Analogue filtering.

from massively parallel recordings with a data-rate reduction of 40x, in which each channel of the MEA has a single-slope ADC. The active readout of the neural event takes place if the value of the ADC output is outside of the estimated noise distribution. The reconstruction of the event takes place on a wearable device in order to reconstruct the spike waveform.

#### 3.4. Topologies of recording front-ends

This section presents different often-used approaches for neural signal processing. Figure 9 shows two recording front-end topologies for different kind of applications, in which the separation of LFP and spike activity is done with filtering in digital domain (a) or in the analogue domain (b).

The benefit of a) is, that the implementation is very resource-efficient, in which the electronic of these probes have only one pre-amplifier and one ADC per channel or time-multiplexed-ADC for *N* number of channels. The disadvantage is, that the dynamic range of the LFP is dominant and higher bit resolution are required for achieving a high resolution of the spike activity. These structures are used in the Utah-Array on the external headstage or neural probes with electrode depth control via electrode time-multiplexing [113].

The major change of structure in figure 9(b) is, that the splitting of the LFP and spike activity is done in the analogue domain with a second amplifier stage. Each line has its own ADC with different sampling rates and bit resolution. These topologies are used in high-density MEA approaches like the NeuroPixel [22] or in neural systems for ECoG applications [100]. The benefit is that the focus is on achieving high signal quality for both biosignals. This is effected at the cost of a higher power and space requirement.

In future, there is research on novel approaches to integrate amplification and filtering directly into the ADC structure (direct digitisation), so that the necessary chip and power consumption for high-density applications can be further reduced [52, 119]. Also, inference effects and crosstalk between the different channels can be reduced. Furthermore, new neural probes must be developed in which the pre-amplifier or the hybrid-ADC is directly placed at the electrode directly for avoiding long wire cables.

When an electrical stimulation front-end is also implemented in order to provide an information flow into the tissue, then a methods for suppressing stimulation artefacts must be included. During the stimulation phase, an absolute change in the electrode voltage in the upper mV range is available. Without any action, the pre-amplifiers go into saturation and a recording is after a long settling time possible again [11]. This effect can be reduced by using the (i) blanking, (ii) pole-shifting and (iii) adaptive substraction method.

With the blanking method, the input of the preamplifier is switched from the active electrode to a reference during the stimulation period. This method is not effective because small voltage differences such as the electrode offset and residual charge on the electrode from the stimulation artefacts can lead to saturation. A better method is the pole shifting method, in which the high-pass corner frequency of the pre-amplifier is increased to high frequencies which results in a low total gain and the input of the pre-amplifier remains actively connected to the electrode [24]. The corresponding dead time is in the lower of  $\mu$ s range so that the responses can subsequently be recorded [98]. The adaptive substraction method tracks the stimulation-induced voltage change during the stimulation phase and adapts the pre-amplifier input in order to eliminate the artefact [104].

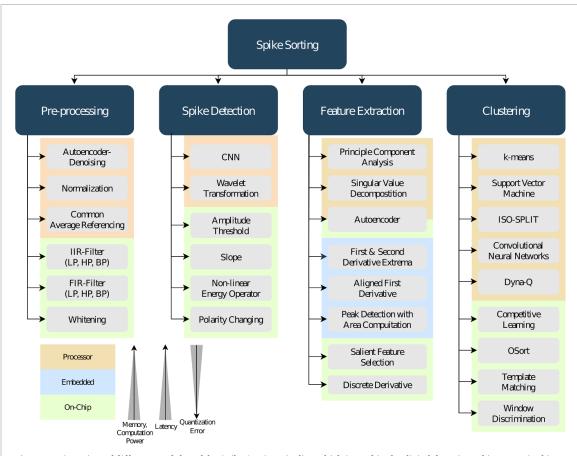

#### 4. Spike sorting

After digitization of the neural input from extracellular recordings, the raw data must be processed in order to detect spike activity and to perform spike sorting for separating several neuron activities in order to get a spike-train for further neural decoding. This processing step is important because it compresses the number of features for the neural decoding drastically. Figure 10 shows an overview of different methods for pre-processing, spike detection, feature extraction and clustering in order to build a modular spike sorting pipeline. Each of the presented techniques is crucial for deploying a online signal processing pipeline. Therefore, we classify the techniques into their target application of the hardware location (remote, wearable, on-implant). Building on these classes, we provide detailed information about needed system architectures. First, we present and discuss the methods for each step of spike sorting starting with pre-processing in section 4.1, the spike

**Figure 10.** Overview of different modules of the Spike Sorting Pipeline which is used in the digital domain and is categorised into the suitable hardware platform (Processor, Embedded, On-Chip).

detection and frame generation in section 4.2, the feature extraction methods in section 4.3, and the clustering approaches in section 4.4. Also, an overview of different system architectures for spike sorters and their use cases are explained in section 4.5.

#### 4.1. Pre-processing

In this section, we give an overview of the used preprocessing with a focus on filtering methods. They can be classified into three categories (i) frequencyspecific, (ii) channel-specific, and (iii) channeloverreaching.

Frequency-specific filters are used to reduce noise and suppress artefacts and local field potentials. This is usually implemented with a band-pass filter (LFP: 0.1–100 Hz, Spike: 0.1–7 kHz). These filters can be implemented as an IIR filter and a FIR filter. While FIR can only be implemented digitally, IIR can be implemented digitally and analogue. The disadvantage of using FIR filters in neural applications is that the frequency selectivity increases with higher orders. But latency and resource consumption also increase due to the feed-forward structure. IIR filters are easy to implement due to the feedback structure and the latency is quite low in the range of the sampling period. For all of these reasons, the IIR implementation is recommended inside the analogue

amplification stage and digital post-processing after quantization.

Channel specific filters are used e.g. for denoising neural input. This can be achieved by a deep learning method, called autoencoder [5, 46, 111]. The autoencoder is divided into an encoder and a decoder. In the encoder, the incoming data are reduced to minimal representation. In the decoder, the features are used to reconstruct the original data. The neural network is usually trained by using the difference, called loss, between the original data and the reconstructed data to find the best-fitting minimal representation. Noisy spikes from the same neuron share a very similar minimal representation and are therefore reconstructed close to each other. This approach shows in ECG applications an increased SNR of 20 dB [68, 108] and in neural applications with increased SNR up to 13 dB and minimal error compared to conventional methods [51, 96].

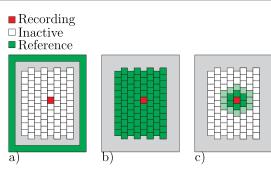

Channel overreaching filters use the spatial information provided by high-density probes for reducing background noise and artefacts. Common Average Reference (CAR) method and spatial whitening are often used digitally in spike sorting pipelines [64, 81]. Figure 11 shows the electrode configuration for different recording strategies. (a) shows the normal

Figure 11. Methods of suppression artefacts in extracellular recordings with high-density electrode arrays: (a) normal configuration—(b) global common average reference—(c) local common average reference with distance-based weights.

configuration, in which neural input of the active electrode (red) is recorded against the global reference (green). This setup does not use spatial benefits and is therefore fragile to environmental influences. In (b), global CAR is used. CAR extracts the global average of each reference electrode and subtracts it from the recording input. The suppression factor here takes a maximum value of 1 if the interfering signal is present on all channels and the SNR increases by  $\sqrt{N}$ with a number of reference electrodes considered. A)reduction of the suppression factor is reduced by channels that are defective (electrode, amplifier, ...) and thus do not allow the acquisition of signals. These channels can be detected by channel selection methods for extracting electrodes with non-neural activity [80] and neglected in the CAR and spike sorting pipeline. In (c), the local CAR algorithm is applied to allow for higher selectivity and further reductions in global and local artefacts like electrical stimulation. In addition, the Laplacian filter is used in EEG recordings for determining the reference from the neural input [127, 151]. The main difference between CAR and the Laplacian filter is that in Laplacian filter the input is weighted with the distance from the center electrode. Both methods achieves similar results.

Signal whitening is used to make signals of electrodes more independent from each other. This is useful for high-density spike sorters, that perform a single-channel spike sorting and merge the results afterwards. [18, 81] state that this drastically increased the performance of their algorithms. This is usually done by computing the covariance matrix on the electrode signals and then decorrelate the signals per channel by using matrix decomposition like the zerophase component analysis (ZCA). ZCA whitening is often used because of its computational efficiency. On a data set X with n-channels and m-samples a covariance matrix C is calculated with (10).

$$C = m^{-1} X \cdot X^T \tag{10}$$

$$W_{\rm ZCA} = C^{-1/2} \tag{11}$$

$$Y = W_{\text{ZCA}} \cdot X. \tag{12}$$

Afterwards, whitening matrix  $W_{ZCA}$  is determined via the inversion and squaring  $\Lambda$  with (11). Finally,  $W_{ZCA}$  is multiplied with its input X in order to the decorrelated matrix Y with (12). The computation of these channel-overreaching filters is done offline on a workstation and further research for hardware implementations is needed.

#### 4.2. Spike detection and frame generation

After the pre-processing, the neural events inside the raw data of neural spike activity have to be detected. The used spike detection algorithm (SDA) extracts spike events and the following frame generator cuts a window/frame from the spike activity data stream at the time point of these events. These frames are passed to the spike sorter. In the following, the different methods for SDA are discussed.

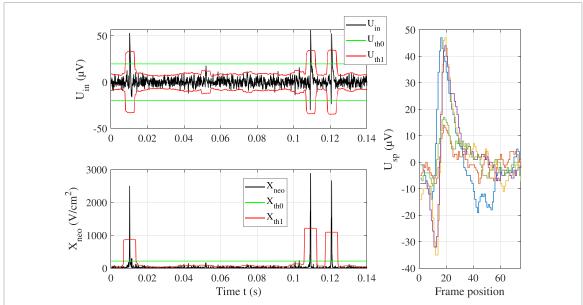

In general, the SDA needs a threshold value for detecting spike events in the bitstream. The easiest method is to use amplitude thresholding (AT) on the neural raw data. Whenever the signal crosses the set threshold, a spike frame with a pre-defined window length is generated. Figure 12 (Left) shows an example of different SDA methods.

$$X_{\text{th0}} = C \cdot \text{median}\left(\frac{|x_{\text{in}} - \overline{x_{\text{in}}}|}{0.6745}\right)$$

(13)

$$X_{\text{th0}} = C \cdot \text{median}\left(\frac{|x_{\text{in}} - \overline{x_{\text{in}}}|}{0.6745}\right)$$

$$X_{\text{th1}}(z) = \frac{C}{\sqrt{N}} \sqrt{\sum_{x=1}^{x=N} (x_{\text{in}}(z-x) - \overline{x_{\text{in}}})^2}$$

(13)

$$X_{\text{th2}}(z) = 1.25 \frac{C}{N} \cdot \sum_{r=1}^{N} |x_{\text{in}}(z-x)|$$

(15)

$$X_{\text{NEO}}(z) = x_{\text{in}}(z)^2 - x_{\text{in}}(z-k) x_{\text{in}}(z+k).$$

(16)

For thresholding, different methods like the median absolute derivation (MAD) in (13), the windowdetermined root-mean-square (RMS) in (14) or the mean absolute (MA) in (15) are used [107]. In general, with all thresholding methods, the statistical deviation of the noise is determined with an additional scaling value C, which is determined via hyperparameter analysis on the used data set in order to reach a trade-off between missing spikes (false negative) and detecting noise/artefacts (false positive). This scaling value is usually in the absolute range of 4 and 6. In these calculations, the mean value calculation can be neglected, as the mean value of the bandpass-filtered raw data should be close to zero.

For the hardware implementation, MAD is not sufficient due to the high computational effort and is only used in offline processing. In hardware, noise

**Figure 12.** Performing and results from the spike detection algorithm (applied on dataset [93]) - Top: Determining the threshold directly on input signal—Bottom: Performing non-linear energy operator (NEO) on input signal with threshold calculation—Right: Detected spike frames (72 points).

distribution is determined more by window methods, like RMS or MA.

The disadvantage of using AT is that this method is prone to noise. Therefore, especially for input signals with low SNR, the nonlinear energy operator (NEO), also called Teaser Energy Operator, with (16) at k=1 [72] is popular for processing neural inputs. This operator applies frequency-dependent amplification so that large signal changes are amplified and small changes like noise are damped. This gain effect comes from the window viewing method with multiplication, squaring and subtraction. The proposed SDA methods can be implemented in hardware easily [110, 130, 131].

The challenge in spike detection is, that the background activity is hard to detect due to a *SNR* below 0 dB. Here, some modifications of NEO-based SDA have been done in order to increase the sensitivity for detecting background activity. Therefore, methods like *k*NEO [72], MTEO [17], Wavelettransformation-based spike detection [78], integer coefficient filter [21] and amplitude slope operator (ASO) [152] are available.

kNEO introduces the tuning parameter k in order to arrange the frequency-selective property of NEO in order to minimize the false-positive rate due to noise influences. MTEO is the superposition of several kNEO approaches, in which the maximum of all operators is used as output. The integer coefficient filter works like a short-window convolution for capturing spike-like windows.

$$X_{\text{SDA}}(z) = 128 x_{\text{in}}(n) - 48 x_{\text{in}}(n-1)$$

$$-156 x_{\text{in}}(n-2) - 36 x_{\text{in}}(n-3)$$

$$+56 x_{\text{in}}(n-4) + 32 x_{\text{in}}(n-5). \quad (17)$$

Formula (17) shows the working principle without using any multiplier, but the parameters must be determined empirically with a hyperparameter optimization on the used data sets. This method achieves better accuracy results like NEO and AT with less computational effort [21].

The amplitude slope operator (ASO) [106, 152] reduces the computational effort by half compared to NEO by using only one multiplier, one subtraction and only two taps in the hardware. Formula (18) shows that a high amplification is achieved with a high slope and amplitude from the neural input  $x_{in}$ .

$$X_{\text{ASO}}(z) = x_{\text{in}}(z) \cdot [x_{\text{in}}(z) - x_{\text{in}}(z - k)]$$

(18)

$$X_{\text{ADO}}(z) = \text{abs}\left(x_{\text{in}}(z) - x_{\text{in}}(z - k)\right). \tag{19}$$

In addition, a higher accuracy has been shown in synthetic and real data [152]. The smoothing properties can be added by sweeping the tuning parameter k. An optimum is reported with k=4 at a sampling rate of 30 kHz [106].

It is also reported, that the detection accuracy of the SDA can be increased by smoothing the SDA output with the Hamming or Bartlett window of length 4k+1 in order to suppress noise influences. The best result is achieved by using a tuning parameter k of 4 [107]. Also, the accuracy is sensitive against the firing rate of the input spikes, in which the accuracy decreases from 60% to 25% at a SNR of 0 dB when the firing rate increases from 10 Hz to 200 Hz [107]. This error appears from the used thresholding method during the runtime. With the normalization of the input as pre-processing or the noise estimation as post-processing, this effect can be minimised [107].

From hardware perspective, the logic consumption of NEO, MTEO and ASO are higher compared to the AT method, resulting from the necessary number of multiplication units and logic cells for calculating the SDA and the threshold value. This results in higher complexity on hardware and less number of SDA channels in a high-density recording unit for neural implants and it gets more critical if smoothing filters with an additional FIR filter is used. In order to achieve a trade-off between i) high accuracy, high robustness against noise and artefacts, ii) low logic utilization and low power consumption, the Absolute Difference Operator (ADO) is recommended [153]. Formula (19) shows that only the absolute different of two input values is used with a settable delay window k. It applies a high-pass filter on the neural input in order to remove LFP and other low-frequency artefacts. Its hardware implementation needs only 300 logic cells per unit with an detection accuracy of 96% in recordings with a runtime over 200 days [153, 154].

With the SDA trigger output of the available neural spike event, the corresponding spike frame is generated for further spike sorting. Figure 12(right) shows an example with a window size of 72 samples which are stored in a FIFO memory buffer. The window length of the spike frame depends on the ADC sampling rate  $f_s$  and the refraction time of the spikes  $\tau_{\rm sp}$  ( $\approx$  1,6 ms). For example, the Data Acquisition System of the Utah Array from Blackrock Neurotech generates the spike frame within a window of 48 samples at a sampling rate of 30 kHz [128].

For some feature extraction methods, an alignment of spike frames is required in order to maximise cluster accuracy. The alignment of all spike frames is done at the window position at a delay time of 300  $\mu$ s with the maximum peak, minimum peak, maximum absolute peak or maximum slope [29]. This delay requires a time delay filter between the SDA input and the frame generator input in order to extract neural information before the active SDA trigger output.

Current research also shows interest in deep learning approaches for spike detection by combining convolutional neural networks (CNN) and recurrent neural networks (RNN) with long short-term memory (LSTM) cells. These large CNN+LSTM networks are quite complex to implement on FPGA and are more often designed for offline processing on workstations. Also, the authors of [128, 129] used CNN architectures. One architecture is designed for the discard of unstable channels. Another one is built for a background activity rejection. Both are servergrade solutions.

To sum up, the accuracy of spike detection depends strongly on the threshold method in order to achieve high accuracy. In determining the scaling value *C* for hardware execution, a trade-off must be found between the detection accuracy, the noise

sensitivity, the energy consumption of the logic and the computational effort of the whole spike sorter pipeline must be performed. Also, this value should be updated automatically during runtime.

#### 4.3. Feature extraction

On the captured spike frames, the feature extraction (FE) for performing clustering in order to determine the spike trains for neural decoding has to be done. This step is necessary due to the scaling of the computational complexity of most clustering algorithms exponentially with the number of features. To reduce this overhead, feature extraction algorithms can be used. They compute a set of features that represent the spike frame without losing critical information. Clustering can then be performed on these features instead of the full spike frame signal. FE algorithms can be divided into:

- i) matrix decomposition,

- ii) geometric,

- iii) important samples and

- iv) deep learning based FE.

In the following, we describe these in more detail, including information on how they are implemented, which limitations they have, and what promising ideas are not covered by current research.

Matrix decomposition based FE uses the idea to represent the input spike frames as a matrix and then decompose this matrix to find a smaller representation of it. Two approaches that use matrix decomposition are principal component analysis (PCA) [43, 88] and singular value decomposition (SVD) [41]. PCA is used for spike sorting, e.g. by [18, 128]). It first computes a covariance matrix C out of m input spike frames X with zero mean with (20). Then, a matrix decomposition on the covariance matrix computes its eigenvalues  $\Lambda$  and eigenvectors V with (21). The highest ones can be used to select and weight the most characteristic features (or principal components) P with (22). In contrast, SVD represents the input spike frames as a matrix and decomposes this matrix directly into singular values [81] with a unitary matrix Uand transposed eigenvectors V with (23). The principal components can also be computed when first computing SVD to calculate  $\Sigma$ . With (24)  $\Lambda$  can be computed. This is useful since computations on the covariance matrix can be ineffective for a high number of spike frames.

$$C = X^{T}X (m-1)^{-1}$$

(20)

$$C = V\Lambda V^T \tag{21}$$

$$P = X \cdot \Lambda \tag{22}$$

$$X = U\Sigma V^T \tag{23}$$

$$\Lambda = \Sigma^2 \left( m - 1 \right)^{-1}. \tag{24}$$

Both algorithms usually work offline on a workstation, since they need all spike frames as input. Online algorithms, like incremental PCA, are possible but have not been used widely for spike sorting, yet. Similarly, while these algorithms are computationally complex, hardware accelerators exist [8] and could be used for spike sorting. For on-implant, the computational power might be too high for hundreds of channels. Further research investigating the reduction of computational power is needed.

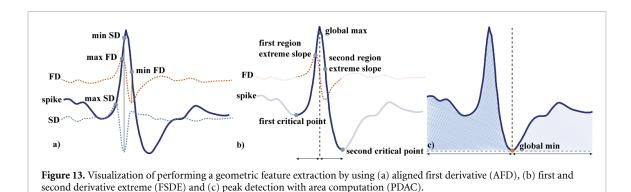

Geometric FE algorithms are using geometric calculable features. They can include the extreme point of the spike and its derivatives and areas under the curves. Aligned first derivative (AFD) [70] and first and second derivative extreme (FSDE) [84] are two examples. Usually, the FSDE algorithm should give the same features as AFD plus the features of the second derivative. Peak detection with area computation (PDAC) [13] calculates the areas under the curve and scales them with the difference between the minimum and maximum extreme. Figure 13 shows an example of the three mentioned methods. Alternatively, the authors propose to take the area above the curve divided by the maximum and scale them as well. All these geometric-based algorithms are unsupervised and are computed online, spike by spike. In addition, they are computationally inexpensive. Hence, it is convenient to implement them on FPGAs or ASICs, which makes them feasible for on-implant implementations. To our knowledge, no analogue implementation of one of those FE exists, but because of the low computational complexity. This could be feasible in combination with analogue spike detection heavily reducing the load of the ADCs.

Sample selection is another FE class. The idea is to reduce the features by only passing important samples to the clustering. To do so, an algorithm has to select the samples that distinguish the clusters most. Therefore the clusters need to be known in advance. This can be computationally expensive, but once selected the computational cost are almost nonexistent. To our knowledge, the only approach of this class is the salient features selection (SFS) proposed

in [116]. They have a training and inference phase. In the training phase, a shadow spike sorter computes the incoming spikes and creates labels for a set of spikes. A mean waveform of each cluster is computed. For each cluster, an optimizer selects the samples of the mean waveforms that distinguish the cluster most. These samples are the configuration, that can be used for inference. The training can be computed on different hardware than the inference. This allows a FE inference to be implemented on-implant. The inference is not adapting to changes automatically. Those could be updated by the shadow spike sorter. Therefore an online spike sorter could compute the mean waveforms on a sparse number of frames per channel. A salient feature optimizer could then recalculate the salient samples and update the inference unit. The computation power of the inference unit scales with the number of channels, while the shadow spike sorter only needs a multiplexer to swap between the channels.

Deep learning FE are the most recently used class. The most used architecture uses autoencoder [5, 46, 111]. Autoencoders showed success as FE in different application cases [77, 95]. They are usually self-supervised and benefit from supervised training mechanisms. The encoder minimizes the number of features which are usually directly used for the clustering. The neural network is usually trained by using the difference, called loss, between the original data and the reconstructed data to find the best-fitting minimal representation. However, this will just lead to a feature reduction which allows a good reconstruction and does not take into account the cluster separability with the generated features. Seong et al [114] targets this issue and proposes a modification of the loss function that takes clustering accuracy into account. This way the authors improve the features for better clustering accuracy. Radmanesh et al [96] proposes a modification of the input layer which punishes noise sensitivity. While the inference is already implemented on FPGAs and ASICs, the training is usually done on workstations and needs further optimizations to be implemented on FPGAs or ASICs.

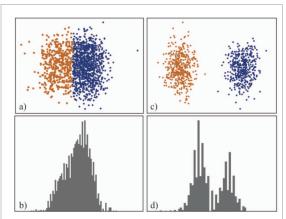

#### 4.4. Clustering

Clustering is used to distinguish between the different neurons due to the neural response. The goal of the clustering algorithm is to assign all detected spike waveforms from the same neuron to its own cluster. The clustering algorithms have to deal with electrode drift, which causes a slight change in the features of the clusters over time. In addition, they have to delete clusters, when neurons die and create new ones when a new neuron moves into the measuring range of the electrode. This allows classification into three classes, (i) Cluster initialization given, (ii) Number of clusters given and (iii) Adaptation through runtime. In addition, we distinguish between analogue and digital implementations, and offline and online processing.

(i) Cluster initialization given: These are online clustering algorithms and can be configured for singleor multichannel activity. They can be divided into two sub-classes; Optimized for workstations, and optimized for on-implant. Both require a training phase, which is usually implemented offline. After the training, the configuration is given to the clustering algorithm for online inference.

A deep learning approach for clustering uses CNNs. [57, 94] present an approach for online spike sorting for multi-channel activity. The CNN is a classifier with a fixed number of clusters and needs no previous feature extraction. However, a feature extraction could be beneficial for the reduction of computational complexity. For the training, ground truth is required. Once trained the network can be used for online inference. The CNN is usually executed on a workstation. Like the other CNNs, they could also be implemented for on-implant. The adaptation during runtime would be possible if another system is training on a sparse subset and updates the weights of the inference system.

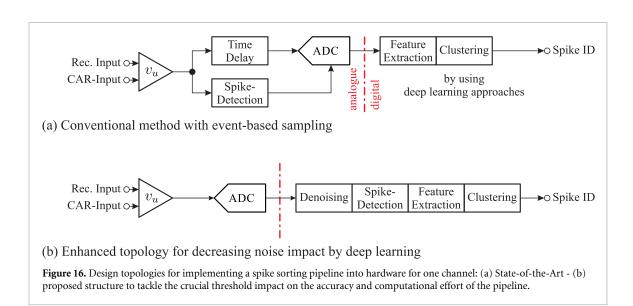

The next two algorithms, Template matching (TM) [81, 130] and window discrimination (WD) [29, 116] could be executed on-implant. TM is a classification algorithm used for online inference in the domain of spike sorting. The algorithm calculates the distance of the incoming spikes' features to all feature sets of each template. Either the algorithm matches the incoming spike to the closest template or additionally checks if the distance is below a threshold. If not the spike is discarded. The algorithm is computationally not intensive and can be implemented on-implant. The configuration of the templates can be done by another system. WD sets an upper and lower limit, called window, for each feature for each cluster. If each feature matches the window of a cluster, it is assigned to it otherwise the spike is discarded. This approach is even more efficient than template matching but also requires another system to generate the configuration for each window of each feature. [116] proposed this approach for on-implant spike sorting.