RESEARCH ARTICLE | FEBRUARY 20 2025

# **Cutoff frequency increase of gate recessed AlGaN/GaN MISHFETs with amorphous AIN insulator**

Peter Kordoš 💿 ; Dagmar Gregušová 🔀 📵 ; Martin Mikulics 📵 ; Hilde Helen Hardtdegen 📵

AIP Advances 15, 025028 (2025) https://doi.org/10.1063/5.0252024

# Articles You May Be Interested In

III-nitride metal-insulator-semiconductor heterojunction field-effect transistors using sputtered AION thin films

Appl. Phys. Lett. (January 2005)

High-power Si O 2/Al Ga N/Ga N metal-oxide-semiconductor heterostructure field-effect transistors

Appl. Phys. Lett. (September 2005)

High-power AlGaN/InGaN/AlGaN/GaN recessed gate heterostructure field-effect transistors

Appl. Phys. Lett. (April 2005)

# Cutoff frequency increase of gate recessed AlGaN/GaN MISHFETs with amorphous **AIN** insulator

Cite as: AIP Advances 15, 025028 (2025); doi: 10.1063/5.0252024 Submitted: 6 December 2024 • Accepted: 29 January 2025 • Published Online: 20 February 2025

Peter Kordoš, Dagmar Gregušová, Dagmar Gregušová

## **AFFILIATIONS**

- <sup>1</sup> Institute of Electrical Engineering, Slovak Academy of Sciences, Dúbravská cesta 9, Bratislava, Slovak Republic

- <sup>2</sup> Jülich-Aachen Research Alliance, Fundamentals of Future Information Technology, 52425 Jülich, Germany

- Ernst Ruska-Centre (ER-C-2), Forschungszentrum Jülich, 52425 Jülich, Germany

#### **ABSTRACT**

The RF performance of gate recessed MISHFET devices with an amorphous AlN layer was investigated by small-signal (S-parameter) measurements. They reveal current gain and unilateral power gain cutoff frequencies of 125 and 138 GHz, respectively. These device parameters were achieved for gate recessed MISHFET devices after applying a selective "step by step" etching T-gate formation procedure. The results indicate that the combination of an amorphous AlN dielectric layer with the gate recessed AlGaN/GaN MISHFET structures affects the RF performance in devices prepared for high frequency operation advantageously.

© 2025 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution-NonCommercial 4.0 International (CC BY-NC) license (https://creativecommons.org/licenses/by-nc/4.0/). https://doi.org/10.1063/5.0252024

The combination of a gate recessing procedure with a variety of oxide and insulator layers for III-nitride heterostructure based transistors has attracted growing attention during the last decade. 1-10 The main research focus was centered on gate recessing procedures with the aim of locally achieving the "full recessing state" of the barrier layers<sup>3–5</sup> and/or of reaching deeper, i.e., shallowly into the GaN region targeting the fabrication of "normally off" devices. The developments in this field were primarily driven by efforts to achieve device performance improvement and RF parameters comparable with those reached by "normally on" HFET and/or HEMT III-nitride based devices. Therefore, different III-nitride material layer systems and device layouts and architectures were studied and

Here, in this work, in contrast to the latest efforts and results published by other groups, 24-26 we focus our attention on the performance improvement of conventional AlGaN/GaN heterostructure HFET devices with a planar device layout. Although this material system and device architecture were extensively studied in the past, they are perfectly suited for the demonstration and testing of further technological innovations. Lately, we already demonstrated that the device concept based on multi-level T-gate technology,<sup>27</sup> which

is characterized by its simplicity of lithographical processes and minimal processing steps, leads to advantageous performance. For the sake of comparison, device parameters for HFET non-recessed and gate recessed devices without an AlN layer were presented.<sup>28</sup> A comparison of the static transfer and transconductance characteristics of the devices presented—for MISHFET structure with gate recess and a deposited amorphous AlN layer (nominal thickness 4 nm) and their counterpart non-recessed and gate recessed HFET was reported in our previous study. 10 The results from CV measurements for all three types of devices, a non-recessed HFET, a gate recessed HFET, and an AlN gate recessed MISH-Fet alGaN/GaN/SiC, were also presented in our previous study.<sup>10</sup> We reported that the application of an amorphous AlN dielectric layer has a direct impact on the charge carrier concentration up to  $\sim 6.2 \times 10^{12}$  cm<sup>-2</sup>, determined by CV measurements, which is a more than 60% increase in comparison with the respective gate recessed devices without applied dielectrics. Nevertheless, all three types of investigated devices (MISHFET device structure with their non-recessed and recessed HFET counterparts) reached maximal values of static transconductance in the range ~230 to 250 mS/mm.

a) Author to whom correspondence should be addressed: dagmar.gregusova@savba.sk

In this study, we present a detailed investigation of the high frequency performance of gate recessed AlGaN/GaN MISHFETs with an amorphous AlN insulator in comparison with non-recessed and recessed HFET counterparts. All the devices are fabricated from the same material structure as it was introduced in our study.<sup>10</sup> The core of the processes involved in the device preparation is based on the so-called "step by step" selective metal etching procedure with the aim to achieve sub-micrometer-sized gate lengths controllably as was previously reported in detail.<sup>27,29</sup> This simple technological procedure allows us to improve the RF performance of any already fabricated, e.g., HFET, MOSHFET device with gate lengths in the micrometer range down to the several hundreds of nanometer or even below 100 nm range as long as the mechanical and chemical stability of the metal layer stacks as well as of the whole device is ensured. Therefore, it should be noted that the advantageous selective metal etching process is suitable especially for material layer systems, such as for the III-nitrides in our case, which are not affected by an etching solution necessary for the procedure. The etching solution (HCl acid) removes oxides on AlGaN and GaN very thoroughly, as it was reported by Okada et al.<sup>30</sup> Similarly, the chemical inertness of AlN (used as a dielectric layer in this study) was also demonstrated by Young and Duh.<sup>31</sup> Hence, this simple technique (etching procedure for formation of T-gate structures) in combination with the suitable dielectrics may overcome any possible etching induced effects in the central "source-gate recessed-drain" region.

The material structure consists of a 2 µm thick GaN buffer layer, followed by a 20 nm thick Al<sub>0.29</sub>Ga<sub>0.71</sub>N barrier grown on 6H-SiC substrates by using the MOVPE technique. 29,32 In the following, HFET devices were fabricated using conventional optical and/or e-beam lithographical processes.30 The ohmic Ti/Al/Ni/Au contact metallization for source and drain electrodes was annealed for 30 s at 850 °C in nitrogen ambient. The gate recess region with a depth of  $7 \pm 1$  nm was performed with the help of Ar ion beam etching (Ar IBE).<sup>10</sup> After that, 4 nm thick amorphous AlN layers were nominally deposited by reactive magnetron sputtering. An amorphous AlN dielectric layer with a thickness of 4 nm was studied with respect to its surface morphology after applying several etching steps with HCl:H2O solution. The amorphous AlN layer after this "step by step" etching procedure was inspected by AFM, confirming that the procedure did not induce any pinhole formation. Finally, conventional Schottky Ni/Au gate metallization was fabricated.

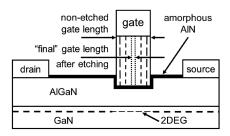

Figure 1 presents schematically a cross section of the gate recessed amorphous AlN-AlGaN/GaN MISHFET devices with the required different gate lengths achieved by using the abovementioned metal selective etching procedure. Hence, T-gate structures with different lengths are formed. The devices were investigated in a comparative approach.

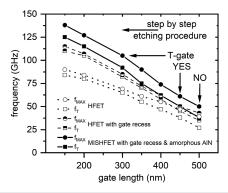

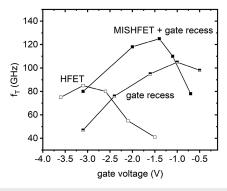

In order to characterize the RF properties of the devices prepared, the small-signal scattering parameters were measured using an Agilent 8510C automatic network analyzer. Figure 2 presents a comparison of the determined current gain cutoff frequency  $f_{\rm T}$  and maximum frequency of oscillation  $f_{\rm max}$  values as a function of the gate length for three different devices. The data are shown for non-recessed and gate recessed HFET structures and their amorphous AlN-based MISHFET counterparts without T-gate ( $L_{\rm G}=500$  nm) and with T-gate ( $L_{\rm G}$  etched down to 150 nm). As expected for all three types of devices, both  $f_{\rm T}$  and  $f_{\rm max}$  increased as the gate lengths decreased down to  $\sim 150$  nm remarkably. On the other hand, both

FIG. 1. Schematics: cross section of the gate recessed MISHFET amorphous AIN-AIGaN/GaN/SiC devices and material structure. The "nominal" gate length after the lithographical process (gate definition and metallization) represents the "starting" gate length. After applying a selective "step by step" (dashed lines) etching procedure forming T-gate structures, the "final" gate length is achieved (dotted lines). Please note that the presented schematics do not reflect the "real" geometrical lengths/dimensions of the fabricated devices presented in this study. Explicitly, these schematics are only a guide to the eye.

**FIG. 2.** Comparison of the current gain cutoff frequency  $f_T$  and maximum frequency of oscillation  $f_{max}$  values as a function of the gate length for AlGaN/GaN HFET devices with non-recessed (empty symbols) and gate recessed (half-filled) structures and their AlN-based MISHFET (full symbols) counterparts with and without T-gate structure. Please note that the values presented in this graphic are for devices with parameters close to average values.

characteristic frequencies for MISHFET devices are significantly higher than those for HFET devices. As it could be expected, the highest values for current gain and unilateral power gain cutoff frequencies were achieved after the MISHFET structure's gate length was reduced down to ~150 nm. In this case, the extracted current gain cutoff frequency  $f_{\rm T}$  and the maximum oscillation frequency  $f_{\rm max}$  reached 125 and 138 GHz, respectively.

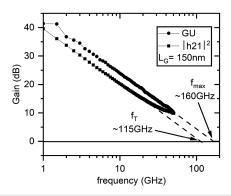

Figure 3 shows exemplarily the evaluation of the current gain  $\left|h21\right|^2$  and unilateral power gain GU parameters as a function of frequency for a single AlN-based gate recessed MISHFET with the nominal gate length (T-gate) of 150 nm. The extracted current gain cutoff frequency  $f_T$  and maximum oscillation frequency  $f_{max}$  115 and 160 GHz, respectively, differ from the values presented in Fig. 2. This is a consequence of the dispersion of the process parameters (e.g., gate recess depth and AlN thickness) over a large area, as was presented in our previous study.  $^{10}$

**FIG. 3.** Small-signal microwave performance for the gate recessed MISHFET amorphous AIN-AIGaN/GaN/SiC device with a nominal 150 nm gate length (T-gate structure). Please note that the presented data in this graphic represent an example of values acquired on a single MISHFET device.

The current gain cutoff frequency as a function of the gate voltage for HFET devices with non-recessed and gate recessed structures and their AlN-based gate recessed MISHFET counterpart is shown in Fig. 4. These data demonstrate a significant enhancement of the MISHFET cutoff frequency compared to both the HFET and gate recessed devices. The presented data for gate recessed and nonrecessed devices in Fig. 4 are fully in agreement with the studies published in the past by other groups. 33-35 As it was reported in our previous study, 10 an expected increase in the gate capacitance—as a consequence of the decrease in the gate-channel distance (for the gate recessed device) was confirmed, and simultaneously, a peak transconductance increase was observed in comparison with the non-recessed devices. Here, it should be noted that the higher gate capacitance of the active gate region lowers the influence of parasitic capacitance components leading to enhanced cutoff frequencies as it was reported for the E-HEMT by Schwierz and Liou.<sup>36</sup> On the other hand, in contrast to the explanation above, we assume, that the enhanced cutoff frequency of the MISHFET device with gate recess in comparison with its gate recessed counterpart, can by explained analogically as it was introduced for non-recessed MOSHFET

**FIG. 4.** Current gain cutoff frequency as a function of gate voltage for AlN-based gate recessed MISHFET HFET devices with non-recessed ( $V_{DS}=12$  V) and gate recessed structures ( $V_{DS}=10$  V) and their counterpart ( $V_{DS}=14$  V). All the devices have a gate length of 150 nm (T-gate structure).

vs HFETs by the higher ratio of the transconductance to the gate capacitance. This ratio mainly determines the cutoff frequency, as it was by presented by Marso *et al.*<sup>37</sup> and Kordoš *et al.*<sup>38</sup> Furthermore, it could also be explained by the transconductance increase as a consequence of the surface trap reduction due to the amorphous AlN dielectric layer and the increase in the electric field below the gate, analogically as it was demonstrated by Al<sub>2</sub>O<sub>3</sub> dielectric MOSH-FETs by Kordoš *et al.* This resulted among others in an enhancement of the channel electron mobility in the device.<sup>39</sup> Nevertheless, the deeper understanding of the physical mechanism, comprising and explaining the effects mentioned above and reported in the past, will be the scope of a theoretical study under preparation by Gregušová *et al.*

In conclusion, AlGaN/GaN-based MISHFETs using an amorphous AlN insulator and recessed gate were prepared and their high frequency performance was investigated. The properties of non-recessed and gate recessed HFET structures are shown for comparison too. Gate recess was performed with the help of Ar IBE. The step-by-step etching procedure was used to prepare T-gates with different gate lengths. The obtained results show a significant improvement in RF performance of gate recessed MISHFETs compared to non-recessed and recessed counterparts. The extracted current gain cutoff frequency  $f_{\rm T}$  and the maximum oscillation frequency  $f_{\rm max}$  for MISHFETs with a gate length of 150 nm reached 125 and 138 GHz, respectively. This demonstrates the high perspectives of gate recessed AlGaN/GaN MISHFETs with an amorphous AlN insulator for the preparation of efficient microwave devices.

This work was partially supported by the VEGA Project No. 2/0068/21 (Slovak Republic) and Grant No. APVV- 21-0365 project (Slovak Republic). In addition, all authors thank A. Fox from Langerwehe (Germany) for support with respect to the characterization of the RF performance of the devices investigated by using small-signal measurements (S-parameters) and Š. Gaži (IEE SAS) for AlN preparation.

### **AUTHOR DECLARATIONS**

#### **Conflict of Interest**

The authors have no conflits to disclose.

#### **Author Contributions**

Peter Kordoš: Data curation (equal); Formal analysis (equal); Investigation (equal); Supervision (equal); Writing – review & editing (equal). Dagmar Gregušová: Conceptualization (equal); Investigation (equal); Supervision (equal); Validation (equal). Martin Mikulics: Conceptualization (equal); Data curation (equal); Investigation (equal); Methodology (equal); Writing – review & editing (equal). Hilde Helen Hardtdegen: Conceptualization (equal); Investigation (equal); Methodology (equal); Supervision (equal); Writing – review & editing (equal).

#### **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **REFERENCES**

- <sup>1</sup>T. Oka and T. Nozawa, IEEE Electron Device Lett. **29**, 668 (2008).

- <sup>2</sup>N. Kaneko, O. Machida, M. Yanagihara, S. Iwakami, R. Baba, H. Goto, and A. Iwabuchi, in *21st International Symposium on Power Semiconductor Devices* & *IC's*, 2009 (IEEE, 2009), pp. 25–28.

- <sup>3</sup>J. Kashiwagi, T. Fujiwara, M. Akutsu, N. Ito, K. Chikamatsu, and K. Nakahara, IEEE Electron Device Lett. **34**, 1109 (2013).

- <sup>4</sup>W. Choi, O. Seok, H. Ryu, H.-Y. Cha, and K.-S. Seo, IEEE Electron Device Lett. **35**, 175 (2014).

- <sup>5</sup>T. E. Hsieh, E. Y. Chang, Y. Z. Song, Y. C. Lin, H. C. Wang, S. C. Liu, S. Salahuddin, and C. C. Hu, IEEE Electron Device Lett. 35, 732 (2014).

- <sup>6</sup>P.-C. Yeh, Y.-W. Lin, Y.-L. Huang, J.-H. Hung, B.-R. Lin, L. Yang, C.-H. Wu, T.-K. Wu, C.-H. Wu, and L.-H. Peng, Appl. Phys. Express 8, 084101 (2015).

- <sup>7</sup>Y.-C. Byun, J.-G. Lee, X. Meng, J. S. Lee, A. T. Lucero, S. J. Kim, C. D. Young, M. J. Kim, and J. Kim, Appl. Phys. Lett. 111, 082905 (2017).

- <sup>8</sup>T.-L. Wu, S.-W. Tang, and H.-J. Jiang, Micromachines 11, 163 (2020).

- H.-S. Kim, M.-J. Kang, J. J. Kim, K.-S. Seo, and H. Cha, Materials 13, 1538 (2020).

M. Mikulics, P. Kordoš, D. Gregušová, Š. Gaži, J. Novák, Z. Sofer, J. Mayer, and H. Hardtdegen, Semicond. Sci. Technol. 36, 095040 (2021).

- <sup>11</sup> U. K. Mishra, in 2010 International Electron Devices Meeting (IEEE, 2010), pp. 13.2.1–13.2.4.

- <sup>12</sup>G. Meneghesso, M. Meneghini, D. Bisi, I. Rossetto, T. L. Wu, M. Van Hove, D. Marcon, S. Stoffels, S. Decoutere, and E. Zanoni, Microelectron. Reliab. 58, 151 (2016).

- <sup>13</sup> H. Amano, Y. Baines, E. Beam, M. Borga, T. Bouchet, P. R. Chalker, M. Charles, K. J. Chen, N. Chowdhury, R. Chu, C. De Santi, M. M. De Souza, S. Decoutere, L. Di Cioccio, B. Eckardt, T. Egawa, P. Fay, J. J. Freedsman, L. Guido, O. Häberlen, G. Haynes, T. Heckel, D. Hemakumara, P. Houston, J. Hu, M. Hua, Q. Huang, A. Huang, S. Jiang, H. Kawai, D. Kinzer, M. Kuball, A. Kumar, K. B. Lee, X. Li, D. Marcon, M. März, R. McCarthy, G. Meneghesso, M. Meneghini, E. Morvan, A. Nakajima, E. M. S. Narayanan, S. Oliver, T. Palacios, D. Piedra, M. Plissonnier, R. Reddy, M. Sun, I. Thayne, A. Torres, N. Trivellin, V. Unni, M. J. Uren, M. Van Hove, D. J. Wallis, J. Wang, J. Xie, S. Yagi, S. Yang, C. Youtsey, R. Yu, E. Zanoni, S. Zeltner, and Y. Zhang, J. Phys. D: Appl. Phys. 51, 163001 (2018).

- <sup>14</sup>Y. Zhang and T. Palacios, IEEE Trans. Electron Devices **67**, 3960 (2020).

- <sup>15</sup> M. Meneghini, C. De Santi, I. Abid, M. Buffolo, M. Cioni, R. A. Khadar, L. Nela, N. Zagni, A. Chini, F. Medjdoub, G. Meneghesso, G. Verzellesi, E. Zanoni, and E. Matioli, J. Appl. Phys. 130 (2021).

- <sup>16</sup>S. Keller, S. S. Pasayat, C. Gupta, S. P. DenBaars, S. Nakamura, and U. K. Mishra, Phys. Status Solidi RRL 15, 1 (2021).

- <sup>17</sup>H.-Y. Lee, Y.-H. Ju, J.-I. Chyi, and C.-T. Lee, Materials 15, 42 (2021).

- <sup>18</sup>N. Chowdhury, Q. Xie, and T. Palacios, IEEE Electron Device Lett. 43, 358 (2022).

- <sup>19</sup>R. Zhu, H. Jiang, C. W. Tang, and K. M. Lau, IEEE Electron Device Lett. 43, 346 (2022).

- <sup>20</sup> R. Zhu, H. Jiang, C. W. Tang, and K. M. Lau, Appl. Phys. Lett. **120** (2022).

- <sup>21</sup> R. Soman, M. Malakoutian, B. Shankar, D. Field, E. Akso, N. Hatui, N. J. Hines, S. Graham, U. K. Mishra, M. Kuball, and S. Chowdhury, in *2022 International Electron Devices Meeting* (IEEE, 2022), pp. 30.8.1–30.8.4.

- <sup>22</sup>J. Kuzmik, R. Stoklas, S. Hasenöhrl, E. Dobročka, M. Kučera, P. Eliáš, F. Gucmann, D. Gregušová, Š. Haščík, A. Kaleta, M. P. Chauvat, S. Kret, and P. Ruterana, J. Appl. Phys. 135 (2024).

- <sup>23</sup> J. Würfl, T. Palacios, H. G. Xing, Y. Hao, and M. Schubert, Appl. Phys. Lett. 125 (2024).

- <sup>24</sup>J.-J. Jia, C.-C. Lin, and C.-T. Lee, IEEE Access **8**, 158941 (2020).

- <sup>25</sup> H. Wang, M. Xiao, K. Sheng, T. Palacios, and Y. Zhang, IEEE J. Emerg. Sel. Top. Power Electron. **9**, 2235 (2021).

- <sup>26</sup>H.-Y. Lee, C.-H. Lin, and C.-T. Lee, IEEE Trans. Electron Devices **69**, 500 (2022).

- <sup>27</sup> M. Mikulics, H. Hardtdegen, Y. C. Arango, R. Adam, A. Fox, D. Grützmacher, D. Gregušová, S. Stanček, J. Novák, P. Kordoš, Z. Sofer, L. Juul, and M. Marso, Appl. Phys. Lett. **105**, 232102 (2014).

- <sup>28</sup>M. Mikulics, A. Fox, M. Marso, D. Grützmacher, D. Donoval, and P. Kordoš, Vacuum 86, 754 (2012).

- <sup>29</sup>M. Mikulics, H. Hardtdegen, and D. Grützmacher, U.S. Patent 9735247B2 (18 August 2017).

- <sup>30</sup>H. Okada, M. Shinohara, Y. Kondo, H. Sekiguchi, K. Yamane, and A. Wakahara, AIP Conf. Proc. 1709, 020011 (2016).

- <sup>31</sup>C. D. Young and J. G. Duh, J. Mater. Sci. **30**, 185 (1995).

- <sup>32</sup> H. Hardtdegen, N. Kaluza, R. Steins, P. Javorka, K. Wirtz, A. Alam, T. Schmitt, and R. Beccard, Phys. Status Solidi A 202, 744 (2005).

- <sup>33</sup>H.-K. Lin, F.-H. Huang, and H.-L. Yu, Solid-State Electron. **54**, 582 (2010).

- <sup>34</sup>S. Maroldt, C. Haupt, W. Pletschen, S. Müller, R. Quay, O. Ambacher, C. Schippel, and F. Schwierz, Jpn. J. Appl. Phys. 48, 04C083 (2009).

- 35 S. Vitanov and V. Palankovski, Annu. J. Electron. 2009, 144–147 (n.d.), available at https://www.iue.tuwien.ac.at/pdf/ib\_2009/CP2009\_Vitanov\_4.pdf.

- <sup>36</sup>F. Schwierz and J. J. Liou, Solid-State Electron. **51**, 1079 (2007).

- <sup>37</sup>M. Marso, G. Heidelberger, K. M. Indlekofer, J. Bernát, A. Fox, P. Kordoš, and H. Lüth, IEEE Trans. Electron Devices **53**, 1517 (2006).

- <sup>38</sup>P. Kordoš, M. Mikulics, A. Fox, D. Gregušova, K. Cico, J.-F. Carlin, N. Grandjean, J. Novak, and K. Frohlich, IEEE Electron Device Lett. **31**, 180 (2010).

- <sup>39</sup>P. Kordoš, R. Kúdela, R. Stoklas, K. Čičo, M. Mikulics, D. Gregušová, and J. Novák, Appl. Phys. Lett. **100**, 122401 (2012).