# Evaluation of cryogenic model libraries for FDSOI CMOS transistors

Phanish Chava<sup>1</sup>, Heidrun Alius<sup>1</sup>, Jonas Buehler<sup>1</sup>, Alfonso R Cabrera-Galicia<sup>1</sup>, Carsten Degenhardt<sup>1</sup>, Thomas Gneiting<sup>1</sup>, Markus Harff<sup>1</sup>, Thomas Heide<sup>1</sup>, Peter Javorka<sup>1</sup>, Matthias Kessler<sup>1</sup>, Maximilian Lederer<sup>1</sup>, Steffen Lehmann<sup>1</sup>, Maik Simon<sup>1</sup>, Meng Su<sup>1</sup>, Patrick Vliex<sup>1</sup>, Stefan Van Waassen<sup>1</sup>, Christian Witt<sup>1</sup>, and Dennis Zetzsche<sup>1</sup>

October 28, 2025

<sup>&</sup>lt;sup>1</sup>Affiliation not available

## Evaluation of cryogenic model libraries for **FDSOI CMOS transistors**

Phanish Chava, Heidrun Alius, Jonas Buehler, Alfonso R. Cabrera-Galicia, Carsten Degenhardt, Thomas Gneiting, Markus Harff, Thomas Heide, Peter Javorka, Matthias Kessler, Maximilian Lederer, Steffen Lehmann, Maik Simon, Meng Su, Patrick Vliex, Stefan van Waassen, Christian Witt, and Dennis Zetzsche

Abstract—Scalable quantum computers demand innovative solutions to tackle the wiring bottleneck and control an increasing number of qubits. Cryogenic electronics based on CMOS technologies are promising candidates which can operate down to deep-cryogenic temperatures and act as a communication and control interface to the quantum layer. However, the performance of transistors used in these circuits is altered significantly when cooling from room temperature to cryogenic temperatures, which motivates accurate cryogenic modeling of transistors. In this paper, we report on a cryogenic simulation library tailored specifically to fully depleted silicon-on-insulator (FDSOI) transistors. We validated the accuracy of our preliminary model library by comparing simulations at both the device and circuit levels with experimental measurements from single transistors, ring oscillators, and a transimpedance amplifier. Our models effectively capture the DC behavior across the temperature range from 8 K to room tempera-

Index Terms—Cryogenics, complementary metal-oxidesemiconductor (CMOS), fully-depleted silicon-on-insulator (FDSOI), integrated circuits, ring oscillators, semiconductor device modeling, and quantum computing.

#### I. INTRODUCTION

EALIZING the full potential of quantum computers requires overcoming significant engineering challenges, particularly in the realm of qubit control and readout. One of the major hurdles is the wiring bottleneck, which arises as the number of qubits increases [1], [2].

This work was funded by the German Federal Ministry of Research. Technology and Space (BMFTR), funding program "Quantum technologies - from basic research to market", project QSolid (Grant No. 13N16149).

P. Chava, J. Buehler, A.R. Cabrera-Galicia, C. Degenhardt, M. Harff, P. Vliex, and S. van Waasen are with Integrated Computing Architectures (ICA PGI-4), Forschungszentrum Juelich GmbH, 52428 Juelich, Germany. S. van Waasen is also with the Faculty of Engineering, Communication Systems, University Duisburg-Essen, 47057 Duisburg,

- H. Alius, T. Gneiting, and M. Su are with AdMOS GmbH, 72636 Frickenhausen, Germany.

- T. Heide and D. Zetzsche are with Racyics GmbH, 01069 Dresden,

- P. Javorka, M. Kessler, and S. Lehmann are with GlobalFoundries, 01109, Dresden, Germany.

- M. Lederer and M. Simon are with Fraunhofer Institute for Photonic Microsystems IPMS, Center Nanoelectronic Technologies (CNT), 01109, Dresden, Germany.

- C. Witt is with GlobalFoundries, Kapeldreef 75, 3001 Leuven, Belgium.

Cryogenic integrated circuits, which operate at extremely low temperatures, offer a promising solution to this wiring challenge by integrating control and readout electronics close to the quantum processor and operating them at cryogenic temperatures [3]–[8]. CMOS (Complementary Metal-Oxide-Semiconductor) technology, which is the backbone of modern electronic devices, shows great potential for adaptation to cryogenic environments [9]-[12].

Among various CMOS technologies, Fully Depleted Silicon-on-Insulator (FDSOI) stands out for its excellent electrostatic control and reduced short-channel effects, making it particularly suitable for cryogenic applications [13]–[18]. The main advantage of FDSOI transistors is their ability to adjust the threshold voltage using the back gate, which becomes especially critical at cryogenic temperatures. This tunability enables compensation for the threshold voltage increase caused by cryogenic temperature. Additionally, FDSOI transistors, which are built on an ultra-thin silicon layer atop a buried oxide layer, exhibit lower variability and enhanced performance at reduced voltages. This enables lowering the power consumption, which is a crucial factor to cope with the limited cooling power of a dilution refrigerator.

The transition from room temperature to cryogenic temperatures significantly alters the electrical characteristics of a transistor. Critical device parameters such as carrier mobility, threshold voltage, and subthreshold slope are significantly affected due to reduced thermal energy and changes in carrier scattering mechanisms [19], [20]. Consequently, existing foundry-based simulation libraries, which are typically characterized only down to  $-40\,^{\circ}$ C, fail to accurately predict device performance at deep cryogenic temperatures. This discrepancy motivates the need for specialized cryogenic libraries that can accurately capture the physical phenomena occurring in the cryogenic regime.

Among the widely used modeling approaches, the Enz-Krummenacher-Vittoz (EKV) model [21], [22] requires the fewest parameters. It is a charge-based compact framework that is particularly suited for low-power and analog applications, offering strong performance in weak inversion regions. On the other hand, the BSIM family of models from UC Berkeley feature extensive parameterization to handle the complexities of advanced transistor technologies. These models accurately capture short-channel effects and performance in various operating conditions and require significant adaptation and retuning to account for cryogenic effects, such as

Fig. 1. (a) Cryogenic chamber and (b) a close-up of test chip with DC needle probes.

carrier freeze-out, mobility degradation, and threshold voltage shifts. Lastly, the L-UTSOI model developed by CEA-LETI [23], [24] is specifically designed for FDSOI technology and provides an optimal balance between computational efficiency and physical accuracy. It captures the unique characteristics of ultra-thin body and body-biasing effects, which are critical at low temperatures. The BSIM family and L-UTSOI are both recognized as the industry standard compact SPICE models by the Compact Model Coalition.

In this work, using the BSIM-IMG library, we develop a cryogenic simulation library for transistors based on a FDSOI process of GlobalFoundries. We rely on the BSIM-IMG library due to its compatibility with the foundry library as well as industry-standard EDA and simulation software, like Cadence Spectre. As a starting point, we performed DC characterization of several transistors from room temperature down to  $8\,\mathrm{K}$ , which is used as a calibration reference for the generation of the simulation library over the entire temperature range.

The developed library is used to simulate single-transistor devices and circuit blocks like ring oscillators and a transimpedance amplifier. The results of these simulations are compared against the measurement data at different temperatures to verify the accuracy of our transistor models. This work aims to provide a robust modeling framework that supports the design and accurate simulation of cryogenic electronic circuits. Such a framework is essential for the development of scalable quantum computing systems, where reliable and scalable control and readout electronics play a critical role.

#### II. DEVICE CHARACTERIZATION

### A. Experimental Setup

We used an attoDRY800 closed-cycle cryostat to cool down the test chips. The cryostat can achieve a minimum temperature of 5 K. However, the base temperature can vary depending on the measurement configuration. Figure 1(a) and (b) show the system configuration for the measurement of single transistor devices using DC multi-contact needle probes. The probes are mounted onto piezo-positioners to access different areas of the test chip. In this particular configuration, a base temperature of 8 K is achieved. The test chips described in section V were wire bonded to a custom printed circuit board (PCB), and the measurements were also performed in the same cryogenic chamber.

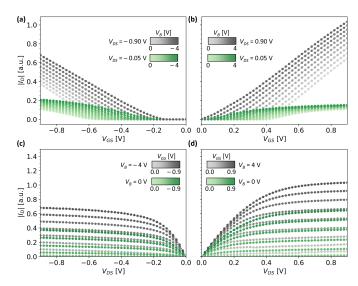

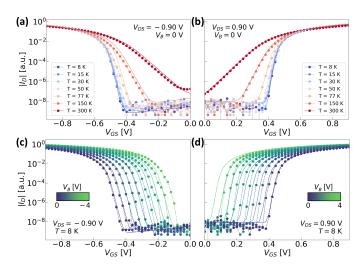

Fig. 2. Normalized transfer curves of (a) PMOS and (b) NMOS transistors at  $|V_{DS}|=0.05\,\mathrm{V}$  (green curves) and  $|V_{DS}|=0.90\,\mathrm{V}$  (gray curves), varying across different back-bias values  $(V_B)$  in steps of  $|0.5\,\mathrm{V}|$ ; normalized output curves of (c) PMOS and (d) NMOS transistors at  $V_B=0\,\mathrm{V}$  (green curves) and  $|V_B|=4\,\mathrm{V}$  (gray curves), varying across different front-gate biases  $(V_{GS})$  in steps of  $|0.1\,\mathrm{V}|$  Measurements are recorded at  $8\,\mathrm{K}$  for all the sub-plots.

#### B. I-V Measurements

The test chip, which is comprised of transistor arrays, was produced by GlobalFoundries. Initially, our investigations concentrated on the SLVT (Super-low threshold voltage) variant of the transistors. We carried out comprehensive DC characterization on transistors of various sizes, spanning from room temperature down to  $8\,\mathrm{K}$ .

We measured the current-voltage (IV) characteristics of each device under a range of bias conditions at different temperature stages, using the Keysight B1500 Parameter Analyzer. For illustration, Figure 2 presents examples of these measurements at  $8\,\mathrm{K}$  for both NMOS and PMOS transistors of identical dimensions.

The impact of the applied back-bias  $(V_B)$  on these transistors is clearly visible in the transfer curves shown in Figure 2(a) and (b). These curves reveal a shift in the threshold voltage towards lower values, which is observed for both linear  $(|V_{DS}| = 0.05 \, \mathrm{V})$  and saturation modes  $(|V_{DS}| = 0.90 \, \mathrm{V})$  of the transistors shown by the green and gray sets of curves. These measurements were repeated for multiple devices of different device dimensions across temperatures ranging from 8 K to  $300 \, \mathrm{K}$ .

#### III. MODELING APPROACH

We developed a simulation library based on DC measurements to cover the temperature range from room temperature down to a few Kelvin. For the modeling process, we utilized the BSIM-IMG 102-9.6 model [25], which includes a built-in cryogenic extension. This model was selected for its ability to accurately capture the physical phenomena in FDSOI transistors at low temperatures. We calibrated the model parameters using the measured data to ensure that the

simulated behavior aligned with the observed characteristics across the temperature range.

#### A. SPICE models for cryogenic applications

Simulation models for bulk or SOI devices have traditionally supported temperatures down to  $-55\,^{\circ}\mathrm{C}$  (218 K). For applications such as cooled amplifiers or infrared detectors, specialized models were developed to accommodate even lower temperatures,  $4\,\mathrm{K}$  for helium-cooled and  $77\,\mathrm{K}$  for nitrogen-cooled circuits. Since these circuits are only operated at a fixed temperature, it is sufficient to create the models without temperature effects and also to set the extraction and simulation temperature to  $25\,^{\circ}\mathrm{C}$  although the measurements were carried out at a low temperature. This approach avoids numerical problems in the models if the correct temperature would be set.

Two standard models certified by the Compact Model Coalition have already been available for transistors manufactured in the 22nm FDSOI process: BSIM-IMG 102.9.4 [25] from UC Berkeley and L-UTSOI 102.5 [23], [24] from CEA-LETI. However, both models failed to converge at temperatures below approximately 40 K. More recently, the updated versions BSIM-IMG 102.9.6 and L-UTSOI 102.7 [26] have been released with cryogenic extensions that enable reliable simulation across the targeted temperature range.

The cryogenic extension in the case of the BSIM-IMG model avoids numerically unstable states when the transistor temperature approaches absolute zero. This can be seen particularly well in the calculation of the temperature voltage (Vtm), which approaches 0 as the temperature falls. This can lead to floating-point exceptions in those parts of the model code that use the fundamental expression:

$$\lim_{T \to 0} \left( \frac{k_B T}{q} \right) = 0 \tag{1}$$

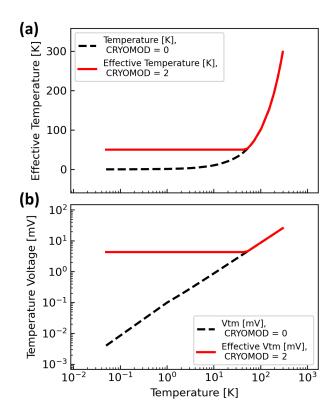

To avoid this situation, BSIM-IMG 102.9.6 introduces an effective temperature (Tempeff) for the cryogenic extension, which specifies a lower limit for the device temperature, and this avoids the aforementioned numerical problems.

The two subplots shown in Figure 3 have been generated using the Verilog-A code of the BSIM-IMG 102.9.6 model. They show the effective temperature for BSIM-IMG 102.9.6 with CRYOMOD model selector set to 0 (standard operation with classical temperature model) and CRYOMOD = 2 with the special extension for cryogenic applications. Below is the derived temperature voltage Vtm for both cases. Both variables go into a saturated state at a temperature of approximately  $50 \, \mathrm{K}$ .

In this paper, the parameter extractions have been performed for the BSIM-IMG model, which serves as the foundation for the existing foundry library.

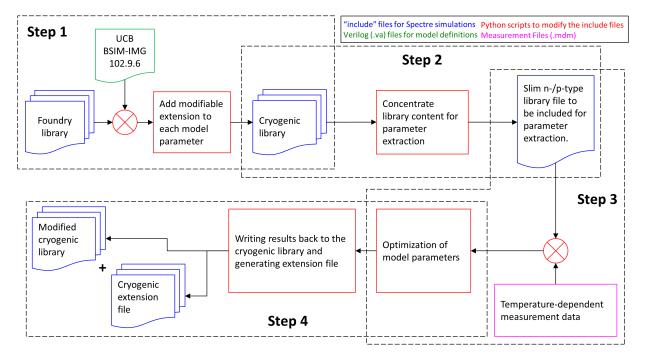

#### B. Model parameter extraction and simulation library

Figure 4 shows an overview of the general development flow of the simulation library, organized into four main steps. The first step involves expanding the existing foundry library (based on BSIM-IMG 102.9.4) to include the additional

Fig. 3. Calculation of (a) effective temperature and (b) resulting temperature voltage for CRYOMOD=0 and 2

cryogenic extension parameters from the BSIM-IMG 102.9.6 model. Following this, a modifiable adjustment parameter is introduced for each of the model parameters, as shown in the following example:

$$UA1 = 0.00 + UA1_{adjust}$$

(2a)

$$UC = -0.027 + UC_{adjust}$$

(2b)

$$TLOW = 50.0 + TLOW_{adjust}$$

(3a)

$$KT11 = 0.01 + KT11_{adjust}$$

(3b)

where Equations 2 correspond to the parameters in the existing foundry library, while Equations 3 account for the cryogenic extension parameters. In this fashion, all the remaining model parameters are also redefined with the adjustment parameters, resulting in an updated version of the existing foundry library, hereby defined as our *cryogenic library*.

In the second step, simulations are performed for various device geometries using the existing foundry library. An initial parameter extraction is carried out to capture the effective model parameters across all measured temperature points. These parameters are compiled into a new file, referred to as the *slim library* file, including a compact model to adapt the simulation to the measured curves. This file contains both geometry-independent parameters as well as the parameters that vary with the width (W) and/or gate length (L), along with the adjustment parameters to be tuned in the next step.

The *slim library* file is then loaded into the simulator along with the measured data corresponding to each temperature point. At this stage, the adjustment parameters are iteratively

Fig. 4. Flowchart depicting the development of cryogenic simulation libraries. The blocks are color-coded according to the type of files indicated in the legend.

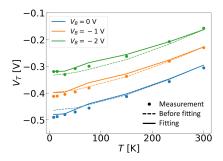

Fig. 5. Calibration of  ${\it V}_{\it T}$  values using measurement data of a short-channel PMOS transistor.

optimized to minimize the relative error between simulated and measured data across all temperatures. In the first step of the optimization procedure, the existing temperature parameters like UTE for the basic mobility behavior are re-adjusted to the extended temperature range down to a few Kelvin. Subsequently, only a few specific model parameters for the cryogenic extension, like the threshold voltage parameters KT11, the mobility coefficient UA2, or the velocity saturation parameter AT2, and in the case of the p-type transistor, the transition parameter TLOW and the coefficient for smoothening function TMEXP2 were taken to adjust the simulations to the experimental data. Table I lists the parameters that were chosen for the optimization. As an example, we show the adjustment of the threshold voltage  $(V_T)$  versus temperature at different back bias values in Figure 5, which includes both the measurement points as well as the fitting curves. The curves before fitting (simulated with the existing foundry library), the parameters to the measurement data are shown as dashed lines, and the curves after optimization (simulated with cryogenic library) are shown as solid lines.

Fig. 6. Measured (symbols) and simulated (lines) transfer curves at different temperatures for short-channel (a) PMOS and (b) NMOS transistor; measured and simulated transfer curves at  $8\,\mathrm{K}$  for different backbias voltages in steps of  $|0.5\,\mathrm{V}|$  (c) PMOS and (d) NMOS transistor. The curves in all the sub-figures are normalized to the corresponding maximum values.

As a final step, after the whole extraction process, the results are written back to the cryogenic library and a separate cryogenic extension file. These files with optimized parameters can be directly loaded into an EDA software for simulations across a broad temperature range of a few K to 298 K. The cryogenic library was also verified against the original library, and it shows identical behavior at room temperature.

TABLE I

MODEL PARAMETERS GROUPED BY TEMPERATURE DEPENDENCE

| A. Non-cryogenic temperature parameters |                                               |    |   |   |     |  |  |

|-----------------------------------------|-----------------------------------------------|----|---|---|-----|--|--|

| Name                                    | Description                                   | P0 | w | L | W×L |  |  |

| KT1L                                    | Vth temperature coefficient                   | х  |   |   |     |  |  |

| KT2                                     | Vth temperature coefficient                   | x  |   |   |     |  |  |

| UTE                                     | Mobility temperature coefficient              | x  | x | x | x   |  |  |

| UTL                                     | Mobility temperature coefficient              | x  |   |   |     |  |  |

| UA1                                     | Mobility temperature coefficient for UA       | x  | x |   |     |  |  |

| UC1                                     | Mobility temperature coefficient for UC       | x  |   |   |     |  |  |

| PRT                                     | Series resistance temperature coefficient     | x  |   |   |     |  |  |

| AT                                      | Saturation velocity temperature coefficient 1 | x  |   |   | x   |  |  |

| ATL                                     | Length scaling parameter for AT               | x  |   |   |     |  |  |

| PTWGT                                   | PTWG temperature coefficient                  | x  |   | x |     |  |  |

| B. Model | narameters | for | cryogenic | extension | (CRYOMOD = 2) |

|----------|------------|-----|-----------|-----------|---------------|

| B. Model | parameters | IOL | crvogenic | extension | (CKYOMOD = Z) |

| Name    | Description                                                                                                            | P0 | W | L | $W{	imes}L$ |

|---------|------------------------------------------------------------------------------------------------------------------------|----|---|---|-------------|

| CRYOMOD | Cryogenic model selector; 2 = turn<br>on cryogenic model and merge<br>smoothly to CRYOMOD = 0 for T<br>more than 210 K |    |   |   |             |

| KT11    | Vth temperature coefficient                                                                                            | x  |   |   |             |

| UA2     | Mobility temperature coefficient for UA                                                                                | x  |   |   |             |

| TLOW    | Transition temperature of SS at low temperatures                                                                       | x  |   |   |             |

| TMEXP2  | Temperature coefficient for Vdseff smoothing                                                                           | x  |   |   |             |

| AT2     | Saturation velocity temperature coefficient                                                                            | x  |   |   |             |

#### A. I-V Curves

Using the *cryogenic library*, we simulated the transfer curves of short-channel PMOS and NMOS transistors with identical dimensions at the measured temperature points. The temperature dependence of the measured (symbols) and simulated (lines) transfer curves is shown in Figure 6(a) and (b) for the PMOS and NMOS transistors, respectively, at  $V_B=0\,\mathrm{V}$  and  $|V_{DS}|=0.90\,\mathrm{V}$ .

The results indicate that the *cryogenic library* has a good match to the measurements at room temperature for both PMOS and NMOS transistors. However, at cryogenic temperatures, the model has a larger deviation from the measurement points as compared to room temperature. This is also observed in the back-bias dependent transfer curves at 8 K as shown in Figure 6(c) and (d), where the model deviates further from the measurement at much higher  $|V_B|$  values, especially in the weak inversion or the sub-threshold regime.

#### B. Threshold Voltage

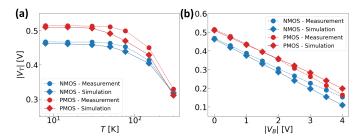

From the measured transfer curves, we use the threshold voltage as an initial parameter to quantitatively estimate the accuracy of our model. For all the measured and simulated curves shown in Figure 6, the threshold voltage values were extracted using the constant current method [27]. Critical current values of  $100 \, \text{nA}$  and  $300 \, \text{nA}$  were used for the PMOS

Fig. 7. Measured and simulated values of threshold voltage plotted against (a) temperature at  $V_B = 0 \, \text{V}$  and (b) back-bias at  $T = 8 \, \text{K}$ .

and NMOS transistors, respectively. Figure 7(a) shows the extracted threshold voltage values of the curves in Figure 6(a) and (b) plotted together against temperature.

For both PMOS and NMOS transistors, the values increase with decreasing temperature and start to saturate towards lower temperatures around 30 K, which is also in agreement with previous reports on bulk [20], [28] and FDSOI [29] transistors. Using the extracted  $V_T$  values from the measurement and simulations, we calculated the mean average percentage error (MAPE) between measured and simulated  $V_T$  values for the PMOS and NMOS transistors to be around 3% and 2%, respectively, over the entire temperature range. However, on considering the  $V_T$  values for different back-bias conditions at 8 K as plotted in Figure 7(b), the MAPE in  $V_T$  for PMOS and NMOS devices was extracted to be around 15% and 5% respectively, indicating that the model deviation is much higher for PMOS devices at 8 K. Nevertheless, for  $|V_B| < 1.5 \,\mathrm{V}$  the model fits well with the measured data for both PMOS and NMOS transistors.

#### V. CIRCUIT-LEVEL VALIDATION

We further expanded our investigation on the accuracy of our cryogenic models using two distinct test chips. The first test chip, featuring a series of ring oscillators, was designed by Racyics GmbH, while the second, developed at ICA (PGI-4), includes a transimpedance amplifier. Both test chips were produced by GlobalFoundries and the specific circuit blocks we focused on within these chips were designed using the SLVT variants of the transistors as discussed previously.

#### A. ABB Ring Oscillators

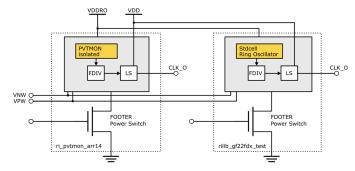

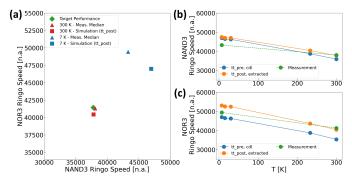

In cryogenic temperatures, a major target is to significantly reduce the power consumption of digital standard cell logic. But, high performance is still required. Biasing the backgate of the transistors is a promising technique to speed up digital circuits powered with ultra-low supply voltage (ULV). An investigation of digital standard cell logic performance in cryogenic conditions with an Advanced Body-Biasing (ABB) regulation scheme [30] can be evaluated with the test chip. The resulting measurements are compared to the simulation with the developed cryogenic transistor library.

The test chip contains PVT performance monitors of the SLVT transistor flavor with a gate-length of  $28\,\mathrm{nm}$ . A single PVT monitor instance consists of ring oscillators with NAND3 and NOR3 standard cell logic gates. Multiple instances of

Fig. 8. ABB PVT monitor and standard cell ring oscillator test structure.

Fig. 9. PVT monitor (a) measurement and (b) simulation values at ZBB  $0.80\,\mathrm{V}$  at  $300\,\mathrm{K}$ .

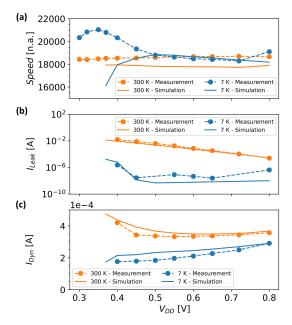

them are instantiated to measure the local performance deviation on silicon. Based on the room temperature target performance of the PVT monitor ring oscillators at Zero-Body-Bias (ZBB) and 0.80 V supply voltage, in room and cryogenic temperatures, and lower supply voltages, the PVT monitors are moved to their target performance. Hence, in each PVT operation condition the back-bias voltages  $V_{NW}$  and  $V_{PW}$  are adapted in forward body-bias direction (FBB) from ZBB to  $V_{NW} = -V_{PW} = 4.0 \,\mathrm{V}$  based on the ABB scheme [30]. The adapted back-bias voltages are applied to a test ring oscillator consisting of standard cell logic gates of a specific cell type (e.g. INV), VT-flavor, and gate-length (e.g. SLVT 28 nm). Measurement results of the ring oscillator speed, leakage, and dynamic current consumption are compared to simulation values. The schematic of the ABB ring oscillator measurement is visualized in Figure 8.

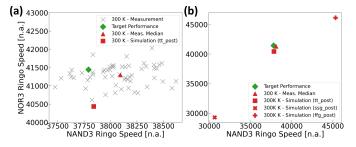

The ABB target performances of PVT monitor ring oscillators NAND3 and NOR3 are depicted in Figure 9. At room temperature, the median of the NMOS-sensitive ring oscillator built up of NAND3 standard cell logic gates is 1% slower than the TT (typical-typical) process model. The median of the PMOS-sensitive NOR3 ring oscillator measurement is around 2.5% faster than the TT process model. At cryogenic temperature, the PVT monitor NAND3 ring oscillator is faster by 15% and the NOR3 ring oscillator has a speed-up by 20% compared to the room temperature measurements. In Figure 10, the developed cryogenic model also shows a speed-up of the ring oscillator performance from room temperature to cryogenic temperature. This speed-up has been simulated for schematic and extracted netlists, and is about 8% greater than the measurements show.

The standard cell ring oscillator performance, leakage, and dynamic current consumption in the ABB corners are depicted

Fig. 10. (a) PVT monitor measurement and simulation values at ZBB  $0.80\,\mathrm{V}$  at  $7\,\mathrm{K}$ ; Comparison of schematic and extracted netlist simulation of (b) NAND3 and (c) NOR3 ring oscillators with the cryogenic transistor models.

in Figure 11(a)-(c), respectively. The ABB calibration has been executed on silicon and virtually, with the transistor models extended to the cryogenic temperature range. Due to ABB, the process mismatch between the model and silicon seen in the ZBB PVT monitor measurement is canceled out. Therefore, the performance measurements in Figure 11(a) show only a deviation of less than 0.5% down to a supply voltage of 0.40 V between model and silicon. For lower supply voltages  $(V_{DD} < 0.50 \,\mathrm{V})$ , the back-bias voltages are close to their limits of  $V_{NW} = -V_{PW} = 4.0 \,\mathrm{V}$ . Since the ABB simulations with the cryogenic model show a higher back-bias sensitivity than on silicon measured, for  $V_{DD} < 0.50 \,\mathrm{V}$  the back-bias voltages are at their limits and slow down the ring oscillator in the simulation. On silicon, an over-compensation of the ring oscillator performance can be observed since the backbias voltages are in between their limits, especially for lower supply voltages of  $V_{DD}$ . In Figure 11(b), the leakage current rises exponentially with lower  $V_{DD}$  because the ring oscillator is more biased into the forward direction. The cryogenic model shows a very low leakage independent of the backgate voltage and supply voltage for  $V_{DD} > 0.45 \,\mathrm{V}$ . Then, the leakage rises rapidly due to the back-bias voltages close to their voltage range limits. The dynamic current consumption of the test ring oscillator in Figure 11(c) shows a minimum around 0.55 V at room temperature. In cryogenic temperatures, the dynamic current consumption decreases with lower  $V_{DD}$ for the developed model as well as the measurements.

At ZBB 0.80 V, the developed cryogenic model shows a speed-up of NAND3 and NOR3 ring oscillator performances from room temperature to cryogenic temperature, which is also observed in the measurements. With the removed process offset between silicon and model by ABB in between the back-bias voltage range limits, the cryogenic model can fairly represent the ABB ring oscillator measurements.

#### B. Transimpedance Amplifier

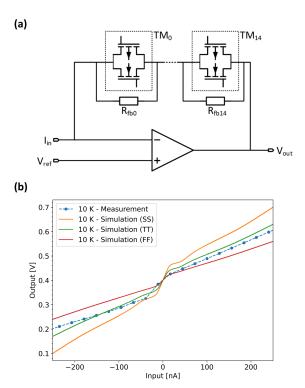

We tested the performance of the developed models further by simulating a transimpedance amplifier (TIA). The TIA comprises of a two-stage operational amplifier with adjustable gain as shown in Figure 12(a). In order to implement gain control, the feedback loop comprises of 15 resistors ( $200 \, \mathrm{k}\Omega$ ), which can be shorted with a standard transmission gate.

Fig. 11. Exemplary standard cell ring oscillator measurement of SLVT28 INVX040 and comparison to simulation results for ring oscillator (a) speed, (b) leakage current, and (c) dynamic current consumption.

Fig. 12. (a) Schematic and (b) output characteristic of the transimpedance amplifier.

Simulation at the minimum valid temperature using the standard library at  $-40\,^{\circ}\mathrm{C}$  demonstrates an expected highly linear output characteristic. Initial measurements at  $10\,\mathrm{K}$  reveal a kink in the output characteristic of the TIA for currents approaching  $0\,\mathrm{A}$  as seen in Figure 12(b).

We simulated the amplifier using our cryogenic library, which yielded results that align closely with the observed measurement at  $10\,\mathrm{K}$ . The simulation setup comprises the

foundry's standard library, with the substitution of the standard p- and n-channel transistors with our cryogenic models. Cadence Spectre AMS Designer was employed as a simulator, with the ambient temperature set to  $-40\,^{\circ}\mathrm{C}$ , to circumvent potential invalid behavior of feedback resistors, since cryogenic models are unavailable for them. The temperature of the transistors is set to  $-266\,^{\circ}\mathrm{C}$  within a configuration cell-view. The simulation is performed with two worst-case corners, i.e slow-slow (SS) and fast-fast (FF).

The measured output characteristic is found to be within the simulated worst-case corners, which demonstrates the correctness of the cryogenic simulation. Moreover, the kink inside the output characteristic can be investigated by setting the temperature of individual sets of transistors to room temperature. In this case, the kink is caused by an increase in the threshold of the transistors inside the transmission gates. For values around  $V_{DD}/2$ , neither the n-channel nor the p-channel transistor is fully conducting, increasing the resistance of the feedback network around this value. A more detailed analysis of the amplifier with further measurements and simulations is yet to be done and is not available at the moment, and is beyond the scope of this work.

#### VI. CONCLUSION

In summary, we have addressed the critical need for accurate transistor modeling in cryogenic environments, which is essential for the advancement of scalable quantum computing systems. We developed a cryogenic simulation library specifically for a FDSOI technology, compatible with industry-standard EDA tools such as Cadence Spectre. This library was calibrated using DC characterization data collected from room temperature down to  $8\,\mathrm{K}$ , ensuring its reliability across a broad temperature range.

Our simulations of single transistor devices and circuit blocks, including ring oscillators and a transimpedance amplifier, demonstrated a reasonable agreement with experimental measurements from room temperature down to 8 K. While the model is not production-ready, it successfully captures key trends and provides a reliable basis for the design and simulation of cryogenic integrated circuits. These results show a significant step towards the development of cryogenic electronics for scalable quantum computers.

#### **ACKNOWLEDGMENT**

The authors acknowledge financial support from the German Federal Ministry of Research, Technology and Space (BMFTR), under the program "Quantum technologies from basic research to market", project QSolid (Grant No. 13N16149).

#### REFERENCES

- [1] D. Reilly, "Challenges in scaling-up the control interface of a quantum computer," in 2019 IEEE International Electron Devices Meeting (IEDM), pp. 31–7, IEEE, 2019.

- [2] D. J. Reilly, "Engineering the quantum-classical interface of solid-state qubits," *npj Quantum Information*, vol. 1, no. 1, pp. 1–10, 2015.

- [3] B. Patra, R. M. Incandela, J. P. Van Dijk, H. A. Homulle, L. Song, M. Shahmohammadi, R. B. Staszewski, A. Vladimirescu, M. Babaie, F. Sebastiano, and E. Charbon, "Cryo-CMOS Circuits and Systems for Quantum Computing Applications," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 1, pp. 309–321, 2018.

- [4] J. Anders, M. Babaie, J. C. Bardin, I. Bashir, G. Billiot, E. Blokhina, S. Bonen, E. Charbon, J. Chiaverini, I. L. Chuang, C. Degenhardt, D. Englund, L. Geck, L. Le Guevel, D. Ham, R. Han, M. I. Ibrahim, D. Kruger, K. M. Lei, A. Morel, D. Nielinger, G. Pillonnet, J. M. Sage, F. Sebastiano, R. B. Staszewski, J. Stuart, A. Vladimirescu, P. Vliex, and S. P. Voinigescu, "CMOS Integrated Circuits for the Quantum Information Sciences," *IEEE Transactions on Quantum Engineering*, vol. 4, no. June, 2023.

- [5] H. Homulle, S. Visser, B. Patra, G. Ferrari, E. Prati, F. Sebastiano, and E. Charbon, "A reconfigurable cryogenic platform for the classical control of quantum processors," *Review of Scientific Instruments*, vol. 88, no. 4, pp. 343–346, 2017.

- [6] A. R. Cabrera-Galicia, A. Ashok, P. Vliex, L. Schreckenberg, P. Chava, S. Bhat, A. Kruth, A. Zambanini, and S. van Waasen, "Power Integrity Challenges in Large Scale Quantum Computers and Solutions," in *IEEE Workshop on Quantum Computing: Devices, Cryogenic Electronics and Packaging*, Zentralinstitut für Elektronik, 2023.

- [7] F. Sebastiano, H. Homulle, B. Patra, R. Incandela, J. Van Dijk, L. Song, M. Babaie, A. Vladimirescu, and E. Charbon, "Cryo-CMOS Electronic Control for Scalable Quantum Computing: Invited," *Proceedings - Design Automation Conference*, vol. Part 12828, 2017.

- [8] F. Jazaeri, A. Beckers, A. Tajalli, and J. M. Sallese, "A Review on quantum computing: From qubits to front-end electronics and cryogenic MOSFET physics," *Proceedings of the 26th International Conference* "Mixed Design of Integrated Circuits and Systems", MIXDES 2019, pp. 15–25, 2019.

- [9] P. Vliex, C. Degenhardt, C. Grewing, A. Kruth, D. Nielinger, S. Van Waasen, and S. Heinen, "Bias voltage DAC operating at cryogenic temperatures for solid-state qubit applications," *IEEE solid-state* circuits letters, vol. 3, pp. 218–221, 2020.

- [10] A. R. Cabrera-Galicia, A. Ashok, P. Vliex, C. Degenhardt, A. Kruth, A. Artanov, and S. van Waasen, "Towards the development of cryogenic integrated power management units," in 2022 IEEE 15th Workshop on Low Temperature Electronics (WOLTE), pp. 1–4, IEEE, 2022.

- [11] C. Degenhardt, A. Artanov, L. Geck, C. Grewing, A. Kruth, D. Nielinger, P. Vliex, A. Zambanini, and S. Van Waasen, "Systems engineering of cryogenic CMOS electronics for scalable quantum computers," *Pro*ceedings - IEEE International Symposium on Circuits and Systems, vol. 2019-May, pp. 1–5, 2019.

- [12] E. Charbon, "Cryo-CMOS Electronics for Quantum Computing: Bringing Classical Electronics Closer to Qubits in Space and Temperature," IEEE Solid-State Circuits Magazine, vol. 13, no. 2, pp. 54–68, 2021.

- [13] R. Carter, J. Mazurier, L. Pirro, J. U. Sachse, P. Baars, J. Faul, C. Grass, G. Grasshoff, P. Javorka, T. Kammler, A. Preusse, S. Nielsen, T. Heller, J. Schmidt, H. Niebojewski, P. Y. Chou, E. Smith, E. Erben, C. Metze, C. Bao, Y. Andee, I. Aydin, S. Morvan, J. Bernard, E. Bourjot, T. Feudel, D. Harame, R. Nelluri, H. J. Thees, L. M-Meskamp, J. Kluth, R. Mulfinger, M. Rashed, R. Taylor, C. Weintraub, J. Hoentschel, M. Vinet, J. Schaeffer, and B. Rice, "22nm FDSOI technology for emerging mobile, Internet-of-Things, and RF applications," Technical Digest International Electron Devices Meeting, IEDM, pp. 2.2.1–2.2.4, 2017.

- [14] W. Chakraborty, K. A. Aabrar, J. Gomez, R. Saligram, A. Raychowd-hury, P. Fay, and S. Datta, "Characterization and Modeling of 22 nm FDSOI Cryogenic RF CMOS," *IEEE Journal on Exploratory Solid-State Computational Devices and Circuits*, vol. 7, no. 2, pp. 184–192, 2021.

- [15] H. C. Han, F. Jazaeri, A. D'Amico, Z. Zhao, S. Lehmann, C. Kretzschmar, E. Charbon, and C. Enz, "In-depth Cryogenic Characterization of 22 nm FDSOI Technology for Quantum Computation," 2021 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon, EuroSOI-ULIS 2021, no. 871764, pp. 1–4, 2021.

- [16] S. Bonen, M. Sadegh Dadash, A. Zandieh, U. Alakuşu, M. Jia Gong, J. Rafique, L. Wu, E. Checca, H. Yun Hsu, S. Pati Tripathi, G. Cooke, and S. P. Voinigescu, "Harnessing the unique features of FDSOI CMOS technology in fibreoptic, millimetre-wave, and quantum computing circuits from 2 K to 400 K," Solid-State Electronics, vol. 194, no. April, 2022.

- [17] S. P. Tripathi, S. Bonen, A. Bharadwaj, T. Jager, C. Nastase, S. Iordănescu, G. Boldeiu, M. Păşteanu, A. Nicoloiu, I. Zdru, et al., "Characterization and modeling of quantum dot behavior in FDSOI

- devices," *IEEE Journal of the Electron Devices Society*, vol. 10, pp. 600–610, 2022.

- [18] J. P. G. Van Dijk, B. Patra, S. Subramanian, X. Xue, N. Samkharadze, A. Corna, C. Jeon, F. Sheikh, E. Juarez-Hernandez, B. P. Esparza, et al., "A scalable cryo-CMOS controller for the wideband frequencymultiplexed control of spin qubits and transmons," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 11, pp. 2930–2946, 2020.

- [19] A. Beckers, F. Jazaeri, H. Bohuslavskyi, L. Hutin, S. D. Franceschi, and C. Enz, "Characterization and modeling of 28-nm FDSOI CMOS technology down to cryogenic temperatures," *Solid State Electronics*, vol. 159, no. 688539, pp. 106–115, 2020.

- [20] A. Beckers, F. Jazaeri, A. Grill, S. Narasimhamoorthy, B. Parvais, and C. Enz, "Physical model of low-temperature to cryogenic threshold voltage in MOSFETs," *IEEE Journal of the Electron Devices Society*, vol. 8, pp. 780–788, 2020.

- [21] C. C. Enz, F. Krummenacher, and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications," *Analog integrated circuits and signal processing*, vol. 8, pp. 83–114, 1995.

- [22] H.-C. Han, A. D'Amico, and C. Enz, "Comprehensive Design-oriented FDSOI EKV Model," in 2022 29th International Conference on Mixed Design of Integrated Circuits and System (MIXDES), pp. 40–44, IEEE, 2022.

- [23] T. Poiroux, S. Martinie, O. Rozeau, M. Reiha, and J. Arcamone, "L-UTSOI: Best in-class compact modeling solution for FD-SOI technologies," in 2021 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), pp. 1–3, IEEE, 2021.

- [24] S. Martinie, O. Rozeau, T. Poiroux, P. Scheer, S. El Ghouli, M. Kang, A. Juge, and H. Lee, "L-UTSOI: A compact model for low-power analog and digital applications in FDSOI technology," in 2020 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 311–314, IEEE, 2020.

- [25] C. Hu, S. Khandelwal, Y. S. Chauhan, T. Mckay, J. Watts, J. P. Duarte, P. Kushwaha, and H. Agarwal, *Industry standard FDSOI compact model BSIM-IMG for IC design*. Woodhead Publishing, 2019.

- [26] M. Alepidis, S. Jarjayes, T. Bédécarrats, S. Martinie, M. Cassé, C. Witt, and O. Rozeau, "Cryogenic L-UTSOI model for 22nm pMOS FD-SOI, including stress effects," in 2024 IEEE European Solid-State Electronics Research Conference (ESSERC), pp. 737–740, IEEE, 2024.

- [27] A. Ortiz-Conde, F. J. García-Sánchez, J. Muci, A. T. Barrios, J. J. Liou, and C.-S. Ho, "Revisiting MOSFET threshold voltage extraction methods," *Microelectronics Reliability*, vol. 53, no. 1, pp. 90–104, 2013.

- [28] N. C. Dao, A. El Kass, M. R. Azghadi, C. T. Jin, J. Scott, and P. H. Leong, "An enhanced MOSFET threshold voltage model for the 6–300 K temperature range," *Microelectronics Reliability*, vol. 69, pp. 36–39, 2017

- [29] G. Pahwa, P. Kushwaha, A. Dasgupta, S. Salahuddin, and C. Hu, "Compact modeling of temperature effects in FDSOI and FinFET devices down to cryogenic temperatures," *IEEE Transactions on Electron Devices*, vol. 68, no. 9, pp. 4223–4230, 2021.

- [30] S. Höppner, H. Eisenreich, D. Walter, A. Scharfe, A. Oefelein, F. Schraut, J. Schreiter, T. Riedel, H. Bauer, R. Niebsch, et al., "Adaptive body bias aware implementation for ultra-low-voltage designs in 22FDX technology," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 67, no. 10, pp. 2159–2163, 2019.