## Rate limiting step for the switching kinetics in Cu doped Ge0.3Se0.7 based memory devices with symmetrical and asymmetrical electrodes

R. Soni, P. Meuffels, A. Petraru, O. Vavra, and H. Kohlstedt

Citation: Journal of Applied Physics 113, 124504 (2013); doi: 10.1063/1.4797488

View online: http://dx.doi.org/10.1063/1.4797488

View Table of Contents: http://scitation.aip.org/content/aip/journal/jap/113/12?ver=pdfcov

Published by the AIP Publishing

### Articles you may be interested in

Chemical-state-resolved depth profiles of Al/Pr0.7Ca0.3MnO3 stacked structures for application in resistive switching devices

J. Appl. Phys. 114, 243711 (2013); 10.1063/1.4858381

Charge trapping-detrapping induced resistive switching in Ba0.7Sr0.3TiO3

AIP Advances 2, 032166 (2012); 10.1063/1.4754150

On the stochastic nature of resistive switching in Cu doped Ge0.3Se0.7 based memory devices

J. Appl. Phys. **110**, 054509 (2011); 10.1063/1.3631013

The growth of metallic nanofilaments in resistive switching memory devices based on solid electrolytes Appl. Phys. Lett. **94**, 153504 (2009); 10.1063/1.3118574

Reliability analysis of the low resistance state stability of Ge 0.3 Se 0.7 based solid electrolyte nonvolatile memory cells

Appl. Phys. Lett. 94, 123503 (2009); 10.1063/1.3103555

## Re-register for Table of Content Alerts

Create a profile.

Sign up today!

# Rate limiting step for the switching kinetics in Cu doped Ge<sub>0.3</sub>Se<sub>0.7</sub> based memory devices with symmetrical and asymmetrical electrodes

R. Soni, <sup>1,a)</sup> P. Meuffels, <sup>2</sup> A. Petraru, <sup>1</sup> O. Vavra, <sup>1</sup> and H. Kohlstedt <sup>1</sup> Nanoelektronik, Technische Fakultät Kiel, Christian-Albrechts-Universität Kiel, Kiel 24143, Germany <sup>2</sup> Peter Grünberg Institut, Forschungszentrum Jülich GmbH, Jülich 52425, Germany

(Received 25 February 2013; accepted 11 March 2013; published online 26 March 2013)

We report on the comparison of the resistance switching properties and kinetic behavior of Cu doped  $Ge_{0.3}Se_{0.7}$  solid electrolyte based dual layer memory devices integrated with asymmetrical (Pt and Cu) and symmetrical electrodes (only Cu). In spite of the fact that the observed resistance switching properties and its parameters are quite similar for both memory devices, the dependence of the SET-voltage on the voltage sweep rate suggests different microscopic rate limiting factors for the resistance switching behavior. Additionally, in order to alleviate the cross talk problem in passive crossbar arrays, a dual layer oxide stack ( $TiO_2/AI_2O_3$ ) is integrated with  $Ge_{0.3}Se_{0.7}$  based dual layer memory devices to achieve a specific degree of non-linearity in the overall resistance of the low resistance state. © 2013 American Institute of Physics. [http://dx.doi.org/10.1063/1.4797488]

#### I. INTRODUCTION

In the last decade, the resistance switching based memory device concept, commonly known as resistance random access memory (RRAM), has evoked great interest within the scientific community as a potential candidate for nonvolatile random access memories, passive crossbar arrays, and neuromorphic computational architectures. <sup>1-9</sup> A lot of promising results have already been reported on single structure resistive switching memory cells integrating a large variety of oxides and solid electrolytes. 10 Some of the most attractive properties of resistance switching memory devices are low power consumption, low threshold voltages, scalability into the nanometer regime, fast write and read access, and low fabrication costs. 10 Thin oxide films such as SiO2, 11  ${

m TiO_2}^{12}$  as well as solid electrolyte materials such as Ag and Cu doped amorphous Ge-Se,  $^{13,14}$  Ge-S,  $^{15}$  and (Zn, Cd)S $^{16}$ are some of the most promising candidates in the race for future RRAM cells. The macroscopic origin of the resistance switching "ON" process in the solid electrolyte material systems, when sandwiched between an electrochemically active metal, such as Ag or Cu, and an electrochemically inert counter electrode, such as Pt or Au, is proposed to be an electrochemical formation of metallic filaments. 10 Under an applied positive bias at the oxidizable electrode (e.g., Cu or Ag), the filament formation process ("SET" process) in the memory cell is supposed to consist of three steps: (1) anodic dissolution of Cu or Ag according to  $M \rightarrow M^{z+} + ze^-$ , where Mz+ represents the Cu or Ag metal cations in the thin electrolyte film, (2) drift of the metal cations in the electrolytes under the action of the high electric field, (3) cathodic reaction at the inert electrode,  $M^{z+} + ze^- \rightarrow M$ , involving the nucleation and growth processes of the metallic filament.<sup>10</sup> Despite recent progress, there remain some open questions and challenges with respect to, for example, the rate limiting step in the resistance switching process, the role of the inert

In this article, we report on the resistance switching properties of Cu doped  $Ge_{0.3}Se_{0.7}$  solid electrolyte based memory devices integrated with an oxidizable Cu electrode only on the top side (bottom side is an inert Pt electrode) as well as on both sides (top and bottom). Further, the kinetics of the resistance switching process in both types of memory cells are investigated within the framework of the metallic filament growth model. Moreover, we show that by integrating an additional dual layer oxide barrier element with Cu doped  $Ge_{0.3}Se_{0.7}$  based memory devices, it is feasible to introduce a specific degree of non-linearity in the low resistance state.

#### II. EXPERIMENTAL

Single cross-point and planar structures with active areas ranging from  $2\,\mu\text{m}^2$  up to  $1600\,\mu\text{m}^2$  were fabricated using standard photolithography techniques and ion beam etching. The detailed layer sequence of the memory devices as used in this study was the following: Si/SiO<sub>2</sub> substrate/5 nm TiO<sub>2</sub>/30 nm Pt or Cu (bottom electrode)/2 nm SiO<sub>x</sub> ("with expected pin holes")/Ge<sub>0.3</sub>Se<sub>0.7</sub>/100 nm Cu (top electrode).

Si (100) wafers with a 400 nm thermal oxide and a 5 nm  $\rm TiO_2$  film as an adhesion layer for the Pt base electrode deposition were used as substrates. A 30 nm thin film of Pt (Cu) was sputtered on top and this bottom Pt (Cu) electrode was patterned by standard optical lithography and by reactive ion beam etching (RIBE). The photo-resist was removed with acetone and a buffer layer of 2 nm  $\rm SiO_x$  was deposited by radio frequency (RF) sputtering at a rate of 0.8 nm s<sup>-1</sup> followed by defining the bottom electrode contact with optical lithography and RIBE. Afterwards, the top structure of the memory cell was defined by a lift-off step. The  $\rm Ge_{0.3}Se_{0.7}$  layers were deposited by RF-sputtering followed by the deposition of the 150 nm Cu top electrode. The deposition rates

electrodes and existing crosstalk problem in crossbar arrays, which needed to be addressed before the industrial qualification of these devices.

a)Electronic mail: soro@tf.uni-kiel.de.

for the  $Ge_{0.3}Se_{0.7}$  and Cu layers were around 0.2 and 0.5 nm s<sup>-1</sup>, respectively. Finally, a lift-off in acetone was used to finalize the device structure. All electrical measurements were done using an Agilent B1500 semiconductor parameter analyzer.

The very thin  $SiO_x$  buffer layer "with expected pinholes (or weak links)" was introduced between the Cu-Ge-Se layer and the Pt (Cu) bottom electrode to improve the switching characteristics such as endurance and retention. As shown in Ref. 14, introducing a 2 nm  $SiO_x$  buffer layer does not affect the switching voltage which indicates the film has pin holes (or weak links). As a test of the robustness of the thin  $SiO_x$  layer, we measured the current-voltage characteristics of  $Pt/SiO_x$  (2 nm)/Cu cells. The devices were found short which further indicates the thin  $SiO_x$  buffer layer having pin holes (or weak links). We believe that a 2 nm  $SiO_x$  film "with expected pin holes" basically controls the overgrowth of the filament during repeated switching cycles and, hence, improves the resistive switching characteristics.

#### **III. RESULTS AND DISCUSSION**

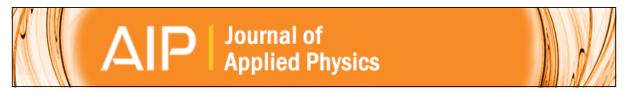

Figure 1(a) shows the current-voltage (I-V) and corresponding resistance-voltage (R-V) characteristics of a memory cell, Pt/SiO<sub>x</sub>/Ge<sub>0.3</sub>Se<sub>0.7</sub>/Cu, measured at room temperature. A quasi-static voltage sweep with bias on the top Cu electrode and grounded bottom electrode was applied to the memory cell, starting from 0 V to 0.5 V, then from 0.5 V to -0.2 V and back to 0 V again, at a sweep rate of 0.05 V/s. A current compliance of 100  $\mu$ A was set during the run to avoid complete breakdown of the memory cell. The typical  $R_{\rm off}/R_{\rm on}$  ratio ( $R_{\rm off}$  and  $R_{\rm on}$  correspond to the resistances of the high and low resistance states, respectively) of these memory cells written with a programming current of 100  $\mu$ A was found to be in the range of  $10^4$ – $10^5$ . One of the major reliability issues for RRAM and logic devices is data retention which is defined as

the ability of a memory cell to retain stored data between the time for writing and subsequent reading of the stored information. The retention behavior of both the high and low resistance states was measured at a temperature of 120 °C with 50 mV of constant applied voltage to the memory cell. As shown in Figure 1(b), there is no degradation of the resistance states up to approximately 10<sup>4</sup> s waiting time. Further details on the memory device properties such as endurance, nanoampere switching, reliability and random telegraph noise, etc., can be found in Refs. 14, 17, and 18.

As shown by Schindler *et al.*, <sup>19</sup> one can get information on the kinetics of the "SET" process by potentio-dynamic *I-V* measurements at different voltage sweep rates. It is proposed that the switching voltage,  $V_{\rm SET}$ , depends on the voltage sweep rate  $\vartheta$  as follows:

$$V_{SET} = \frac{k_B T}{\alpha z e} \ln \vartheta + \frac{kT}{\alpha z e} \ln \frac{Q_{SET} \alpha z e}{i_0 \pi r_f^2 k_B T}, \tag{1}$$

where  $i_0$  is the exchange current density,  $\alpha$  is the cathodic charge transfer coefficient,  $k_{\rm B}$  is the Boltzmann constant, e is the elementary charge, and T is the temperature.  $Q_{\text{SET}}$  is the charge needed for the one-dimensional growth of a Cu filament and  $\pi r_{\rm f}^2$  corresponds to the tip area of the growing filament with radius  $r_{\rm f}$ . Therefore, we investigated the  $V_{\rm SET}$ dependence on the voltage sweep rate during quasi static I-V measurements. Figure 1(c) shows the observed dependence of  $V_{\rm SET}$  for medium up to high voltage sweep rates, measured on Pt/SiO<sub>x</sub>/Ge<sub>0.3</sub>Se<sub>0.7</sub>/Cu based memory devices. A clear exponential relationship between the switching voltage and the voltage sweep rate is observed at high sweep rates. There seems to be a threshold voltage for low voltage sweep rates probably originating from a nucleation overpotential. Further, according to Eq. (1), one expects a logarithmic dependence of the switching voltage  $V_{\rm SET}$  on the solid electrolyte film thickness. 19 As for thicker films longer filaments

FIG. 1. Pt/SiO<sub>x</sub>/Ge<sub>0.3</sub>Se<sub>0.7</sub>/Cu: (a) Typical *I-V* (*R-V*) characteristics of a memory cell measured at room temperature with a 100  $\mu$ A compliance current setting. (b) Retention of the resistance states measured at 120 °C. The cell was written with 100  $\mu$ A programming current and read at 50 mV. (c) Dependence of the SET-voltage  $V_{\rm SET}$  on the voltage sweep rate measured at room temperature. (d) Dependence of  $V_{\rm SET}$  on the Ge<sub>0.3</sub>Se<sub>0.7</sub> film thickness at a sweep rate of 0.05 V/s measured at room temperature.

have to grow, it requires more Cu atoms, and, hence, more charge  $Q_{\rm SET}$  has to be supplied. The dependence of the switching voltage  $V_{\rm SET}$  on the  $Ge_{0.3}Se_{0.7}$  film thickness was investigated quasi-statically with a sweep rate of 0.05 V/s at room temperature. As expected, a logarithmic dependence was observed for  $Ge_{0.3}Se_{0.7}$  films with thicknesses ranging from 60 nm to 120 nm (see Fig. 1(d)).

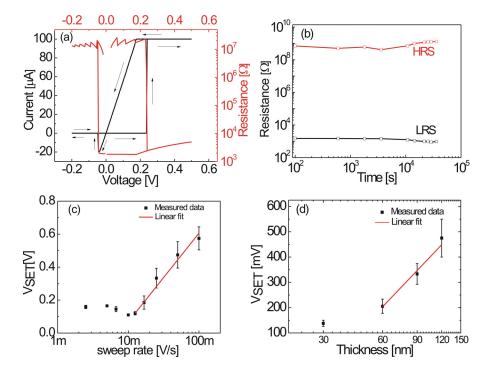

In order to understand the importance of an inert counter electrode in the resistance switching process, we investigated devices with oxidizable Cu as top and bottom electrodes. Before going further, it is important to point out that, even at room temperature, Cu dissolves easily in amorphous germanium chalcogenide films of micrometer thickness.<sup>20</sup> Therefore, it is not possible to realize a pure thin Ge<sub>0.3</sub>Se<sub>0.7</sub> film integrated non-volatile memory device with symmetrical active Cu electrodes. However, in case of dual layer memory devices, the SiO<sub>x</sub> buffer layer "with expected pin holes" (or weak links) limits the Cu dissolution in amorphous germanium chalcogenide films in abundance and, hence, makes it feasible to use symmetrical active Cu electrodes.<sup>21</sup> Figure 2(a) shows a typical current-voltage and corresponding resistance-voltage characteristics of a dual layer memory device, Cu(bottom electrode)/SiO<sub>x</sub>/Ge<sub>0.3</sub>Se<sub>0.7</sub>/ Cu(top electrode), with bias applied on the top Cu electrode and grounded bottom electrode. The typical  $R_{\text{off}}/R_{\text{on}}$  ratios  $\sim 10^3 - 10^4$  of memory devices with symmetrical oxidizable Cu electrodes were found to be comparable with those of devices with asymmetrical electrodes. Essential characterizations for

FIG. 2. Cu/SiO<sub>x</sub>/Ge<sub>0.3</sub>Se<sub>0.7</sub>/Cu: (a) Typical *I-V* (*R-V*) characteristics of a memory cell measured at room temperature with a  $100\,\mu\text{A}$  compliance current setting. (b) Dependence of the SET-voltage  $V_{\text{SET}}$  on the voltage sweep rate measured at room temperature.

RRAM non-volatile memories such as endurance, retention, and multilevel switching were performed at room temperature on these memory devices. Initial measurements have shown a promising endurance behavior of 500 cycles with a retention of  $10^3 - 10^4$  s for both resistance states and the possibility of multibit data storage due to dependence of the low resistance state on writing current (see supplementary material S1).<sup>29</sup> The observed similarities in resistance switching characteristics for both types of memory devices imply that it is not essential to have an inert counter electrode in electrochemical metallization cells.

Further, we investigated the  $V_{\rm SET}$  dependence on the voltage sweep rate to understand the rate limiting step in the resistance switching process for memory devices with symmetrical oxidizable Cu electrodes. Figure 2(b) shows the observed results which were obtained at room temperature. The dependence of  $V_{\rm SET}$  on the voltage sweep rate is completely different from that found for devices with asymmetrical electrodes. We believe that nucleation as the rate limiting step, not the filament growth, might qualitatively explain the behavior found in these resistance switching devices for the measured voltage sweep range. Further studies on the breakdown behavior of such devices under constant bias for different time ranges could shed more light on the rate limiting step in the switching process of these devices.  $^{21}$

One possible application for the above resistance switching devices would be their integration into passive crossbar-array based architectures, which are ideal building blocks for configurable logic circuits. <sup>10</sup> In spite of the simple geometrical structure and ultimate scaling potential, the use of this array based architectures has largely been blocked by the existing crosstalk problem, i.e., misreading a designated cell within a passive crossbar array due to interferences from sneak-path currents through neighbouring cells with low resistance states. As suggested before, the integration of a serial element with a particular non-linearity to each cell would solve the crosstalk problem. <sup>10</sup> For unipolar resistance switching based memory cells, this could be a rectifying diode such as a p-n junction.<sup>22</sup> However, it is not feasible to use a conventional diode for bipolar resistance switching based memory cells because the diode also prevents reverse current into the cell which is important for the bipolar switching process.<sup>23</sup> Hence, in the case of bipolar-type memory cells, more complicated varistor type-elements with specific degrees of non-linearity (high current density and threshold voltage) are required at both polarities.<sup>23</sup> Recently, different concepts such as complementary resistance switches, 24,25 inherent rectifying resistance switching elements, 26 and Schottky interface based selection devices<sup>27</sup> have also been investigated to solve crosstalk problem for bipolar resistance switching based crossbar arrays.

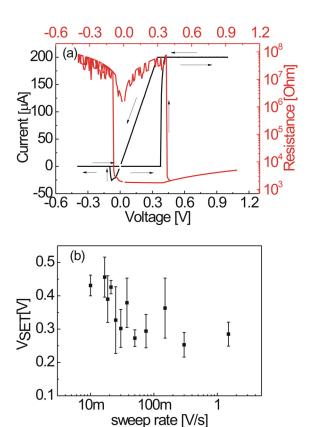

We investigated the feasibility to introduce a specific degree of non-linearity in the resistance of the low resistance state of memory cells via combining an additional dual layer oxide barrier element with Cu doped Ge<sub>0.3</sub>Se<sub>0.7</sub> based memory devices. The dual layered oxide barrier Pt (30 nm)/ TiO<sub>2</sub> (5–6 nm) /AlO<sub>2</sub> (2 nm)/Pt (30 nm) was fabricated on a Si/ SiO<sub>2</sub> substrate to introduce different non-linearities for

different polarities. At first, a 5-6 nm blanket TiO<sub>2</sub> thin film was deposited on a platinized Si substrate by reactive sputtering using a gas mixture of 77% Ar and 23%  $O_2$ . Afterwards, a thin film of  $\sim 2 \text{ nm}$  Al was sputtered on top of the TiO<sub>2</sub> film. The Al film was exposed in situ to an atmosphere of 5 mbar O2 and UV light at room temperature to prepare a thin Al<sub>2</sub>O<sub>3</sub> barrier.<sup>28</sup> Then, a 30 nm blanket Pt electrode was sputtered on top of the Al<sub>2</sub>O<sub>3</sub> film. Finally, the Ge<sub>0.3</sub>Se<sub>0.7</sub> based memory devices were fabricated on this dual layer oxide barrier stack. Figure 3 shows the resistance switching properties of Ge<sub>0.3</sub>Se<sub>0.7</sub> based memory devices integrated with a dual layered oxide barrier. As it can be seen, it was possible to achieve a specific degree of nonlinearity for the low resistance state of the combined cell. The observed  $R_{\text{off}}/R_{\text{on}}$  ratio of these devices was found to be around 10 at 500 mV, which is still reasonable to allow for small and highly efficient sense amplifiers. 10 The non-linear current-voltage characteristics of the dual layer oxide stack was measured at room temperature and is presented in the inset of Fig. 3(b). Finally, we performed the sweep endurance test on these cells and the result is shown in Fig. 3(b). The resistive switching behavior was found to be stable and reproducible for the measured 10 sweep cycles. However, in future, a detailed analysis of the transport properties is

FIG. 3. Pt/TiO<sub>2</sub>/Al2O<sub>3</sub>/Pt (dual layer oxide stack)—/SiO<sub>x</sub>/Ge<sub>0.3</sub>Se<sub>0.7</sub>/Cu (resistive switching stack): (a) Typical *I-V* (*R-V*) characteristics of Ge<sub>0.3</sub>Se<sub>0.7</sub> based memory devices integrated with a dual layered oxide barrier with a non-linear low resistance state characteristic measured at room temperature. (b) Endurance behaviour of the memory device measured at room temperature. The inset shows the typical non-linear *I-V* characteristics of the dual layer oxide stack (Pt/TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/Pt) measured at room temperature.

required to understand the non-linear behaviour of dual layer oxide stacks. At the end, it is important to point out that the non-linearity in the low resistance state can be further enhanced by optimizing the oxide barrier.

### **IV. CONCLUSION**

In summary, the resistance switching properties and kinetic behavior of Cu doped  $Ge_{0.3}Se_{0.7}$  solid electrolyte based memory devices integrated with asymmetrical (Pt and Cu) and symmetrical electrodes (only Cu) were investigated in this study. The observed similarities in resistance switching characteristics and its parameters imply that it is not essential to have inert counter electrodes in electrochemical metallization cells. However, the dependence of the SET-voltage,  $V_{\rm SET}$ , on the voltage sweep rate suggests that different rate limiting steps are involved in the resistance switching process for both memory devices. Further, a dual layer oxide stack was used to achieve a specific degree of non-linearity in the overall resistance of the low resistance state of  $Ge_{0.3}Se_{0.7}$  based memory devices.

#### **ACKNOWLEDGMENTS**

The authors would like to thank R. Waser for helpful discussions.

<sup>1</sup>R. Waser and M. Aono, Nature Mater. **6**, 833 (2007).

<sup>2</sup>T. W. Hickmott, J. Appl. Phys. 33, 2669 (1962).

<sup>3</sup>D. P. Oxely, Electrocomponent Sci. Technol. **3**, 217 (1977).

<sup>4</sup>D. H. Kwon, K. M. Kim, J. H. Jang, J. M. Jeon, M. H. Lee, G. H. Kim, X. S. Li, G. S. Park, B. Lee, S. Han, M. Kim, and C. S. Hwang, Nat. Nanotechnol. 5, 148 (2010).

K. Szot, W. Speier, G. Bihlmayer, and R. Waser, Nature Mater. 5, 312 (2006).

T. Hasegawa, K. Terabe, T. Tsuruoka, and M. Aono, Adv. Mater. 24, 252–267 (2012).

<sup>7</sup>D. S. Jeong, R. Thomas, R. S. Katiyar, J. F. Scott, H. Kohlstedt, A. Petraru, and C. S. Hwang, Rep. Prog. Phys. **75**, 076502 (2012).

<sup>8</sup>T. Ohno, T. Hasegawa, T. Tsuruoka, K. Tarabe, J. K. Gimzewski, and M. Aono, Nature Mater. 10, 591 (2011).

<sup>9</sup>M. Ziegler, R. Soni, T. Patelczyk, M. Ignatov, T. Bartsch, P. Meuffels, and H. Kohlstedt, Adv. Funct. Mater. **22**(13), 2744–2749 (2012).

<sup>10</sup>R. Waser, R. Dittmann, G. Staikov, and K. Szot, Adv. Mater. 21, 2632 (2009)

<sup>11</sup>C. Schindler, M. Weides, M. N. Kozicki, and R. Waser, Appl. Phys. Lett. 92, 122910 (2008).

<sup>12</sup>D. S. Jeong, H. Schroeder, and R. Waser, Electrochem. Solid-State Lett. 10, G51 (2007).

<sup>13</sup>M. N. Kozicki, M. Park, and M. Mitkova, IEEE Trans. Nanotechnol. 4, 331 (2005).

<sup>14</sup>R. Soni, M. Meier, A. Rüdiger, B. Holländer, C. Kügeler, and R. Waser, Microelectron. Eng. 86, 1054 (2009).

<sup>15</sup>M. N. Kozicki, M. Balakrishan, C. Gopalan, C. Ratnakumar, and M. Mitkova, in *Proceedings of the IEEE Non-Volatile Memory Technology Symposium* (2005), p. 83.

<sup>16</sup>Z. Wang, P. B. Griffin, J. McVittie, S. Wong, P. C. McIntyre, and Y. Nishi, IEEE Electron Device Lett. 28, 14 (2007).

<sup>17</sup>R. Soni, P. Meuffels, A. Petraru, M. Weides, C. Kügeler, R. Waser, and H. Kohlstedt, J. Appl. Phys. **107**, 024517 (2010).

<sup>18</sup>R. Soni, P. Meuffels, H. Kohlstedt, C. Kügeler, and R. Waser, Appl. Phys. Lett. **94**, 123503 (2009).

<sup>19</sup>C. Schindler, G. Staikov, and R. Waser, Appl. Phys. Lett. **94**, 72109 (2009).

<sup>20</sup>C. P. McHardy, A. G. Fitzgerald, P. A. Moir, and M. Flynn, J. Phys. C 20(26), 4055 (1987).

<sup>21</sup>R. Soni, P. Meuffels, G. Staikov, R. Weng, C. Kügeler, A. Petraru, M. Hambe, R. Waser, and H. Kohlstedt, J. Appl. Phys. 110, 054509 (2011).

- <sup>22</sup>M. J. Lee, S. Seo, D. C. Kim, S. E. Ahn, D. H. Seo, I. K. Yoo, I. G. Back, D. S. Kim, I. S. Byun, S. H. Kim, I. R. Hwang, J. S. Kim, S. H. Jeon, and B. H. Park, Adv. Mater. 19, 73 (2007).

- <sup>23</sup>J. Shin, I. Kim, K. P. Biju, M. Jo, J. Park, J. Lee, S. Jung, W. Lee, S. Kim, S. Park, and H. Hwang, J. Appl. Phys. **109**, 033712 (2011).

- <sup>24</sup>E. Linn, R. Rosezin, C. Kugeler, and R. Waser, Nature Mater. 9, 403 (2010).

- <sup>25</sup>R. Soni, P. Meuffels, A. Petraru, M. Hansen, M. Ziegler, O. Vavra, D. S. Jeong, and H. Kohlstedt, "Realization of complementary resistive switching based on 'serial' electrochemical metallization cells" (unpublished).

- <sup>26</sup>C. Nauenheim, C. Kuegeler, A. Ruediger, and R. Waser, Appl. Phys. Lett. 96, 122902 (2010).

- <sup>27</sup>W. Y. Park, G. H. Kim, J. Y. Seok, K. M. Kim, S. J. Song, M. H. Lee, and C. S. Hwang, Nanotechnology 21, 195201 (2010).

- <sup>28</sup>P. Rottlander, H. Kohlstedt, H. de Gronckel, E. Girgis, J. Schelten, and P. Grunberg, J. Magn. Magn. Mater. 210, 251 (2000).

- <sup>29</sup>See supplementary material at http://dx.doi.org/10.1063/1.4797488 for "Rate limiting step for the switching kinetics in Cu doped Ge<sub>0.3</sub>Se<sub>0.7</sub> based memory devices with symmetrical and asymmetrical electrodes."