## Ferroelectric field effect transistors using very thin ferroelectric polyvinylidene fluoride copolymer films as gate dielectrics

A. Gerber, M. Fitsilis, R. Waser, Timothy J. Reece, E. Rije, Stephen Ducharme, and H. Kohlstedt

Citation: Journal of Applied Physics 107, 124119 (2010);

View online: https://doi.org/10.1063/1.3437638

View Table of Contents: http://aip.scitation.org/toc/jap/107/12

Published by the American Institute of Physics

## Articles you may be interested in

Physics of the ferroelectric nonvolatile memory field effect transistor Journal of Applied Physics **72**, 5999 (1998); 10.1063/1.351910

Ferroelectric thin films: Review of materials, properties, and applications Journal of Applied Physics **100**, 051606 (2006); 10.1063/1.2336999

Electrical characteristics of MoS<sub>2</sub> field-effect transistor with ferroelectric vinylidene fluoride-trifluoroethylene copolymer gate structure

Applied Physics Letters 108, 132903 (2016); 10.1063/1.4945327

Low-voltage polymer field-effect transistors for nonvolatile memories Applied Physics Letters 87, 203509 (2005); 10.1063/1.2132062

High-κ gate dielectrics: Current status and materials properties considerations Journal of Applied Physics **89**, 5243 (2001); 10.1063/1.1361065

Spin cast ferroelectric beta poly(vinylidene fluoride) thin films via rapid thermal annealing Applied Physics Letters **92**, 012921 (2008); 10.1063/1.2830701

## Ferroelectric field effect transistors using very thin ferroelectric polyvinylidene fluoride copolymer films as gate dielectrics

A. Gerber, <sup>1,a)</sup> M. Fitsilis, <sup>1</sup> R. Waser, <sup>1</sup> Timothy J. Reece, <sup>2</sup> E. Rije, <sup>3</sup> Stephen Ducharme, <sup>2</sup> and H. Kohlstedt <sup>4,b)</sup>

<sup>1</sup>Institute of Solid State Research (IFF), Center of Nanoelectronic Systems for Information Technology (CNI), Research Center Jülich, 52425 Jülich, Germany

<sup>2</sup>Department of Physics and Astronomy, Nebraska Center for Materials and Nanoscience,

University of Nebraska, Lincoln, Nebraska 68588-0299, USA

<sup>3</sup>Institute for Thin Films and Interfaces (ISG 1), Center of Nanoelectronic Systems for Information Technology (CNI), Research Center Jülich, 52425 Jülich, Germany

Technology (CNI), Research Center Jülich, 52425 Jülich, Germany

<sup>4</sup>Technische Fakultät Institut für Elektrotechnik und Informationstechnik Nanoelektronik, Christian-Albrechts-Universität zu Kiel, Kaiserstraße 2 24143 Kiel, Germany

(Received 23 February 2010; accepted 2 May 2010; published online 28 June 2010)

We report electrical characterization of memory elements consisting of a p-type silicon field-effect transistor incorporating a ferroelectric polymer Langmuir–Blodgett film into the gate insulator to produce bistability through polarization hysteresis. The thin gate insulator, consisting of a 10 nm thick silicon oxide layer and a 35 nm thick ferroelectric polymer film, enabled bistable operation at 4 V. Device hysteresis as a function of gate voltage was evident both in the device capacitance, which was measured between the gate and drain, and in the source-drain conductance. The ferroelectric film polarization was not saturated, even up to operating voltages of 10 V. This is likely the reason for the short state retention of less than 10 s at room temperature. The hysteresis vanished as the sample was heated toward the ferroelectric-paraelectric phase transition temperature, showing that the bistability was due to ferroelectric polarization reversal. © 2010 American Institute of Physics. [doi:10.1063/1.3437638]

If the gate dielectric of a conventional metal-oxidesemiconductor field effect transistor (MOSFET) is replaced by a ferroelectric material, a so-called ferroelectric FET (FeFET) is obtained. The reversal of polarization in the ferroelectric layer is used to alter the resistance of the semiconductor source-drain channel, which defines the computational "0" and "1." The ferroelectric film state is stable even without power, making the FeFET a versatile nonvolatile memory element. Currently, available ferroelectric memories use a switchable capacitor design. The state of a bit is set with a voltage pulse and read out by applying another voltage pulse and measuring the switching current. This scheme has several drawbacks. In particular, it requires four to six elements per bit, taking up much space on the chip, and readout is destructive, so that it is slow and requires excess energy to operate. The advantages of the FeFET include a small footprint (only 1 transistor per bit), fast read, write and erase cycles of a nanosecond or less, low power consumption, and long device lifetime. Surprisingly, although the development of the first FeFET goes back to 1963,<sup>2</sup> there is still no commercial product available up to now. So far, most studies of FeFETs have focused on inorganic complex oxide and fluoride ferroelectrics, e.g., PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>, SrBa<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>, or BiMgF<sub>4</sub>, on a silicon complementary MOS platform. One of the technical difficulties with these materials is due to interdiffusion and chemical reaction between the stack interfaces at the high deposition temperatures and high oxygen

pressures used for deposition of the ferroelectric film. These processes produce poorly defined interfaces and uncompensated trap charges, thus, reducing the performance, reliability, and longevity of devices. The incorporation of an additional high-k oxide buffer layer to make the metal-ferroelectric-insulator-semiconductor (MFIS) stack structure has partially mitigated these problems, at the cost of increased fabrication complexity. Moreover, the insufficient compensation of the ferroelectric bound charge on the semi-conductor side leads to a high depolarization field that destabilizes the film polarization and leads to electron injection. Both mechanisms tend to make the device states indistinguishable and are likely responsible for the limited FeFET state retention times of a few days or less. 5-7

Ferroelectricity is found in various material classes besides complex oxides. One promising material class is ferroelectric polymers, such as polyvinylidene fluoride (PVDF) and its copolymers with, e.g., trifluoroethylene, P(VDF-TrFE).8 Ferroelectric polymers are chemically benign and do not require high temperature deposition and processing methods. They are also inexpensive, easily handled, and thin films are readily fabricated with common solvent methods. Further, the low dielectric constant of order 10 and low saturated polarization of approximately 0.1 C/m<sup>2</sup> make the material appropriate for incorporation within FeFET devices on a silicon platform. Despite an encouraging early demonstration of capacitor and FeFET memory elements based on P(VDF-TrFE), there has been little work on this technology until a few years ago. 10,11 More recent work takes the promising step of integrating the ferroelectric polymer

a) Electronic mail: sducharme1@unl.edu.

b)Present address: Nanoelektronik, Technische Fakultät Kiel, Christian-Albrechts-Universität Kiel, Kiel 24143, Germany.

with organic semiconductors. <sup>12–19</sup> The low processing temperatures for the polymer films, deposition at 25 °C and annealing at 130 °C, should have no deleterious effects on the semiconductor and metal components of the device. This is an important advantage compared to oxide ferroelectrics, which require high temperature processing in oxygen to optimize the composition and structure of the ferroelectric layers. Copolymers of PVDF are thermally sensitive, however, with melting points in the range 145 to 220 °C, <sup>20</sup> so standard MOS procedures need to be modified for compatibility reasons during device fabrication.

One of the drawbacks of PVDF and its copolymers is the high coercive field, the minimum electric field required to reverse the polarization state. With coercive fields of 50 MV/m and higher,<sup>21</sup> films must be quite thin, less than 100 nm, to allow for operation voltages below 5 V. The early devices, for example, required up to 200 V to operate, while the more recent examples still require 30 V or more. 11-14,16-18,22 A proven means of making ultrathin films of P(VDF-TrFE) is Langmuir-Blodgett (LB) deposition on silicon wafers, which has produced ferroelectric films as thin as one nanometer<sup>23</sup> and nonvolatile memory devices operating at less than 10 V.18,24-26 This report describes the successful low-voltage operation of a silicon-based FeFET nonvolatile memory device with a gate insulator consisting of a 35 nm thick P(VDF-TrFE) LB film and a 10 nm thick SiO<sub>2</sub> layer, operating in the low-voltage range between ±5 V.

The FeFET devices were fabricated on Silicon (100) oriented, p-type (boron, concentration  $\approx 4 \times 10^{15}$  cm<sup>-3</sup>), 6 in. wafers. First, the drain and source regions 300 by 300  $\mu$ m were defined by photolithography. Then, As<sup>+</sup> dopants were implanted into the source and drain regions using an Axcelis Ion Implanter with an accelerator energy of 30 keV. The simulated ion concentration depth profile for the applied parameters predicted a donor concentration of  $2 \times 10^{20}$  cm<sup>-3</sup> and a maximum ion penetration of 80 nm within the source and drain regions. After implantation, the wafer was cleaned by using the RCA cleaning procedure for organics.<sup>27</sup> An annealing step at 1000 °C in a nitrogen atmosphere was used for 1 min to activate the ions. After an additional cleaning procedure, an SiO2 gate oxide was grown at 700 °C for 1 h in O2 using a wet oxidation process followed by a forming gas (N<sub>2</sub>H<sub>2</sub>) annealing step at 450 °C for 15 min to passivate dangling bonds, which otherwise can act as charge traps. The thickness of the SiO<sub>2</sub> layer was determined by ellipsometry to be approximately 10 nm. The source and drain contacts were fabricated by first defining the contact area with photolithography, etching with buffered HF solution to remove the SiO<sub>2</sub> layer, and depositing the platinum contacts by sputtering. The remaining photoresist and excess platinum were then washed off. By these means, FETs with different channel areas were fabricated lacking only the ferroelectric film and gate contact. The 6 in. wafer was then cut into 1 cm<sup>2</sup> pieces.

The photolithography, implantation, and high temperature MOS processing steps were completed before deposition of the temperature-sensitive ferroelectric copolymer. The ferroelectric film consisted of a random copolymer of 70% VDF and 30% TrFE with a weight-averaged average mo-

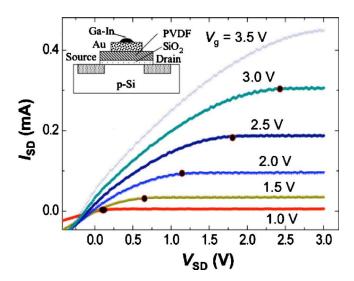

FIG. 1. (Color online) Source-drain current  $I_{\rm SD}$  curves for an Au/PVDF/SiO<sub>2</sub>/p-Si FeFET are shown with their dependency on the gate voltage values as shown. Inset: FeFET device diagram.

lecular weight of 100 000. It was deposited directly on the prepared silicon wafer by horizontal LB deposition from an ultrapure water (18  $M\Omega$  cm) subphase at a surface pressure of 5 mN/m, as describe in greater detail elsewhere.  $^{28}$  The films were formed from 25 LB transfers, which under these conditions produces films with thickness 44  $\pm$  2 nm.  $^{29}$  The samples were subsequently annealed at 130  $^{\circ}$ C for 1 h to improve the crystallinity of the copolymer. Au gate electrodes with various dimensions were deposited by vacuum evaporation through a shadow mask to complete the Au/PVDF/SiO $_2/p$ -Si stack. The inset diagram in Fig. 1 shows the cross-section of the device.

For electrical characterization, a low-resistance side contact was made to the silicon. Both top and side electrodes were connected via gold probe tips. The Au top electrode was first covered with a liquid metal GaIn eutectic, which was contacted with a needle. This method allows minimizing mechanical stress on the polymer film during electrical characterization. The FeFET measurements were performed with a semiconductor parameter analyzer at room temperature in a dark environment (a shielded metal box).

The FETs exhibited excellent current-voltage characteristics for gate voltage  $V_{\rm g}$  ranging from 0 to +3.5 V, as shown in Fig. 1, for a channel area of 25×25  $\mu$ m<sup>2</sup>. The source-drain current  $I_{\rm SD}$  increased linearly with the source-drain voltage  $V_{\rm SD}$  at first and then tended toward saturation. The flat saturation currents are an indication of low leakage current between gate electrode and substrate and means that the PVDF/SiO<sub>2</sub> gate double layer is highly resistive.

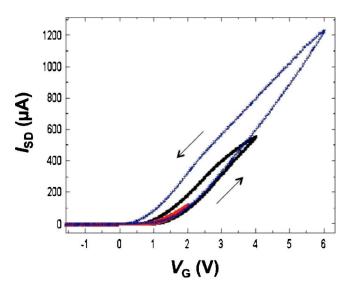

The state bistability of the FeFET is best probed by measuring the source-drain current  $I_{\rm SD}$  as the gate voltage  $V_{\rm g}$  is cycled, while the source-drain voltage is kept low, in the linear  $I_{\rm SD}$  versus  $V_{\rm SD}$  region. Figure 2 shows the growth of hysteresis in the source-drain conductance with increasing amplitude of the gate voltage  $V_{\rm g}$ . The hysteresis is due to the cycling between two opposing polarization states of the ferroelectric film. Although a symmetric gate voltage  $V_{\rm g}$  cycle of up to  $\pm 6$  V was applied, for simplicity only the

FIG. 2. (Color online) Source-drain current  $I_{\rm SD}$  vs applied gate voltage  $V_{\rm g}$  for an Au/PVDF/SiO<sub>2</sub>/p-Si FeFET for different maximal gate voltages. The gate voltage was cycled between  $\pm 2$ ,  $\pm 4$ , and  $\pm 8$  V. The source-drain voltage was  $V_{\rm SD}$ =0.1 V.

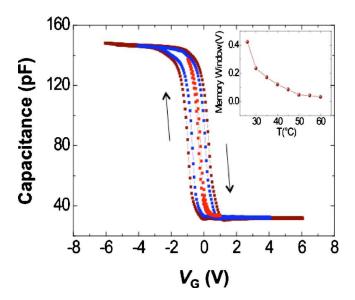

interval between -1.5 V and +6 V is shown because there was negligible conductance with negative gate bias. A small  $V_g$  sweep of  $\pm 2$  V produces a very small hysteresis loop (the small center loop in Fig. 2) with width < 100 mV whereas a large  $V_g$  sweep  $\pm 14$  V results in a width of 3 V (the largest loop in Fig. 2). The width of the hysteresis loop is called the memory window and is one of the most important characteristics of an FeFET memory element. The memory window is also evident in measurements of device capacitance C versus gate voltage  $V_g$  as in an MFIS,  $^{24}$  as shown in Fig. 3. Accumulation is attained at negative gate bias, resulting in a high device capacitance, while depletion is achieve at positive gate bias, resulting in low capacitance. The cross-over between accumulation and depletion is shifted from zero gate

FIG. 3. (Color online) Capacitance-voltage hysteresis loops of a Pt/PVDF/SiO\_2/p-Si gate MFIS stack diode measured with gate voltage sweeps over  $\pm 1,~\pm 4$  and  $\pm 6~V$  at a rate of 0.05 V/s. The measurement frequency was 100 kHz. The inset shows the width of the memory window as a function of temperature for gate voltage sweeps over  $\pm 5~V$ .

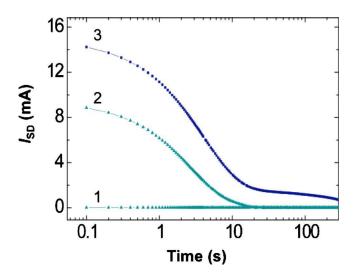

FIG. 4. (Color online) Source-drain current  $I_{SD}$  measured at zero gate bias and  $V_{SD}$ =0.1 V after setting the device state with a gate bias of  $\pm 5$  V. Curve 1 was measured after applying a gate bias of -5 V for 2 min. Curves 2 and 3 were measured after applying a gate bias of +5 V for 2 min and 20 min. respectively.

bias by the polarization state of the ferroelectric film. The MFIS memory window increases linearly from 0.15 to 1.3 V as the gate voltage cycle amplitude increased from  $\pm 1$  V to  $\pm 6$  V, as shown in Fig. 3. A larger memory window indicates higher remanent polarization in the ferroelectric film.

A large memory window, however, is not sufficient for practical FeFET operation. The state retention, i.e., the capability to maintain either the "on" or "off" state for a sufficiently long time, is another important issue. State retention in FeFETs can be limited by instability in the ferroelectric film polarization or by charge leakage and trapping in the insulating layers, or both. The state retention in the polymer FeFET was measured by monitoring the source-drain current  $I_{SD}$  (for  $V_{SD}$ =0.1 V) at zero gate bias after setting either the on or off states with  $\pm 5$  V pulses of duration 2 or 20 min. The on state showed retention times of only a few minutes after state-setting bias voltage pulses of +5 V for 2 or 5 min, as shown in Fig. 4. Relaxation of the remanent polarization would reduce the source-drain conductance but so would leakage and charge trapping in the insulator or ferroelectric layers, and therefore, retention measurements alone are not sufficient to identify which of these mechanisms is dominant. An appreciable source-drain current will only be measured when the condition of strong inversion at the silicon surface is met. Once the ferroelectric polarization in the off state falls so that this condition is no longer met, the on and off states of the FeFET are indistinguishable even if the on state is completely stable. Therefore, the capacitance state retention study that was previously reported<sup>24</sup> is better suited for a discussion of the dominant mechanisms for state relaxation. Since the capacitance hysteresis (Fig. 3) is highly symmetric we can conclude that charge trapping is not significant and that state retention is primarily limited by polarization stability.<sup>24,30</sup> (Charge injection is a much bigger problem oxide ferroelectrics, which are in semiconductors.<sup>31</sup>) Nevertheless, this hypothesis needs further study to clarify the mechanisms for retention in FeFETs,

and properly prescribe a remedy. Polarization stability is best improved by providing better charge compensation at the surfaces of the ferroelectric film. This can be accomplished by further reducing the thickness of the oxide layer so that its capacitance is at least ten times that of the ferroelectric film.

In summary, we fabricated ferroelectric FETs with the copolymer P(VDF-TrFE) integrated in the gate-stack of a p-type silicon FET. The copolymer film was deposited by the LB technique to produce a thin high-quality ferroelectric film. Functional bistable FeFETs were operated with low gate bias voltage ranges from  $\pm 2$  to  $\pm 6$  V. A hysteresis in the  $I_{\rm SD}$  versus  $V_{\rm g}$  characteristics was observed which represented the remanent polarization of the ferroelectric polymer. We observed retention times of less than 10 s, which likely is limited by incomplete polarization saturation.

We thank Nicholas Pertsev and Jürgen Schubert for helpful discussions. This work was supported by Volkswagen-Stiftung (www.volkswagenstiftung.de) within the program "Complex Materials: Cooperative Projects of the Natural, Engineering, and Biosciences" under the title: "Nano-sized ferroelectric Hybrids" Under Project No. 1/77 737. Work at the University of Nebraska was supported by the USA National Science Foundation (Grant No. ECS-0600130).

- <sup>2</sup>J. L. Moll and Y. Tarui, IEEE Trans. Electron Devices **10**, 338 (1963).

- <sup>3</sup>H. Kohlstedt and H. Ishiwara, in *Nanoelectronics and Information Technology*, edited by R. Waser (Wiley-VCH, Weinheim, 2002), p. 387.

- <sup>4</sup>I. P. Batra and B. D. Silverman, Solid State Commun. 11, 291 (1972).

- <sup>5</sup>E. Tokumitsu, G. Fujii, and H. Ishiwara, Jpn. J. Appl. Phys., Part 1 **39**, 2125 (2000)

- <sup>6</sup>T. P. Ma and J.-P. Han, IEEE Electron Device Lett. 23, 386 (2002).

- <sup>7</sup>H. Kohlstedt, Y. Mustafa, A. Gerber, A. Petraru, M. Fitsilis, R. Meyer, U. Böttger, and R. Waser, Microelectron. Eng. **80**, 296 (2005).

- <sup>8</sup>K. Tashiro, in *Ferroelectric Polymers*, edited by H. S. Nalwa (Dekker, New York, 1995), pp. 63–181.

- <sup>9</sup>N. Yamauchi, Jpn. J. Appl. Phys., Part 1 **25**, 590 (1986).

- <sup>10</sup>T. J. Reece, S. Ducharme, A. V. Sorokin, and M. Poulsen, Appl. Phys.

- Lett. 82, 142 (2003).

- S. H. Lim, A. C. Rastogi, and S. B. Desu, J. Appl. Phys. 96, 5673 (2004).

G. H. Gelinck, A. W. Marsman, F. J. Touwslager, S. Setayesh, D. M. de Leeuw, R. C. G. Naber, and P. W. M. Blom, Appl. Phys. Lett. 87, 092903 (2005).

- <sup>13</sup>R. C. G. Naber, C. Tanase, P. W. M. Blom, G. H. Gelinck, A. W. Marsman, F. J. Touwslager, S. Setayesh, and D. M. de Leeuw, Nature Mater. 4, 243 (2005).

- <sup>14</sup>J. Chang, C. H. Shin, Y. J. Park, S. J. Kang, H. J. Jeong, K. J. Kim, C. J. Hawker, T. P. Russell, D. Y. Ryu, and C. Park, Org. Electron. **10**, 849 (2009).

- <sup>15</sup>N. T. Tien, Y. G. Seol, L. H. A. Dao, H. Y. Noh, and N.-E. Lee, Adv. Mater. (Weinheim, Ger.) 21, 910 (2009).

- <sup>16</sup>S. J. Kang, I. Bae, Y. J. Park, T. H. Park, J. Sung, S. C. Yoon, K. H. Kim, D. H. Choi, and C. Park, Adv. Funct. Mater. 19, 1609 (2009).

- <sup>17</sup>K. H. Lee, G. Lee, K. Lee, M. S. Oh, and S. Im, Appl. Phys. Lett. **94**, 093304 (2009).

- <sup>18</sup>C. A. Nguyen, J. Wang, L. Chen, S. G. Mhaisalkar, and P. S. Lee, Org. Electron. **10**, 145 (2009).

- <sup>19</sup>R. C. G. Naber, K. Asadi, P. W. M. Blom, D. M. d. Leeuw, and B. d. Boer, Adv. Mater. (Weinheim, Ger.) 21, 1 (2009).

- <sup>20</sup>T. T. Wang, J. M. Herbert, and A. M. Glass, *The Applications of Ferroelectric Polymers* (Blackie/Chapman and Hall, Glasgow, New York,

- <sup>21</sup>S. Ducharme, V. M. Fridkin, A. V. Bune, S. P. Palto, L. M. Blinov, N. N. Petukhova, and S. G. Yudin, Phys. Rev. Lett. 84, 175 (2000).

- <sup>22</sup>C. W. Choi, A. A. Prabu, Y. M. Kim, S. Yoon, K. J. Kim, and C. Park, Appl. Phys. Lett. 93, 182902 (2008).

<sup>23</sup>A. V. Bune, V. M. Fridkin, S. Ducharme, L. M. Blinov, S. P. Palto, A. V.

- <sup>23</sup> A. V. Bune, V. M. Fridkin, S. Ducharme, L. M. Blinov, S. P. Palto, A. V. Sorokin, S. G. Yudin, and A. Zlatkin, Nature (London) 391, 874 (1998).

- <sup>24</sup>A. Gerber, M. Fitsilis, H. Kohlstedt, R. Waser, T. J. Reece, S. Ducharme, and E. Rije, J. Appl. Phys. **100**, 024110 (2006).

- <sup>25</sup>S. Fujisaki, H. Ishiwara, and Y. Fujisaki, Appl. Phys. Lett. **90**, 162902 (2007)

- <sup>26</sup>S. Fujisaki, H. Ishiwara, and Y. Fujisaki, Appl. Phys. Express 1, 081801 (2008).

- <sup>27</sup> Handbook of Semiconductor Wafer Cleaning Technology: Science, Technology, and Applications, edited by W. Kern (Noyes Publications, Westwood, NJ, 1993).

- <sup>28</sup>S. Ducharme, S. P. Palto, and V. M. Fridkin, in *Ferroelectric and Dielectric Thin Films*, edited by H. S. Nalwa (Academic, San Diego, 2002), Vol. 3, pp. 545–591.

- <sup>29</sup> M. Bai, A. V. Sorokin, D. W. Thompson, M. Poulsen, S. Ducharme, C. M. Herzinger, S. Palto, V. M. Fridkin, S. G. Yudin, V. E. Savchenko, and L. K. Gribova, J. Appl. Phys. 95, 3372 (2004).

- <sup>30</sup>T. J. Reece, A. Gerber, H. Kohlstedt, and S. Ducharme, J. Appl. Phys. (to be published).

- <sup>31</sup>S.-Y. Wu, IEEE Trans. Electron Devices **21**, 499 (1974).

<sup>&</sup>lt;sup>1</sup>H. Ishiwara, M. Okuyama, and Y. Arimoto, in *Ferroelectric Random Access Memories: Fundamentals and Applications*, Topics in Applied Physics Vol. 93, edited by C. E. Ascheron and H. J. Koelsch (Springer-Verlag, Berlin, 2004), p. 290.