## **Characterizing Load and Communication Imbalance** in Parallel Applications

David Böhme

IAS Series Volume 23

Forschungszentrum Jülich GmbH Institute for Advanced Simulation (IAS) Jülich Supercomputing Centre (JSC)

# **Characterizing Load and Communication Imbalance in Parallel Applications**

David Böhme

Schriften des Forschungszentrums Jülich

IAS Series Volume 23

Bibliographic information published by the Deutsche Nationalbibliothek. The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

Publisher and Forschungszentrum Jülich GmbH

Distributor: Zentralbibliothek

52425 Jülich

Phone +49 (0) 24 61 61-53 68 · Fax +49 (0) 24 61 61-61 03

e-mail: zb-publikation@fz-juelich.de Internet: http://www.fz-juelich.de/zb

Cover Design: Jülich Supercomputing Centre, Forschungszentrum Jülich GmbH

Printer: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2014

Schriften des Forschungszentrums Jülich IAS Series Volume 23

D 82 (Diss., RWTH Aachen University, 2013)

ISSN 1868-8489 ISBN 978-3-89336-940-9

Persistent Identifier: urn:nbn:de:0001-2014012708

Resolving URL: http://www.persistent-identifier.de/?link=610

Neither this book nor any part of it may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage and retrieval system, without permission in writing from the publisher.

#### **Abstract**

The amount of parallelism in modern supercomputers currently grows from generation to generation, and is expected to reach orders of millions of processor cores in a single system in the near future. Further application performance improvements therefore depend to a large extend on software-managed parallelism: in particular, the software must organize data exchange between processing elements efficiently and optimally distribute the workload between them. Performance analysis tools help developers of parallel applications to evaluate and optimize the parallel efficiency of their programs by pinpointing specific performance bottlenecks. However, existing tools are often incapable of identifying complex imbalance patterns and determining their performance impact reliably. This dissertation presents two novel methods to automatically extract imbalance-related performance problems from event traces generated by MPI programs and intuitively guide the performance analyst to inefficiencies whose optimization promise the highest benefit.

The first method, the delay analysis, identifies the root causes of wait states. A delay occurs when a program activity needs more time on one process than on another, which leads to the formation of wait states at a subsequent synchronization point. Wait states, which are intervals through which a process is idle while waiting for the delayed process, are the primary symptom of load imbalance in parallel programs. While wait states themselves are easy to detect, the potentially large temporal and spatial distance between wait states and the delays causing them complicates the identification of wait-state root causes. The delay analysis closes this gap, accounting for both short-term and long-term effects. To this end, the delay analysis comprises two contributions of this dissertation: (1) a cost model and terminology to describe the severity of a delay in terms of the overall waiting time it causes; and (2) a scalable algorithm to identify the locations of delays and determine their cost.

The second new analysis method is based on the detection of the critical path. In contrast to the delay analysis, which characterizes the formation of wait states, this critical-path analysis determines the effect of imbalance on program runtime. The critical path is the longest execution path in a parallel program without wait states: optimizing an activity on the critical path will reduce the programs run time. Comparing the duration of activities on the critical path with their duration on each process yields a set of novel, compact performance indicators. These indicators allow users to evaluate load balance, identify performance bottlenecks, and determine the performance impact of load imbalance at first glance by providing an intuitive understanding of complex performance phenomena. Unlike existing statistics-based load balance metrics, these indicators are applicable to both SPMD and MPMD-style programs.

Both analysis methods leverage the scalable event-trace analysis technique employed by the Scalasca toolset: by replaying event traces in parallel, the bottleneck search algorithms can harness the distributed memory and computational resources of the target system for the analysis, allowing them to process even large-scale program runs. The scalability and performance insight that the novel analysis approaches provide are demonstrated by evaluating a variety of real-world HPC codes in configurations with up to 262,144 processor cores.

### Kurzzusammenfassung

Der Grad der Parallelverarbeitung in modernen Supercomputern wächst von Generation zu Generation, und wird in naher Zukunft Grössenordnungen von mehreren Millionen Prozessorkernen erreichen. Die Performanz der Anwendungen hängt dadurch immer stärker von der Fähigkeit der Software ab, diesen Parallelismus effizient zu steuern: insbesondere muss der Datenaustausch zwischen den Prozessen effizient organisiert und die Arbeitslast optimal auf die Prozessoren verteilt werden. Leistungsanalysewerkzeuge helfen den Anwendungsentwicklern dabei, die parallele Effizienz ihrer Anwendungen zu evaluieren und Engpässe aufzuspüren. Bisher verfügbare Werkzeuge sind allerdings in der Regel nicht in der Lage, komplexe Formen von Lastimbalancen zu identifizieren und ihre Auswirkungen auf die Leistung zuverlässig zu quantifizieren. Diese Dissertation stellt daher zwei neue Verfahren vor, um in Ereignisspuren von parallelen Programmen automatisch Lastverteilungs-Probleme zu identifizieren und so den Anwendungsentwickler zu den Schwachstellen mit dem größten Optimierungspotential zu leiten.

Das erste Verfahren, die Delay-Analyse, identifiziert die Ursachen von Wartezuständen. Ein Delay (Verzögerung) tritt auf, wenn eine Programmaktivität auf einem Prozess länger dauert als auf einem anderen und so an einem folgenden Synchronisationspunkt einen Wartezustand auslöst. Solche Wartezustände, bei denen Prozessorkapazität brach liegt, sind das Hauptsymptom von Ungleichgewichten in der Lastverteilung. Während Wartezustände an sich einfach zu erkennen sind, gestaltet sich die Identifikation der Ursachen aufgrund der potentiell grossen Distanz zwischen einem Wartezustand und dem verursachenden Delay oft schwierig. Die Delay-Analyse schließt diese Lücke. Dazu definiert die Dissertation erstens eine Terminologie und ein Kostenmodell zur Charakterisierung von Delays, und stellt zweitens einen skalierbaren Algorithmus zur Identifikation der Delays und der Berechnung ihrer Kosten vor.

Die zweite neue Analysemethode basiert auf der Extraktion des kritischen Pfades. Im Gegensatz zur Delay-Analyse, die die Entstehung von Wartezuständen beschreibt, lassen sich durch die Analyse des kritischen Pfades die Auswirkungen von Imbalancen auf die Programmlaufzeit charakterisieren. Der kritische Pfad ist der längste Ausführungspfad in einem parallelen Programm ohne Wartezustände: daher kann nur die Optimierung von Aktivitäten auf dem kritischen Pfad die Programmlaufzeit verkürzen. Darüber hinaus lassen sich durch den Vergleich der Dauer von Aktivitäten auf dem kritischen Pfad mit der durchschnittlichen Ausführungsdauer dieser Aktivitäten auf jedem Prozess kompakte Leistungsindikatoren ableiten, mit denen komplexe Leistungsprobleme intuitiv hervorgehoben werden können. Insbesondere können Lastverteilungsprobleme schnell erkannt und ihr Einfluss auf die Performanz quantifiziert werden. Anders als bisherige, statistik-basierte Ansätze lassen sich die Leistungsindikatoren sowohl für SPMD als auch für MPMD-Programme anwenden.

Beide Verfahren bauen auf der hochskalierbaren Ereignisspur-Analysetechnik des Scalasca-Toolkits auf: durch die parallele Verarbeitung der Ereignisspuren aller Prozesse können die Rechenresourcen und der verteilte Speicher der Zielplattform für die Suche nach Leistungsengpässen selbst herangezogen werden, wodurch die Analyse hochskalierender Programmläufe ermöglicht wird. Der Erkenntnisgewinn durch die neuen Analyseverfahren und ihre Skalierbarkeit werden anhand von Fallstudien mit einer Vielzahl realer HPC-Anwendungen in Konfigurationen mit bis zu 262.144 Prozessen untersucht.

## Acknowledgment

I would like to thank Prof. Marek Behr, PhD, President of the German Research School for Simulation Sciences and Scientific Director of the Aachen Institute for Advanced Study in Computational Engineering Sciences (AICES), as well as Prof. Dr. Dr. Thomas Lippert, Director of the Jülich Supercomputing Centre, for the opportunity to carry out my PhD project in these excellent research environments.

This project would not have been possible without the support and guidance of my advisor Prof. Dr. Felix Wolf, to whom I owe deep gratitude. I also thank Prof. Dr. Horst Lichter and Prof. Dr. Wolfgang Nagel for serving as second referees. Furthermore, I am grateful to Dr. Bronis R. the Supinski and Dr. Martin Schulz for hosting me at the Lawrence Livermore National Laboratory and opening additional research directions for my thesis.

Thanks are due to my colleagues at the Jülich Supercomputing Centre and the German Research School for Simulation Sciences for their help and advice on countless occasions. I would particularly like to acknowledge Dr. Markus Geimer for being an invaluable source of technical wisdom, and Marc-André Hermanns for his keen eye for details. Finally, I would like to thank my friends – especially Michael, Peter, Pavel, Zoltan, and Alexandre, to mention just a few – without whom the past years would have been only half as much fun. Last but by no means least, I am deeply grateful to my parents for their continuous love, encouragement, and absolute support during the completion of this project.

## **Contents**

| 1 | Intro | oduction 1                                  |

|---|-------|---------------------------------------------|

|   | 1.1   | Parallel Computers                          |

|   |       | 1.1.1 Hardware Architectures                |

|   |       | 1.1.2 Programming Models                    |

|   |       | 1.1.3 Execution Models                      |

|   |       | 1.1.4 Parallel Performance                  |

|   | 1.2   | Performance Analysis                        |

|   |       | 1.2.1 Objectives and Requirements           |

|   |       | 1.2.2 Performance-Analysis Techniques       |

|   |       | 1.2.3 Performance Tools                     |

|   | 1.3   | Contribution of this Thesis                 |

| 2 | Eve   | nt-Trace Analysis 17                        |

|   | 2.1   | Event-Tracing Applications                  |

|   | 2.2   | Scalasca                                    |

|   | 2.3   | The Scalasca Event Model                    |

|   |       | 2.3.1 MPI Events                            |

|   |       | 2.3.2 OpenMP Events                         |

|   | 2.4   | Wait-state Classification in Scalasca       |

|   |       | 2.4.1 Wait States in MPI Communication      |

|   |       | 2.4.2 Wait States in OpenMP Synchronization |

|   | 2.5   | Trace Analysis Methodology                  |

|   | 2.6   | Tracing Constraints and Requirements        |

| 3 | Cha   | racterizing Imbalance 31                    |

|   | 3.1   | Execution Model                             |

|   | 3.2   | Load and Communication Imbalance            |

|   | 3.3   | Patterns of Imbalance                       |

|   |       | 3.3.1 Experiment Setup                      |

|   |       | 3.3.2 Distribution across Processes         |

|   |       | 3.3.3 Interference between Imbalances       |

|   |       | 3.3.4 Transformation over Time              |

|   |       | 3.3.5 Imbalance in MPMD Programs            |

|   | 3.4   | Causes of Imbalance                         |

|   |       | 3.4.1 Program-Internal Causes               |

|   |       | 3.4.2 Program-External Causes               |

|   | 3.5   | Fliminating Imbalance                       |

|   | 3.6   | Related  | l Work                                 | 43       |

|---|-------|----------|----------------------------------------|----------|

|   | 3.7   |          | ements for Imbalance Analysis          | 45       |

|   | 5.7   | rtequir  | ements for infoundice rinarysis        |          |

| 4 | lder  | ntifvina | Root Causes of Wait States             | 49       |

|   | 4.1   |          | -State Formation Model                 | 49       |

|   |       | 4.1.1    | Wait States                            | 50       |

|   |       | 4.1.2    | Delay                                  | 51       |

|   |       | 4.1.3    | Costs                                  | 51       |

|   | 4.2   |          | Cost Calculation                       | 52       |

|   | 4.2   | 4.2.1    |                                        | 52       |

|   |       | 4.2.1    | Program Model                          | 52<br>52 |

|   |       |          | Synchronization Points and Wait States |          |

|   |       | 4.2.3    | Synchronization Intervals              | 53       |

|   |       | 4.2.4    | Causes of Wait States                  | 54       |

|   |       | 4.2.5    | Delay Costs                            | 55       |

|   |       | 4.2.6    | Wait-state Propagation Characteristics | 57       |

|   | 4.3   |          | able Delay Analysis Approach           | 58       |

|   |       | 4.3.1    | Trace Replay                           | 58       |

|   |       | 4.3.2    | Delay Detection                        | 59       |

|   |       | 4.3.3    | Visual Representation of Delay Costs   | 63       |

|   | 4.4   | Evaluat  | tion                                   | 65       |

|   |       | 4.4.1    | Zeus-MP/2                              | 65       |

|   |       | 4.4.2    | CESM Sea Ice Model                     | 68       |

|   |       | 4.4.3    | Illumination                           | 69       |

|   | 4.5   | Related  | l Work                                 | 72       |

|   |       |          |                                        |          |

| 5 | Criti | ical-Pat | th Based Performance Analysis          | 77       |

|   | 5.1   | Revisit  | ing Critical-Path Analysis             | 77       |

|   | 5.2   | Critical | I-Path Analysis Concept                | 78       |

|   |       | 5.2.1    | The Critical Path                      | 79       |

|   |       | 5.2.2    | Critical-Path Profile                  | 79       |

|   |       | 5.2.3    | Critical-Path Imbalance Indicator      | 80       |

|   |       | 5.2.4    | Performance-Impact Indicators          | 81       |

|   | 5.3   | Scalabl  | le Critical-Path Detection             | 84       |

|   | 5.4   |          | tion                                   | 86       |

|   | 5.1   | 5.4.1    | PEPC                                   | 86       |

|   |       | 5.4.2    | ddcMD                                  | 87       |

|   | 5.5   |          | l Work                                 | 89       |

|   | 3.3   | Related  | WOIR                                   | 07       |

| 6 | Con   | nparativ | ve Study                               | 91       |

|   | 6.1   | Function | onal Aspects                           | 91       |

|   |       | 6.1.1    | Functional Comparison                  | 91       |

|   |       | 6.1.2    | Suitability                            | 92       |

|   | 6.2   | Technic  | cal Aspects                            | 95       |

|   |       | 6.2.1    | Trace-Analysis Applicability           | 95       |

|   |       | 6.2.2    | Scalability                            | 98       |

|   |       |          |                                        |          |

|   |           |             |      |      |  |      |      |      | Co   | nte | nts |

|---|-----------|-------------|------|------|--|------|------|------|------|-----|-----|

|   | 6.2.3     | Limitations | <br> | <br> |  | <br> | <br> | <br> | <br> |     | 99  |

| 7 | Conclusio | n & Outlook |      |      |  |      |      |      |      | 1   | 03  |

## **List of Figures**

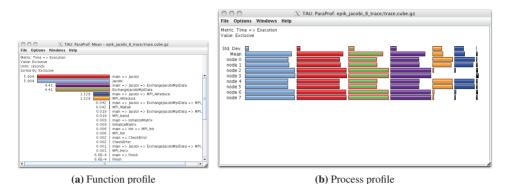

| 1.1  | Performance profile displays in TAU ParaProf                               | 13 |

|------|----------------------------------------------------------------------------|----|

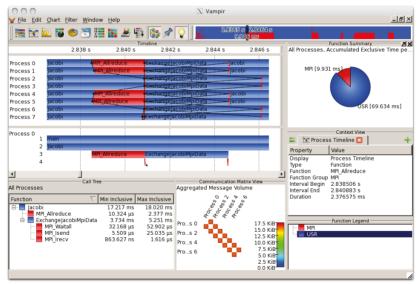

| 1.2  | Event trace displays in Vampir                                             | 13 |

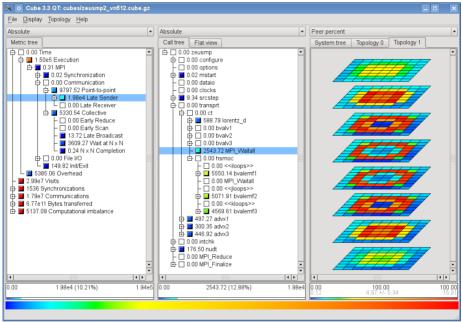

| 2.1  | The Scalasca report browser                                                | 19 |

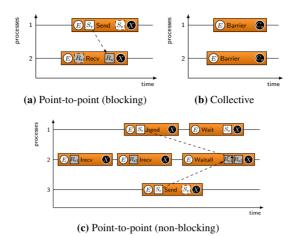

| 2.1  | Typical event sequences for MPI point-to-point communication               | 22 |

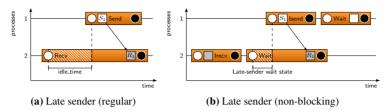

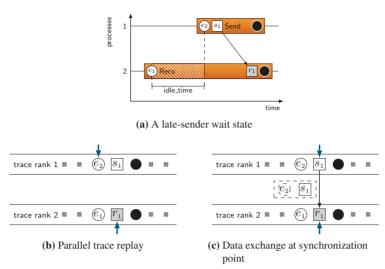

| 2.3  | Late-sender wait states                                                    | 25 |

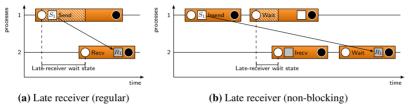

| 2.4  | Late-receiver wait states                                                  | 25 |

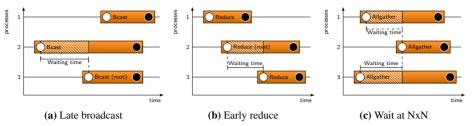

| 2.5  | Wait states in MPI collective communication.                               | 26 |

| 2.6  | Scalasca's parallel trace-analysis workflow                                | 27 |

| 2.7  | Parallel trace replay in Scalasca                                          | 28 |

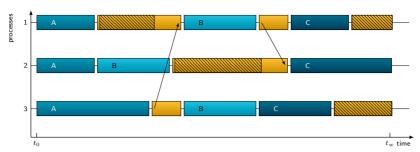

| 3.1  | Time line model of a parallel program execution                            | 32 |

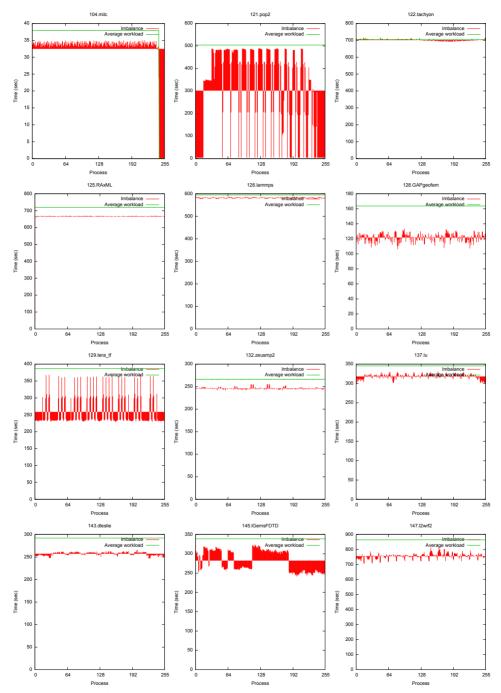

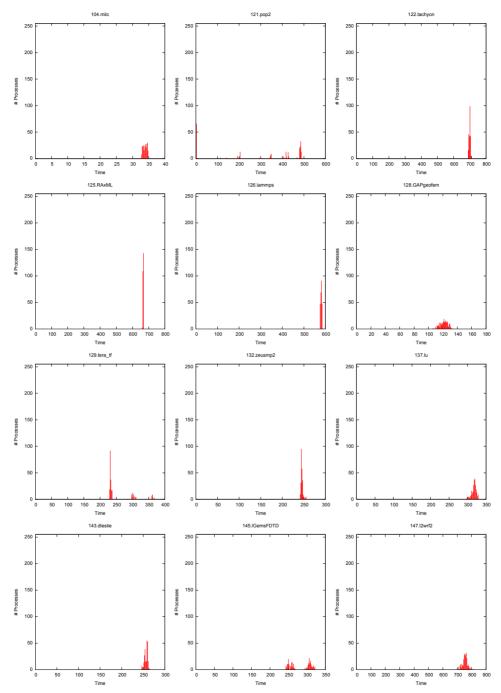

| 3.2  | Workload imbalance per processes in the SPEC MPI benchmarks                | 35 |

| 3.3  | Process workload histograms of the SPEC MPI benchmarks                     | 36 |

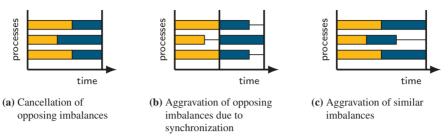

| 3.4  | Interference of superimposing imbalances in different activities           | 38 |

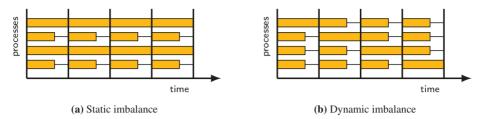

| 3.5  | Evolution of workload distribution patterns over time                      | 39 |

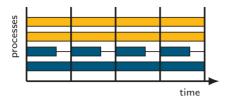

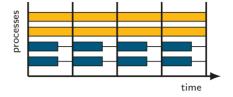

| 3.6  | Intra- and inter-partition imbalance                                       | 40 |

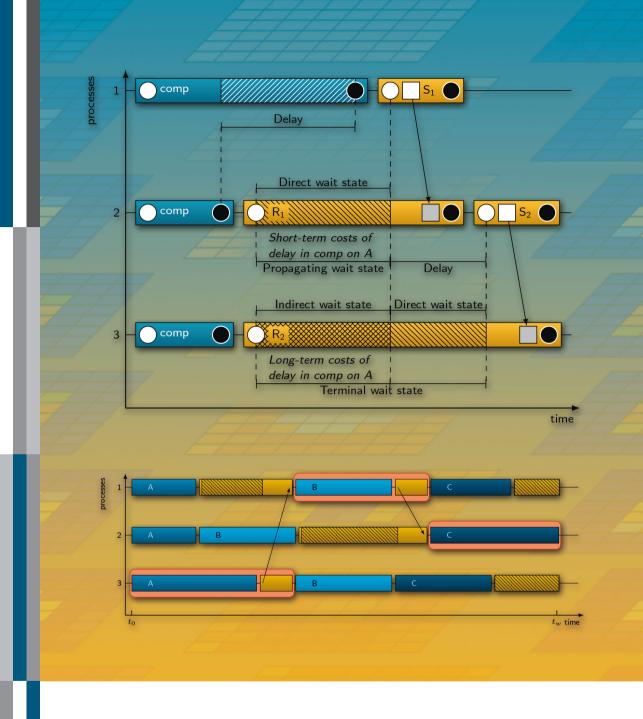

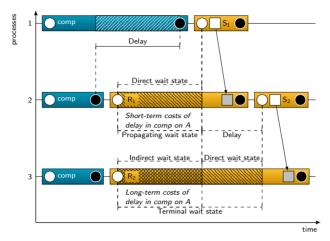

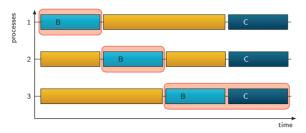

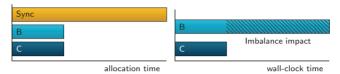

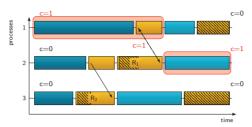

| 4.1  | Formation of wait states                                                   | 50 |

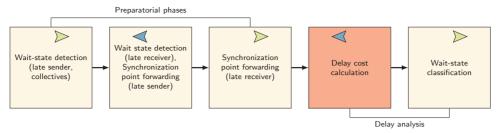

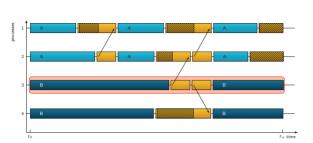

| 4.2  | Trace analysis replay passes performed for the delay analysis              | 60 |

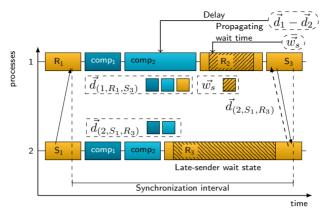

| 4.3  | Delay detection in backward replay                                         | 61 |

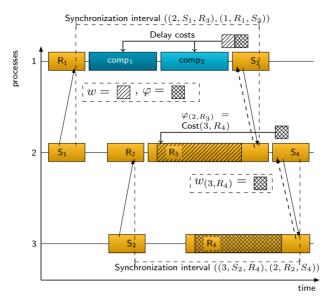

| 4.4  | Long-term delay cost propagation during the backward replay                | 62 |

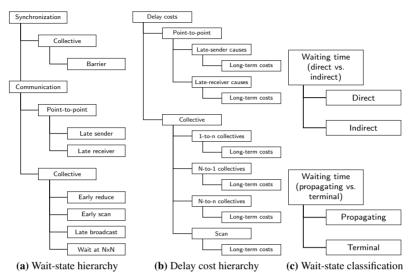

| 4.5  | Metric hierarchies of wait states and associated delay costs               | 64 |

| 4.6  | Visualization of delay costs in the Scalasca report browser                | 65 |

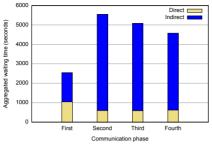

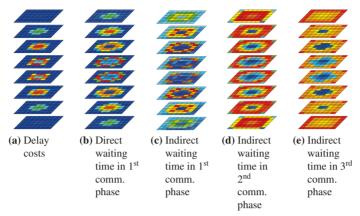

| 4.7  | Delay costs and direct vs. indirect wait time in Zeus-MP/2                 | 66 |

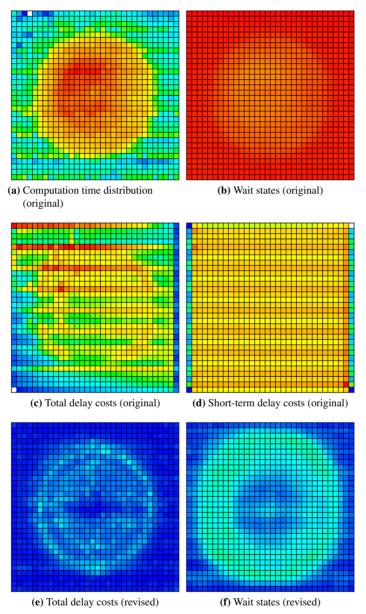

| 4.8  | Computation time, waiting time, and delay costs in Zeus-MP/2               | 66 |

| 4.9  | Propagation of wait states in Zeus-MP/2                                    | 67 |

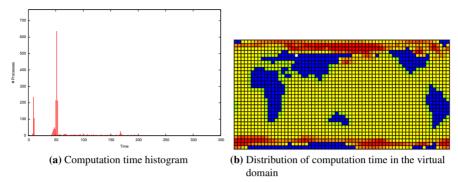

| 4.10 | Computation time distribution in the CESM sea ice model                    | 68 |

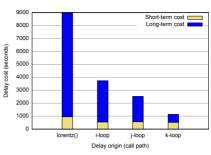

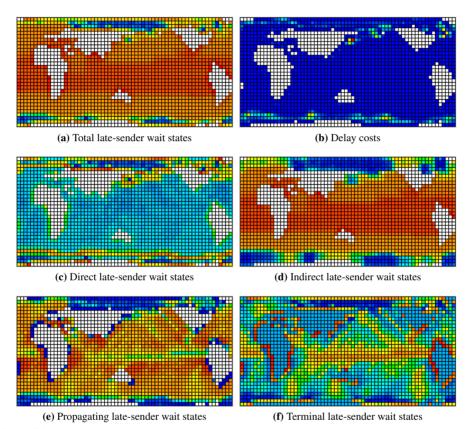

| 4.11 | Delay costs and late-sender wait states in CESM sea ice model              | 70 |

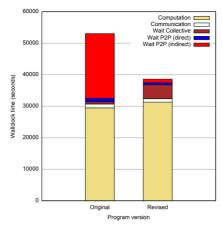

| 4.12 | Runtime of original vs. revised version of Illumination                    | 71 |

| 4.13 | Formation of wait states in the Illumination code                          | 75 |

| 5.1  | The critical path in an SPMD program run                                   | 80 |

| 5.2  | Analysis of dynamic performance effects                                    | 81 |

| 5.3  | Parallel profile and performance impact indicators for an MPMD program     | 82 |

| 5.4  | Critical-path detection in backward replay                                 | 85 |

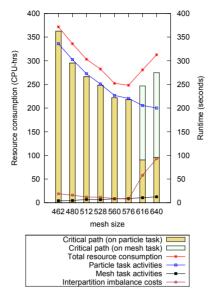

| 5.5  | Influence of mesh size and inverse screening length on ddcMD performance . | 88 |

### List of Figures

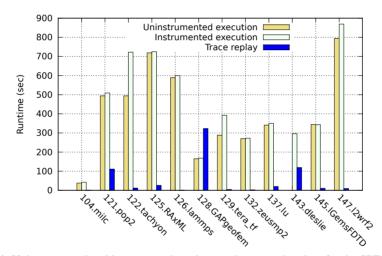

| 6.1 | Instrumentation overhead in SPECMPI applications | 96 |

|-----|--------------------------------------------------|----|

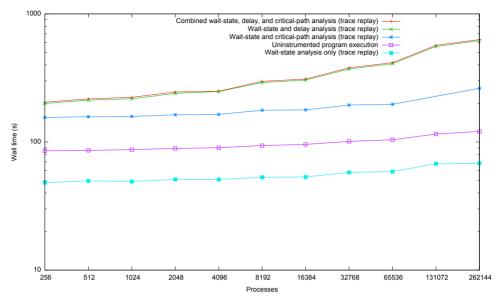

| 6.2 | Scalability of delay and critical-path analysis  | 99 |

## **List of Tables**

|     | Event types in the Scalasca event model                 |    |

|-----|---------------------------------------------------------|----|

|     | PEPC profile statistics for "tree_walk" and "sum_force" |    |

| 6.1 | Trace sizes of SPEC MPI2007 experiments                 | 96 |

## **Chapter 1**

## Introduction

Complementing observation and experimentation, simulation of physical phenomena has become the third pillar of scientific research. However, the never-ending urge to improve scope and accuracy of simulations through more detailed numerical models, higher resolutions, as well as multi-physics and multi-scale approaches leaves simulation scientists hungry for ever more computational power. Unsurprisingly, most of the world's largest supercomputers are dedicated to run advanced scientific simulation codes. Some time ago, simulation codes could benefit from continuously rising microprocessor clock speeds that would automatically improve execution speed with each new hardware generation, but with the shift towards multicore architectures, improvements of sequential processor speed have come to an end. Hence, as Herb Sutter puts it, "the free lunch is over" [77]: further program speedup now depends to a larger extent on the software's capability to leverage increasing amounts of parallelism. Software performance tuning is therefore more important than ever, and developers rely on powerful performance-analysis tools to identify bottlenecks in their codes. For software that runs on massively-parallel machines, characterizing parallel performance aspects is particularly important.

Providing the basic terms and definitions for the discussion of the two innovative performance analysis methods that form the major contribution of this dissertation, the following sections briefly outline the foundations of parallel computers, of parallel programming models, and of the performance analysis of parallel programs.

### 1.1 Parallel Computers

No matter how fast a processor is, a group of them working together can probably solve a given problem faster: this relatively obvious idea lead to the development of parallel computers early on. Supercomputers have been using parallel architectures for decades, but due to their complex architecture and difficult programming, the general public preferred sequential machines for everyday tasks. However, since the mid-2000s, when traditional means of increasing single-processor speed hit physical limitations, processor manufacturers adopted parallelism on a broad scale to further increase processor throughput. While parallel computing concepts that were originally applied in supercomputers now found their way into commodity machines, the general shift to parallelism also affects supercomputer architects and programmers: the introduction of parallelism on multiple levels and the rapid increase

of overall parallelism often require significant changes to existing programs. This section provides an overview of hardware architectures and programming models found in modern supercomputers.

#### 1.1.1 Hardware Architectures

As stated before, supercomputers today use parallel architectures. We can classify parallel architectures based on the memory architecture as either *shared-memory* or *distributed-memory* architectures. In a shared-memory machine, all processors access the same, global memory, whereas in a distributed-memory system, processors have local, private memory and cannot directly access the memory of remote processors.

A widespread class of shared-memory architectures are symmetric multi-processor (SMP) systems, where multiple processor sockets are placed on a single board and connected to the memory via a shared memory bus. Today, SMP parallelism is also found in multi-core systems, where multiple, typically similar processing units (cores) are placed on a single processor die. Other than traditional SMP systems, the cores in a multi-core processor usually share one or two levels of the processor's cache hierarchy. Contemporary high-end SMP system often have more than one processor socket with multi-core processors in each of them. Since a shared memory bus can become a performance bottleneck, modern systems with multiple processor sockets often connect each processor to its own local memory banks, and realize accesses to non-local memory banks through high-speed serial links. Examples are the AMD Opteron processors with HyperTransport [38] links, or the QuickPath interconnect [41] from Intel. Hardware cache coherency protocols such as MESI ensure cache coherency between the processors. Since memory access times differ depending on wether the requested location is stored in a local or remote memory bank, these architectures are referred to as ccNUMA (cache-coherent non-uniform memory architectures). While a shared-memory architecture allows highly efficient data exchange and synchronization between processors, the limited memory bandwidth still constitutes a bottleneck. Therefore, even ccNUMA systems quickly reach a scalability limit.

In contrast, a distributed-memory system is composed of multiple nodes that are connected through a network, where each node has its own local memory and at least one processor. Processors can only directly access memory on their local node, and have to communicate over the network to exchange data with remote nodes. The network transfer makes data exchange between nodes an order of magnitude slower than accesses to local memory. However, the aggregate memory bandwidth in distributed-memory machines increases with system size, and systems can in principle scale up arbitrarily. Because of their better scaling properties, large-scale supercomputers are typically distributed-memory systems. Common types of distributed-memory architectures are massively-parallel multiprocessor systems (MPP) and clusters. Although there is no sharp distinction between these two types, the term "MPP" generally refers to large-scale systems with propietary network interconnects, often using scalable network topologies such as a torus layout; while systems built mainly from commodity, off-the-shelf components are designated as clusters. Examples of MPP systems include the Blue Gene series from IBM and the Cray XT/XE/XK series; clusters are offered from many server

vendors and system integrators such as Dell, HP, or Bull. Clusters are typically built from standard server components, but they often use high-speed networks such as InfiniBand since efficient communication is an important performance factor.

Today, supercomputers virtually exclusively use multi-core CPUs on their nodes. To this end, today's large-scale systems are actually *hybrid* architectures with distributed-memory parallelism between nodes and shared-memory parallelism on the nodes. Another current trend are *heterogeneous* systems. Here, the standard CPUs on the compute nodes are accompanied by additional, throughput-oriented coprocessors (*accelerators*) that can execute vast amounts of (floating-point) operations in parallel and more efficiently than CPUs. A prominent example for a heterogeneous architecture was the Roadrunner supercomputer, which used the heterogeneous IBM Cell processor. Today, graphics hardware vendors such as NVidia succesfully promote the integration of GPUs (graphic-processing units) as accelerators into supercomputers: in the most recent Top 500 [1] list (June 2012), 52 systems use NVidia GPUs. Examples are the Chinese Tianhe-1A (rank 5), Jaguar at Oak Ridge National Laboratory (rank 6), and the Japanese Tsubame 2.0 (rank 14).

#### 1.1.2 Programming Models

Because of the vastly different characteristics of shared-memory and distributed-memory architectures, programmers need to choose a parallelization strategy that best fits their target platform. First and foremost, this means picking an appropriate programming model: typically, some form of multi-threading for shared-memory machines, and message-passing for distributed-memory machines. For hybrid systems, both approaches are also often used complementary in a single program.

#### **Message Passing**

The most popular programming model for tightly coupled parallel programs on distributed-memory machines is *message passing*, where processes synchronize and exchange data by sending messages over a message channel. In 1991, the message-passing interface standard (MPI) effort was initiated to create a generic, standardized, and portable message-passing API with language bindings for C, C++ and Fortran. When the first version of MPI was released in 1994, it rapidly gained attraction and is now the de-facto standard for message-passing programs. The latest version, MPI 2.2 [54], was released in September 2009. At its core, MPI provides functions for point-to-point or collective data exchange and synchronization between processes. In addition, MPI also includes interfaces for parallel file I/O and one-sided communication.

The MPI model defines a flat space of processes that each have their own memory address space, i.e., a process can not access another process' memory directly. To exchange information, the processes participating in a parallel program share a common communication context (communicator), where each process is assigned a unique rank number. Processes can address other processes in the communicator by their rank number and use it to send or receive messages from remote ranks or to participate in collective communication. Thanks to its flexible

and generic interface, virtually any parallelization scheme can be implemented efficiently with MPI.

Currently, MPI is the by far most popular choice for programming distributed-memory machines in the HPC area, receiving widespread support from industry, academia, and platform vendors. MPI is installed on virtually every supercomputer, and MPI programs run on any scale from a couple of dozen to hundreds of thousands of processes. A 2009 study from Balaji et al. [5] does identify some scalability bottlenecks in the MPI specification, but concludes that the core functionality will continue to scale to much higher levels. While parallel programs begin to adopt complementary parallel programming paradigms to exploit the increasing nodelevel parallelism, message passing with MPI remains the tool of choice for implementing data exchange between nodes on distributed-memory machines.

As a very generic programming model for parallel computers, message passing can also be used for programming shared-memory machines. The straightforward approach of running individual MPI processes on each processor core avoids many of the issues related to explicit shared-memory programming, but it has its limitations, too: in particular, multiple MPI processes need more memory than a single multi-threaded process. Also, multi-threading facilitates finer-grained parallelization schemes that can avoid explicit memory copies. As the number of cores per processor increases while the amount of available memory per core is expected to shrink, many codes adopt a hybrid parallelization approach with message-passing between computing nodes and shared-memory multi-threading within a node.

#### **Shared Memory**

With the recent rise of multi-core processors, either in stand-alone machines or in the nodes of larger, distributed-memory systems, shared-memory parallelism is now ubiquitous, spawning new interest in viable programming interfaces.

The shared-memory architecture facilitates multi-threading, where multiple threads of execution that access the same memory address space run in parallel. Global memory access from every thread eliminates the need to exchange data explicitly. This flexibility comes at a cost, however: uncoordinated accesses from multiple threads can easily corrupt shared data structures. Ensuring proper synchronization is therefore the foremost task when writing multi-threaded code. On top of that, today's complex NUMA architectures with multiple, partially shared cache levels hold some performance challenges for the ambitious programmer: meeting all data locality requirements to create optimally performing code across different systems can be difficult. As a result, shared-memory programming may look simple compared to message passing at first glance, but in reality, the effort required to create a correct and performant program can be significant.

There are a number of multi-threading programming interfaces available. Operating systems typically provide low-level APIs for creating threads and synchronizing memory access. For example, the POSIX threading interface (Pthreads) is a widely used, platform-independent low-level threading API. Some programming languages, such as Java or the upcoming C++11, also have multi-threading support built in. While low-level threading interfaces force programmers to take care of thread management and synchronization themselves, other shared-memory programming models provide high-level constructs to simplify the development of

multi-threaded codes. The tool of choice for HPC codes is typically OpenMP [8] (Open specification for Multi-Processing), a combination of an API, language directives, and environment variables for C, C++ and Fortran programs. By now, all major compilers support OpenMP. OpenMP provides a set of high-level parallelization and synchronization constructs, particularly means to semi-automatically parallelize computational loops. Recently, more advanced constructs such as lightweight tasks have been added. Because OpenMP is also straightforward to integrate into MPI programs, the combination of MPI and OpenMP has become a popular solution for developing hybrid applications.

#### Partitioned Global Address Space and One-Sided Communication

Beyond message passing, partitioned global address space (PGAS) and one-sided communication are the two other major programming models used in applications for distributed-memory systems. A partitioned global address space presents a virtual, global memory address space to all processes. Each process owns a single section of the global address space. A process can access both local and remote memory sections; an access to remote memory locations will automatically invoke the necessary network operations. The PGAS model is the basis for data-parallel programming languages such as Unified Parallel C (UPC) [86], Co-array Fortran [64], Chapel [15], and X10 [73].

Another alternative to exchanging data on distributed-memory machines is the remote memory access (RMA) or one-sided communication model. Unlike message passing, where all processes affected by a data transfer have to actively participate in the communication operation, a one-sided data transfer can be completely defined and controlled on only one side. The one-sided communication model is especcially useful on systems with hardware remote memory access support, such as InfiniBand network adapters. It is also used to implement PGAS languages. A popular framework for one-sided communication is ARMCI (Aggregate Remote Memory Copy Interface) [62]. The MPI-2 standard also provides a one-sided communication interface.

#### **Heterogeneous Systems**

The fundamental differences of throughput-oriented GPUs in comparison to classic CPUs also require dedicated programming models for heterogeneous systems. Currently, the preferred programming interface for the widespread graphics processors from NVidia that implement the Compute Unified Device Architecture (CUDA) [65] is NVidia's own propietary CUDA API and 'C for CUDA' programming language. An open alternative is OpenCL (Open Computing Language) [46], a hardware-independent open standard for programming hardware accelerators. With both CUDA and OpenCL, the kernels (i.e., code executed on the accelerator) need to be implemented as seperate components in a restricted, C99-based programming language.

As alternatives to the low-level CUDA and OpenCL interfaces, the (Open)HMPP [19] and OpenACC [67] initiatives provide higher-level approaches to programming accelerators. Both are based on programming language annotations, so that programmers do not need to switch programming languages to develop code for accelerators.

#### 1.1.3 Execution Models

Flynn [20] classifies parallel architectures by the number of concurrent instruction and data streams available in the architecture or program. In the context of parallel simulation codes, the SIMD (single instruction stream, multiple data streams) and MIMD (multiple instruction streams, multiple data streams) models are most relevant. Typically, both models are used in combination: the SIMD model represents the instruction-level parallelism provided by the vector-operation instruction sets in modern CPUs (such as Intel's SSE), where a single operation is applied to multiple data elements at once. Simultaneously, explicit parallelism in MIMD fashion using multi-threading or message passing is used to execute a program across multiple CPU cores and/or cluster nodes.

The MIMD category can be further classified into SPMD (single program, multiple data streams) and MPMD (multiple programs, multiple data streams) programs. With SPMD parallelism, each processor executes the same program (but with independent instruction pointers, as opposed to SIMD parallelism) operating on different data sets. Most simulation codes in the HPC environment are implemented as SPMD programs. In contrast, MPMD programs (loosely) combine sub-programs that perform entirely different activities. A common example is the master-worker model, which combines a "master" program (which distributes work) and "worker" programs (which execute the work). Another type of HPC programs that lends itself to MPMD-style parallelism are multi-physics codes which simulate a compound system by coupling different, interacting mathematical models and domains. Often, the individual models are themselves implemented as tightly-coupled SPMD programs and run in dedicated process partitions. Communication therefore occurs mostly within the process partitions, but to some extend also across partitions to reflect the interactions between different parts of the coupled system. An example for a coupled application that supports a flexible task decomposition in the way outlined here is the Community Earth System Model (CESM) climate project [85]. There, components that simulate different parts of the earth system, such as land surface, atmosphere, sea ice, or the ocean, can work in parallel in various SPMD and MPMD configurations. An additional, separate coupler component enables data transfers between individual components.

#### 1.1.4 Parallel Performance

Writing efficient software for massively parallel computers is a challenging task. Difficulties arise from a number of influence factors, including heterogeneous architectures, complex memory hierarchies, and in particular the ever-increasing amounts of parallelism on multiple levels that need to be exploited. In addition, software-related aspects such as the complexity of large simulation codes themselves, legacy code, or the need to combine multiple parallel programming models further complicate the performance challenge. In short, the combined complexity of hardware and software architectures in parallel computing environments makes it virtually impossible to ensure that a program will run at the desired speed on the target system without systematic performance analysis.

The performance of parallel programs in particular is characterized by both serial and parallel performance aspects. Primarily serial performance aspects include the efficient use of the

memory hierarchy and, obviously, the computational efficiency of the single-processor code. Important parallel performance aspects are communication and synchronization efficiency, process/thread mapping, and workload and communication balance.

Communication and synchronization efficiency refers in particular to the ratio of communication and (useful) computation in the program, i.e., the parallelization overhead. Also, an inefficient communication pattern can be a serious performance bottleneck. The second aspect mentioned, process/thread mapping, refers to the placement of (MPI) processes on the machine. In some cases, performance can be improved if processes are placed in such a way that the logical communication relationships between processes match the underlying physical links between the processors. Process mapping is something that is often tricky to accomplish optimally and difficult to observe.

Workload balance, the distribution of workload across processes, is obvoiusly a key factor for parallel performance: optimal speedup can only be achieved if the workload is equally distributed across processors. Likewise, developers need to balance the communication resource requirements – such as the number of communication partners – evenly between the processes. Properties, causes and analysis of load and communication imbalance as well as basic strategies for their remediation are discussed in detail in Chapter 3.

## 1.2 Performance Analysis

Combined, the parallel performance aspects are a major element of the overall program performance, and they alone determine the scalability of the code. A comprehensive performance evaluation of a parallel program must therefore consider not only serial, but also parallel performance aspects. Hence, serial performance analysis tools such as gprof are insufficient for the analysis of parallel programs. Dedicated tools for parallel programs include specific functionality for the analysis of parallel performance aspects.

### 1.2.1 Objectives and Requirements

The term *performance analysis*, as used in this thesis, refers less to the analysis of underlying algorithms or numerical methods, but rather to the performance evaluation of a program's implementation. Still, this interpretation does of course not exclude the possibility of reconsidering the choice of a particular algorithm as a consequence of the analysis. The major objectives of performance analysis are:

- Comparing expected with actual performance and scalability of the program

- Identifying performance and scalability bottlenecks

The first objective, comparing expected and actual performance, is necessary when porting applications to new platforms or integrating new algorithms or program features. This step can at least theoretically be partially automated if a formal *performance model* of the program exists. A performance model, such as the LogP [16] model for parallel machines, describes the performance behavior of a program as a function of its major input parameters and the

system characteristics. However, few application developers take the time to develop a formal performance model of their program; in most cases, they only have a vague or intuitive understanding of the code's performance. In general, performance modeling is best used in conjunction with performance measurement, and vice versa: the performance model is needed to identify and explain disparities between observed and expected program performance, while measurement data is needed to develop and validate the performance model.

Many parallel programs collect basic performance data themselves, such as the overall wall-clock time or time per iteration of the time-stepping loop. Although this basic information facilitates simple scalability studies and detection of overall performance improvements or degradations, it is typically insufficient for the second objective of performance analysis: identifying performance bottlenecks. Should the program not perform as desired, the performance analyst needs to pinpoint the root causes of the problem. Identifying specific bottlenecks requires detailed information about the program's performance on a low level, which only few programs provide themselves. Dedicated performance-analysis tools are then a crucial aid for application developers to help them with this task. In addition to commercial tools distributed by system vendors or software companies, a vibrant community of developers from academic institutions has created a range of high-quality, open-source performance-analysis tools for parallel applications. Often, the use of these tools leads to significant performance improvements in the target programs.

The requirements of performance tools are determined by the objectives of performance analysis mentioned above: they have to provide insightful data to allow an informed decision on whether the observed performance of a program matches the expectations, and, if necessary, support users in finding performance bottlenecks. To reach these goals, tools employ a variety of techniques, which we will explore in more detail in the following section.

### 1.2.2 Performance-Analysis Techniques

Tool developers have created a variety of complementary performance analysis techniques. To provide a consistent user experience, performance-analysis toolsets combine components to address three aspects of performance analysis:

- Measurement and data storage

- Data analysis

- Data presentation and visualization

This sections discusses these performance analysis techniques in general. Later, Section 1.2.3 provides an overview of the various tools on the market.

#### Measurement

The evaluation of program performance requires observation of the program at run time. Performance observation necessitates performance measurement. Measurement is therefore a key aspect of performance analysis, and performance tools distinguish themselves to some extend by what and how they measure.

Tools typically measure a variety of performance-relevant metrics. The most important metrics are certainly time-related ones; others include visit counts of code regions, the number of bytes transferred during communication operations, or the overall number of communications. In addition, modern processors provide a number of counter registers which store performance metrics collected by the CPU itself, for example, the number of instructions, memory accesses, or cache hits/misses. The PAPI library [40] provides an architecture-independent programming interface to these hardware-specific counters, which is employed by many tools to obtain hardware-counter metrics.

Regarding the way performance data is measured, most tools employ one of two basic methods: *sample-based* or *event-based* measurement. With sampling, measurements are taken at certain intervals (the sampling rate), typically triggered by timer interrupts, and associated with the code region of the target program that was visited at the time of the sample. As an advantage, measurement granularity and measurement overhead can easily be tuned by adjusting the sampling rate. Also, the code location of a sample can typically be identified very precisely, down to the level of a single line of code. However, since only snapshots of the execution are taken, there is always a certain degree of uncertainty associated with the measurement results. Especially count-based metrics, such as function visit counts, are imprecise; this is particularly true for functions that run for a significantly shorter time than the sampling interval. Therefore, sampling measurements should be taken over a longer period to collect enough samples for meaningful results.

Event-based measurements are triggered at certain events in the program, such as entering or leaving a code region. Thanks to the deterministic distribution of the measurement points, event-based measurements are complete and precise. On the downside, it is harder to tune the measurement granularity, and, therefore, the measurement overhead. Some performance-analysis techniques, for example, those that rely on a complete record of inter-process interactions, require event-based measurements.

#### **Profiling and Tracing**

Performance tools also employ different concepts for the aggregation and storage of performance data. Widely used are *profiling* and *tracing*. In a summary profile, all measurements pertaining to a single (process/source code) location are accumulated over time. The result then only contains aggregate values, for example, the total time spent in a certain code region, but not the precise intervals during which a region was visited. Therefore, profiles are often also called *summary profiles*. As a major advantage, the space required for a summary profile remains roughly constant, irrespective of the program runtime. Profiles of parallel programs usually store performance data for each process (and/or thread) individually.

With tracing, each measurement is stored individually. This technique generates increasing amounts of data over time, but allows a precise reconstruction of the program's dynamic behavior. In a profile, these performance dynamics are lost. There are approaches that combine advantages from both profiling and tracing; for example, Szebenyi et al. describe an on-line compression scheme for iterative applications that preserves performance dynamics in constant-size *time-series profiles* [78]. Still, the advanced analysis techniques presented

later in this thesis are only possible with trace data which captures the entire communication behavior in the section of interest. Chapter 2 discusses trace-analysis techniques in greater detail.

#### **Analysis**

The second important step performed by performance tools is data analysis, i.e., processing and filtering measurement data in a way that allows an easy overview of the performance behavior, or helps identifying interesting outliers or patterns. Some tools focus merely on presenting the measurement data to the user. These tools typically provide a variety of filters and statistical analysis methods, ranging from simple (e.g., minima, maxima, average) to quite advanced techniques such as cluster analysis. Often, the data-analysis functionality is integrated into the visualization component.

Another group of tools follows a highly analysis-oriented approach that aims to identify high-level performance patterns in the measured data automatically. These *automatic analysis* tools search for known inefficiency patterns in the measurement data, such as wait states in parallel communication or synchronization operations, or calculate high-level metrics such as the critical path. The analysis can take place while the program is running (*on-line*) or after it finished (*post-mortem*). On-line analysis does not require temporary storage for intermediate raw measurement data, but is limited in its capabilities to operations with little communication and computational effort in order to keep measurement dilation at bay.

Post-mortem analysis necessitates intermediate storage of raw measurement data (often traces), but can employ sophisticated, even multi-pass analysis strategies whose complexity is only limited by the user's patience. Instead of presenting measurement data in its entirety, an automatic analysis report pinpoints specific hotspots or bottlenecks a user may want to look into. The compact summary of interesting performance phenomena makes automatic analysis especially valuable for large-scale parallel program runs, where the sheer volume of data produced by a performance measurement presents a challenge for searching bottlenecks manually. Finding the root causes of performance problems (and fixing them) still requires expert knowledge and access to detailed performance data, but automatic analysis helps performance analysts by providing a good starting point for performance investigation. This task becomes even more important with increasing degrees of parallelism.

#### Presentation and Visualization

A good way to present the collected (and processed) performance data to the user is a key usability aspect of a performance tool. The challenges involved in finding helpful data presentation approaches are manifold. For example, measurements of complex programs at large scale can produce massive amounts of data that need to be made accessible. A good presentation tool should allow users to explore even large quantities of data interactively. Ideally, it also manages the balancing act between providing a compact overview of the program's behaviour as to not drown the user in a plethora of data, and at the same time allowing her to examine interesting findings in detail to investigate root causes of performance problems.

#### **Auto-tuning**

While performance analysis shows how far away a program's performance is from the optimal speed it can achieve on the target system, and helps identify specific bottlenecks, it does not make a program faster by itself. Instead, implementing optimizations based on performance-analysis results is where the actual difficulties often start. The potentially elaborate tuning process is still a mostly brain-powered task. However, it is also possible to follow an (often complementary) *auto-tuning* approach, which automatically chooses optimal algorithms or parameter settings for the target system. Dynamic performance tuning environments such as MATE [58] or Active Harmony [81] work fully on-line: they monitor and analyze the application as it runs, and can tune parameters and algorithms at runtime. Alternatively, autotuning can be used to automatically create optimized versions of performance-critical libraries by empirically determining optimal settings for performance-critical algorithm parameters, such as matric block size, in a profile-guided feedback process. This approach has been used in the context of the ATLAS [88] and OSKI [87] projects to create automatically tuned BLAS and sparse matrix kernels, respectively. Automatic tuning can greatly reduce the cost of porting libraries to new architectures.

#### 1.2.3 Performance Tools

A wide range of both open-source and commercial parallel performance-analysis tools exist. The TAU (Tuning and Analysis Utilities) performance suite [51] developed at the University of Oregon is a well-known and widely used profiling framework. It supports a wide range of parallel programming models, including MPI, OpenMP, CUDA, Pthreads, and Java Threads, and features a number of instrumentation techniques. TAU's ParaProf visualization component (Figure 1.1) offers a variety of 2D and 3D displays to browse profile data in detail. HPCToolkit [3] from Rice University focuses on collecting profiles using sample-based measurement. It also offers post-mortem analysis methods to highlight program regions with load imbalance. Other open-source profilers for parallel programs are Perfsuite [50] developed at NCSA, and Open|SpeedShop [82] developed by the Krell Institute. Like HPCToolkit, Open|SpeedShop can perform sampling for taking measurements of parallel programs.

Many hardware vendors provide performance-analysis tools for their platforms. Notably, Cray provides the CrayPat [18] tool to collect performance profiles and traces of parallel applications, and the Cray Apprentice2 graphical user interface to analyze profiles and traces recorded with CrayPat interactively. IBM provides the IBM High Performance Computing Toolkit (HPCT) for its pSeries, eSeries, and Blue Gene platforms, which can collect hardware performance counters as well as profiles and traces for MPI and OpenMP programs. With its High Performance Computing Systems Toolkit (HPCST) [39], IBM also offers an automatic analysis tool that can actively search and identify pre-defined bottleneck patterns from performance data, and suggest possible solutions. Intel also provides performance-analysis tools. The Intel VTune Amplifier [43] toolsuite is a performance-analysis tool for Fortran, C and C++ programs on Windows and Linux with a focus on multithreading. The Intel MPI Trace Analyzer [42] (ITAC) is a trace-analysis solution for programs using Intel MPI. It can record parallel event traces and display them in a timeline view.

In addition to the vendor-provided tools, a variety of platform-independent trace-analysis tools exist. Paraver [12] from the Barcelona Supercomputing Centre is an extensive tracing and visualization framework. It offers various trace visualizations, such as timeline and statistics displays, as well as combinable semantic and quantitative analysis functions, which can produce displays of high level information such as the global parallelism of the application or load balance in different loops. Vampir [48] from TU Dresden is a well-known, full-featured trace visualization tool, with a particular focus on event timeline displays. Figure 1.2 shows a selection of the performance displays Vampir has to offer. While Vampir's instrumentation and trace collection framework is available as open-source software, the visualization component is distributed under a commercial license. Finally, Scalasca [26] is a scalable, automatic trace-analysis toolset which performs post-mortem event-trace analysis to automatically identify bottlenecks in parallel applications. As the foundation for the work in this dissertation, Scalasca will be discussed in more detail in Section 2.2. In addition to the post-mortem analysis tools presented so far, open-source on-line analysis tools also exist. Notable examples are the Paradyn [55] tool from the University of Wisconsin, Madison, and Periscope [29] developed at TU München.

The ongoing trend to heterogeneous systems also raises the demand for performance-analysis tools that support heterogeneous programs. NVidia provides the comprehensive NVidia visual profiler [66] for CUDA and OpenCL programs. It supports both profiling and trace analysis, and can automatically point out typical performance bottlenecks related to heterogeneous architectures, such as inefficient memory copies between the accelerator device and the host processor. However, the NVidia profiler is limited to programs on a single shared-memory machine. Some vendor-independent tools such as TAU and Vampir recently added support for CUDA and OpenCL programs, and can also analyze combined CUDA/MPI applications. Tool support for the recent HMPP and OpenACC programming interfaces is at this point still limited.

### 1.3 Contribution of this Thesis

Load and communication (im)balance as a particular important aspect of parallel performance calls for appropriate tool support to help developers recognize and improve imbalance-related performance problems in their codes. However, imbalance can take a variety of shapes, and – as will be discussed in detail in Section 3.7 – recognizing all of them also poses a challenge to performance-analysis tools. Summarizing the findings outlined there, a reliable, generic performance-analysis solution should

- point out program locations where imbalance originates from;

- reveal the underlying imbalance pattern;

- determine the severity of imbalance in terms of its actual performance impact;

- take performance dynamics into account;

- be generically applicable, in particular to both SPMD and MPMD programs;

- work at large scale.

**Figure 1.1:** Performance profile displays in TAU ParaProf. The left picture shows a function profile, with the average time per process spent in each function. The right picture shows the time spent in each function (color-coded) on each process. This display can be used to detect (static) load imbalance.

**Figure 1.2:** Various event trace displays in Vampir. The top left area shows an event timeline, covering a small time interval on eight processes. The process timeline display below shows the activities performed on a single process within the selected interval (here, process 0). Grouped around the timelines are a call-path profile (bottom left), a message statistics profile (bottom center), a function group profile (top right), and a context view giving details on a selected item (in this case, an MPI\_Allreduce instance).

However, as an overview of previous work in Section 3.6 points out, currently available imbalance analysis solutions account for one or a subset of these aspects at best, but none of them fulfills all of the requirements listed here. Notably, profiling-based approaches cannot capture dynamic performance effects, while existing trace-based solutions drown users in vast amounts of data, do not scale to relevant system sizes, or do not appropriately adress complex load-balance issues arising in MPMD or hybrid programs. This dissertation introduces two novel methods to automatically detect and characterize imbalance in event traces: the *delay analysis* [10] to identify root causes of wait states, and the *critical-path analysis* [9] that characterizes load imbalance in terms of its performance impact. Together, these methods provide a universally applicable solution for the analysis of imbalance that fulfills all of the requirements listed above.

The delay-analysis approaches load imbalance from its visible effect, using wait states in synchronization points as a starting point to track down the imbalances that caused them in the first place. This approach optimally complements Scalasca's existing wait-state analysis. So far, Scalasca scans event traces to identify wait states in MPI operations or OpenMP constructs. These wait states indicate parallelization bottlenecks resulting from load imbalance or inefficient communication patterns: as such, wait states represent *symptoms* of inefficient parallelism. Moreover, wait states may themselves delay subsequent communication operations and spread further wait states through the system. This propagation effect can create a potentially large temporal and spatial distance between wait states and their original root causes, making it difficult to relate the effect (wait state) to its cause (imbalance) manually. The delay analysis closes this gap by automatically pinpointing the specific performance bottlenecks that cause wait states later on. To that end, the dissertation defines a terminology that describes the formation and propagation of wait states as a result of *delays*, a cost model that ranks delays according to their associated resource waste, and a scalable algorithm to detect and characterize delays.

The second major contribution of this dissertation, the critical-path analysis, illuminates the effect of load imbalance on program run time and resource consumption. The critical path determines those activities in a program that are responsible for the overall run time. While critical-path analysis has been used in performance-analysis tools to identify promising optimization targets for quite some time, the method introduced in this dissertation combines the critical-path with per-process profile data to uncover performance-relevant load-balance issues and determine their performance impact. The analysis creates a set of compact performance indicators that capture the overall load balance and any potential bottlenecks in an intuitive way. Compared to existing solutions that determine load imbalance on the basis of per-process profiles alone, the critical-path based approach has two major advantages: First, it accounts for dynamic effects, such as load shifting between processes over time, that other approaches miss. Second, in addition to the analysis of SPMD programs, it contains specific support for the analysis of complex load imbalance issues in MPMD programs.

Because parallel performance problems such as load imbalance are particularly significant at large scales, it is vitally important that analysis methods are applicable to large-scale program runs. Both the delay analysis and the critical-path analysis are implemented as extensions to the Scalasca performance-analysis toolset, which employs a highly scalable parallel event trace replay technique to analyze traces even from tens of thousands of processes. Scala-

bility studies with up to 262,144 cores confirm that both analysis methods are applicable to large-scale problems. Finally, a number of case studies with real-world examples demonstrate the ability of the delay and critical-path analysis to uncover imbalance-related performance bottlenecks intuitively.

## **Summary**

Since sequential processing speed is unlikely to increase significantly in current and future hardware, software must be designed to exploit parallelism to leverage maximal computing power. However, writing efficient parallel programs is challenging. One particularly important aspect of parallel performance is load and communication balance. The two new analysis techniques introduced in this thesis help developers in quickly identifying imbalance-related performance bottlenecks in large-scale parallel programs.

The dissertation is organized as follows. First, Chapter 2 briefly explains the underlying techniques used in performance-analysis tools. Next, Chapter 3 discusses load and communication balance in parallel programs in general, with a special focus on intricacies posed by certain imbalance patterns that complicate the identification of imbalance. Chapters 4 and 5 introduce the delay analysis and the critical-path analysis, respectively. Both chapters also include case studies which highlight the specific benefits of that technique. Afterwards, Chapter 6 discusses scalability and applicability of both techniques in comparison. Finally, Chapter 7 concludes the dissertation and provides an outlook on future research directions based on this work.

## **Chapter 2**

## **Event-Trace Analysis**

Many interesting phenomena in a program's behavior can only be investigated when the full sequence of its activities (up to a certain granularity) is known. Event tracing is a widely used technique to obtain this information for post-mortem analysis. This section introduces event tracing in general and its application in the Scalasca toolset for automatically identifying performance bottlenecks in particular. After a basic introduction of the Scalasca toolset, the chapter discusses basic principles of event tracing, with a particular focus on the Scalasca event model and references to related work where appropriate.

## 2.1 Event-Tracing Applications

An event trace represents the program execution as a sequence of events which reflect certain state changes in the program. The events are defined by an event model, which describes the different types of events and data attributes associated with them, as well as the context in which each event type occurs. At runtime, the target program performs measurements and stores event records containing the type, location, (typically) a timestamp, and attributes for all events that occur during execution.

Event tracing has a number of different applications in the context of parallel program analysis. In [49], Kranzlmüller describes the generation of event graphs from trace data to debug communication patterns in message-passing applications. Other projects, e.g. Dimemas [11, 31] or PSINS [83], use event traces to conduct simulations that predict performance and scalability of applications or system software on larger configurations or non-existant systems. Such simulation tools can also help in evaluating procurement decisions or future system designs. In [34], Hermanns et al. introduce a complementary trace-based simulation approach to study the impact of program optimizations. Of course, event tracing is also used for performance analysis. Trace visualizers like Vampir (Figure 1.2) present the recorded execution of a parallel code as a time-line diagram. Each program activity is represented by a rectangle whose length corresponds to its runtime, and message exchanges are shown as arrows between communication activities. Finally, automatic analysis tools like Scalasca perform an automatic bottleneck search on the trace to draw the user's attention directly to inefficiency patterns in the program. Automatic and visual analysis methods complement each very well and are often used in combination, for example to identify performance bottlenecks automatically first and examine them in detail in a time-line visualization tool later on. Open event specifications and trace file formats such as OTF-2, which can be parsed by different tools, facilitate such complementary analyses.

#### 2.2 Scalasca

Scalasca [26] is a profiling and trace analysis toolset for parallel programs which is jointly developed by the Jülich Supercomputing Centre and the German Research School for Simulation Sciences in Aachen. Its distinct feature is the automatic detection of wait states in communication and synchronization operations. Scalasca is specifically targeted to the analysis of parallel application behavior of large-scale programs; compared to its predecessor KOJAK [89], Scalasca is able to analyze massively parallel program runs with tens of thousands of processes. Developed with portability in mind, Scalasca runs on a broad range of current supercomputing platforms and architectures, including IBM Blue Gene L/P/Q series, the Cray XT/E/K series, NEC, and Linux clusters. It supports programs written in C, C++, or Fortran using MPI, basic OpenMP constructs, or both (hybrid programs). Support for further parallel programming models, such as partitioned shared address space languages or remote memory access models, is currently under development.

Scalasca supports two types of measurements. In *summary profile* mode, Scalasca records a runtime profile of the program. The profile report contains various metrics such as time, visit counts, bytes transferred in communication calls, and, optionally, hardware counter metrics for each call path and process and/or thread in the program. Time metrics are further split into the time spent in user code and the time spent in various types of MPI operations or OpenMP workshare, loop, and synchronization constructs. With its *tracing* mode, Scalasca records an event trace of the program, and runs an automatic post-mortem bottleneck search on the trace to identify and classify wait-states in MPI and OpenMP operations. The extended performance report produced by the trace analysis divides MPI time further into waiting and communication time and shows the process and program locations of wait states. Alternatively, the event traces produced by Scalasca can also be converted into various other trace formats or manually inspected with the Vampir trace visualizer.

Scalasca's performance reports store performance data in a three-dimensional (metric, callpath, thread) matrix. Essentially, every entry in this matrix represents the value of a particular metric at a particular program location (identified via its call path) on a particular thread. Even for trace analysis reports, values are always aggregated along the time dimension. Additionally, Scalasca provides a *worst instance tracking* feature, which reports the exact location in the trace where the worst instance of a performance bottleneck or metric has been observed.

Users can explore the reports using the provided graphical user interface (Figure 2.1), dubbed "Cube" in reference to the three dimensions in the report. It features three panes, one for each performance dimension. The left pane shows the hierarchy of metrics found in the report, which includes typical performance profile metrics such as execution time and visit counts as well as the waiting-time metrics produced by the automatic trace analysis. The middle pane shows the distribution of performance data across the program call tree, and the right pane shows the distribution of performance data across processes. For programs that use a regular

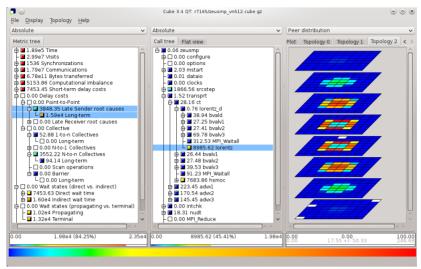

**Figure 2.1:** A trace-analysis report of the Zeus-MP/2 application with 512 MPI processes in the Scalasca report browser. The left pane shows the performance metrics produced by Scalasca. The middle pane shows the distribution of performance data across call paths for the selected "Late sender" waiting time metric. Finally, the third pane shows the distribution of the late-sender waiting time for the selected MPI\_Waitall call path across processes. In this case, the processes are arranged in the logical 8x8x8 grid used by the application.

1D, 2D or 3D virtual process topology, Scalasca can record and display the performance data within the application's virtual topology. Besides the HAC approach by Schulz et al. [75], Scalasca is one of very few production-grade tools which support such a visual mapping. As we will see in the example section in Chapter 4, this feature can greatly help in understanding complex performance phenomena.

#### 2.3 The Scalasca Event Model

Scalasca uses event traces as basis for its detailed automatic performance bottleneck search in parallel MPI, OpenMP, and hybrid MPI/OpenMP programs. Therefore, the underlying event model captures all the necessary information to identify performance problems and relate them to the program and machine locations where they occur. A special focus lies on capturing the MPI communication and OpenMP synchronization behavior: the event model has been designed to support Scalasca's automatic event-trace analysis of inefficient communication patterns, but it also facilitates other use cases beyond the automatic bottleneck search. Advanced examples include a performance simulation approach to evaluate performance hypotheses [34], and trace visualization using Vampir or other tools.

Scalasca's event model specifies programming-model independent events, such as events for entering and leaving source code regions, and events that are specific to a certain programming model, e.g. MPI or OpenMP. Every event contains a timestamp and additional information (attributes) related to the action it describes. Table 2.1 lists the event types and their attributes that are relevant for this dissertation.

The programming-model independent Enter (E) and Exit (X) events denote entering and leaving source code regions, respectively. The region entered is specified as an attribute of the Enter event, the region left in the Exit event is implied by assuming that region instances are properly nested. Most commonly, regions are functions or subroutines, but they can also mark basic building blocks such as a loop or a sequence of statements. The nesting of regions makes it possible to reproduce the *call path* of an event in the trace, that is, the sequence of regions entered leading to this event. The call-path information helps users to relate individual findings in the trace to their calling context (e.g., main/foo/send or main/bar/send). Knowledge of the call path is particularly useful to identify the calling contexts of MPI operations, which are often issued from different places in the program.

#### 2.3.1 MPI Events

Scalasca's event model contains a number of event types to capture MPI point-to-point and collective communication. Additionally, the model also includes events for MPI one-sided communication, but since one-sided communication is not covered by this thesis, they are not included in this discussion.

The MPI-related events provide a rich amount of information about the respective communication operation. For point-to-point communication, the collected attributes include the number of bytes that were transferred, the communicator for every communication operation, source or

**Table 2.1:** Event types in the Scalasca event model and their attributes. Each event additionally contains a timestamp.

| Symbol                            | Event type             | Attributes                            |  |  |  |  |  |

|-----------------------------------|------------------------|---------------------------------------|--|--|--|--|--|

| Entering and leaving code regions |                        |                                       |  |  |  |  |  |

| E                                 | Enter                  | Region entered                        |  |  |  |  |  |

|                                   |                        | Hardware counter values (optional)    |  |  |  |  |  |

| X                                 | Exit                   | Hardware counter values (optional)    |  |  |  |  |  |

| MPI communication                 |                        |                                       |  |  |  |  |  |

| $S_R$                             | Send request           | Destination location                  |  |  |  |  |  |

|                                   |                        | Message tag                           |  |  |  |  |  |

|                                   |                        | Bytes sent                            |  |  |  |  |  |

|                                   |                        | Communicator                          |  |  |  |  |  |

|                                   |                        | Request ID (for non-blocking send)    |  |  |  |  |  |

| $S_C$                             | Send completion        | Request ID                            |  |  |  |  |  |

| $R_R$                             | Receive request        | Request ID                            |  |  |  |  |  |

| $R_C$                             | Receive completion     | Source location                       |  |  |  |  |  |

|                                   |                        | Message tag                           |  |  |  |  |  |

|                                   |                        | Bytes received                        |  |  |  |  |  |

|                                   |                        | Communicator                          |  |  |  |  |  |

|                                   |                        | Request ID (for non-blocking receive) |  |  |  |  |  |

| $C_X$                             | Collective exit        | Collective root location              |  |  |  |  |  |

|                                   |                        | Bytes sent                            |  |  |  |  |  |

|                                   |                        | Bytes received                        |  |  |  |  |  |

|                                   |                        | Communicator                          |  |  |  |  |  |

| OpenMP events                     |                        |                                       |  |  |  |  |  |

| F                                 | Fork                   |                                       |  |  |  |  |  |