## **Strained Silicon and Silicon-Germanium Nanowire Tunnel FETs and Inverters**

Simon Richter

Forschungszentrum Jülich GmbH Peter Grünberg Institute (PGI) Semiconductor Nanoelectronics (PGI-9)

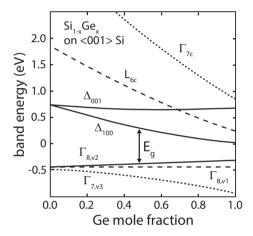

# Strained Silicon and Silicon-Germanium Nanowire Tunnel FETs and Inverters

Simon Richter

Schriften des Forschungszentrums Jülich Reihe Information / Information

Bibliographic information published by the Deutsche Nationalbibliothek. The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

Publisher and Forschungszentrum Jülich GmbH

Distributor: Zentralbibliothek

52425 lülich

Tel: +49 2461 61-5368 Fax: +49 2461 61-6103

Email: zb-publikation@fz-juelich.de www.fz-juelich.de/zb

Cover Design: Grafische Medien, Forschungszentrum Jülich GmbH

Printer: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2014

Schriften des Forschungszentrums Jülich Reihe Information / Information, Band / Volume 40

D 82 (Diss., RWTH Aachen University, 2014)

ISSN 1866-1777 ISBN 978-3-95806-002-9

The complete volume is freely available on the Internet on the Jülicher Open Access Server at www.fz-juelich.de/zb/openaccess

Neither this book nor any part of it may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage and retrieval system, without permission in writing from the publisher.

## **Abstract**

Reducing power consumption is an important issue for integrated circuits in portable devices relying on batteries and systems without external power supply. Scaling of the supply voltage  $V_{DD}$  in integrated circuits is a powerful tool for reducing the power consumption, due to the quadratic dependence on  $V_{DD}$ . MOSFETs, however, exhibit a fundamental limitation for the drain current increase per applied gate voltage difference. The tunnel field-effect transistor (TFET) provides the ability for beating this limitation, thus offering a performance advantage over MOSFETs for ultra-low  $V_{DD}$ .

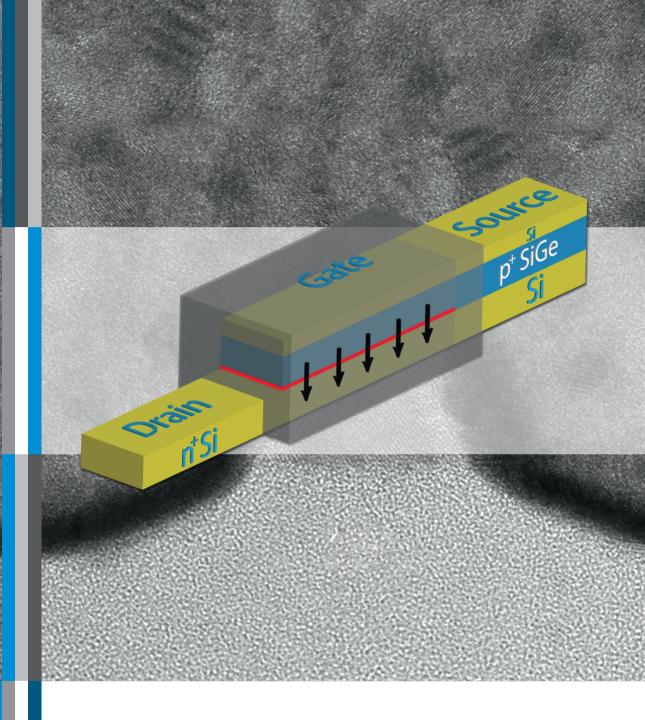

In this work, TFETs are fabricated with respect to design rules deduced from basic physical relations for the tunneling probability. The aim is to increase the tunneling probability in order to obtain higher drive currents in the devices. A tri-gated nanowire design in combination with a high- $\kappa$ /metal gate stacks is employed in order to increase the electrostatic gate control. Devices are fabricated on tensile-strained Si on insulator (SSOI) as well as compressively strained SiGe on SOI substrates. Fabricated devices reveal enhanced current for smaller band gap and effective carrier mass in those materials. In order to further increase  $I_{ON}$  and prevent  $I_{OFF}$  degradation occurring in small band gap TFET homostructures, a NW based heterostructure design with enlarged tunnel junction area is conceived and fabricated. Device characterization of this structure reveals superior performance and large  $I_{ON}/I_{OFF}$  ratio. TCAD simulations demonstrate how the structure could be adapted to utilize line tunneling in an inverted source region for further current improvement.

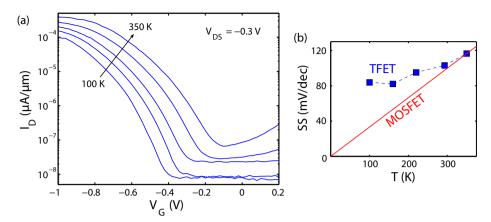

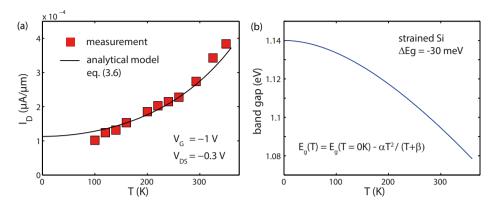

SSOI NW TFET characteristics are investigated and compared to MOSFETs fabricated with analog processing. Temperature dependence of TFET characteristics is analyzed and hot carrier effects in the tunnel junction are revealed by charge pumping measurements. Furthermore, the feasibility of TFETs for logic application is studied by fabrication of inverter structures. A comparison of TFET and MOSFET inverters reveals degradation of the voltage transfer characteristics caused by the ambipolarity of TFETs. An emulated TFET structure based on the fabricated SiGe/Si heterostructure with reduced ambipolarity proves to prevent output degradation of the TFET inverter and demonstrates sufficiently high noise margins down to ultra-low supply voltages.

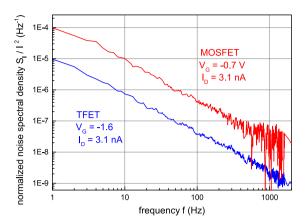

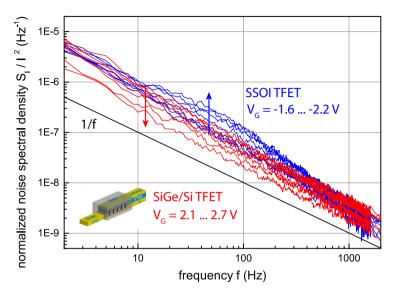

Low frequency noise measurements are performed on SSOI NW TFETs and MOSFETs revealing a dominant noise contribution by the tunnel junction in TFETs. The confined tunnel junction area provides a higher probability for RTS noise generation.

## Kurzfassung

Die Reduzierung des Energieverbrauchs ist ein wichtiges Thema für integrierte Schaltungen in mobilen Geräten und Systemen ohne externe Stromversorgung. Durch die quadratische Abhängigkeit der Leistungsaufnahme von  $V_{DD}$ , bietet die Skalierung der Versorgungsspannung eine effektive Möglichkeit zur Reduzierung des Energieverbrauchs. MOSFETs besitzen eine physikalische Begrenzung für die mögliche Erhöhung des Drainstroms bezogen auf eine angelegt Gatespannungsdifferenz, die wiederum ein Skalierung von  $V_{DD}$  begrenzt. Der Tunnel-Feldeffekttransistor (TFET) besitzt diese Begrenzung nicht und bietet daher Vorteile gegenüber dem MOSFET bei sehr kleinen Versorgungsspannungen.

In dieser Arbeit werden TFETs hergestellt und optimiert nach Designkonzepten basierend auf physikalischen Modellen für das Band-zu-Band-Tunneln. Ziel ist es, die Tunnelwahrscheinlichkeit zu erhöhen, um höhere Ströme in den Bauelementen zu ermöglichen. Die TFETs basieren auf Nanodrähten, die an drei Seiten von einem High- $\kappa$ /Metall-Gate umgeben sind. Diese Struktur erhöht die elektrostatische Gatekontrolle. Die Bauelemente werden auf verspanntem Silizium auf Isolator (SSOI) und Silizium-Germanium auf SOI Substraten prozessiert. Die Bauelemente zeigen eine Zunahme des Tunnelstroms mit abnehmender Bandlücke und effektiver Masse der Ladungsträger. Um den An-Strom weiter zu erhöhen und eine Vergrößerung des Aus-Stromes, wie sie bei Homostruktur TFETs mit kleiner Bandlücke auftritt, zu verhindern, wird ein Heterostruktur TFET basierend auf dem Nanodrahtdesign entwickelt und hergestellt. Dieser Heterostruktur TFET zeigt weiter verbesserte An-Ströme bei reduzierten Strömen im Aus-Zustand.

Die Eigenschaften der SSOI Nanodraht TFETs werden mit äquivalent prozessierten MOS-FETs verglichen. Die Temperaturabhängigkeit der TFETs wird charakterisiert und eine Verschlechterung des Gatedielektrikums durch hochenergetische Ladungsträger im Tunnelkontakt wird mittels der "Charge Pumping"-Methode nachgewiesen. Des Weiteren werden die Eigenschaften von TFETs in Bezug auf Logikschaltungen anhand von Invertern analysiert. Der Vergleich von TFET und MOSFET Invertern zeigt, dass sich die ambipolaren Eigenschaften der TFETs negativ auf die Spannungstransfercharakteristik des Inverters auswirken. Ein emulierter TFET Inverter basierend auf der hergestellten SiGe/Si Heterostruktur mit reduzierter Ambipolarität verhindert dies und zeigt gutes Schaltverhalten bei sehr kleinen Spannungen.

Die Charakterisierung des Niederfrequenzrauschens in TFET und MOSFET zeigt, dass der Tunnelkontakt im TFET das Rauschen dominiert. Der örtlich eingeschränkte Tunnelkontakt trägt zu einer höheren Wahrscheinlichkeit für das Auftreten von RTS-Rauschen bei.

## **Contents**

| 1 | Intr                                                      | ntroduction                                 |    |  |  |  |

|---|-----------------------------------------------------------|---------------------------------------------|----|--|--|--|

| 2 | The                                                       | oretical Background                         | 5  |  |  |  |

|   | 2.1                                                       | Power Consumption in Integrated Circuits    | 5  |  |  |  |

|   | 2.2                                                       | MOSFET                                      | 6  |  |  |  |

|   |                                                           | 2.2.1 Subthreshold Characteristics          | 6  |  |  |  |

|   | 2.3                                                       | Tunnel Field-Effect Transistor              | 7  |  |  |  |

|   |                                                           | 2.3.1 Band-to-Band Tunneling                | 8  |  |  |  |

|   |                                                           | 2.3.2 Subthreshold Characteristics          | 10 |  |  |  |

|   |                                                           | 2.3.3 Ambipolarity                          | 11 |  |  |  |

|   |                                                           | 2.3.4 Trap Assisted Tunneling               | 12 |  |  |  |

|   |                                                           | 2.3.5 Phonon-Absorption Assisted Tunneling  | 12 |  |  |  |

|   |                                                           |                                             | 13 |  |  |  |

|   |                                                           | 2.3.7 Drain Induced Barrier Thinning        | 14 |  |  |  |

|   | 2.4                                                       | TFET Design Considerations                  | 15 |  |  |  |

|   |                                                           | 2.4.1 Multi-Gate Structures                 | 15 |  |  |  |

|   |                                                           | 2.4.2 High- $\kappa$ Gate Dielectrics       | 17 |  |  |  |

|   |                                                           | 2.4.3 Density of Interface and Oxide States | 17 |  |  |  |

| 3 | Stra                                                      | ined SOI Nanowire TFET                      | 21 |  |  |  |

|   | 3.1                                                       | Device Fabrication                          | 21 |  |  |  |

|   | 3.2                                                       |                                             | 25 |  |  |  |

|   | 3.3 Current-Voltage Characteristics of NW TFET and MOSFET |                                             | 26 |  |  |  |

|   |                                                           |                                             | 31 |  |  |  |

|   |                                                           |                                             | 32 |  |  |  |

|   |                                                           |                                             | 34 |  |  |  |

|   |                                                           |                                             | 36 |  |  |  |

|   | 3.5                                                       |                                             | 38 |  |  |  |

|   | 3.6                                                       | r r                                         |    |  |  |  |

| 4 | SiGe | e Homostructure NW TFET                    | 43 |

|---|------|--------------------------------------------|----|

|   | 4.1  | Strained SiGe on SOI Substrate             | 43 |

|   | 4.2  | SiGe on SOI NW TFET Fabrication            | 44 |

|   | 4.3  | High- $\kappa$ /Metal Gate Stack on SiGe   | 46 |

|   | 4.4  | Density of Interface States                | 47 |

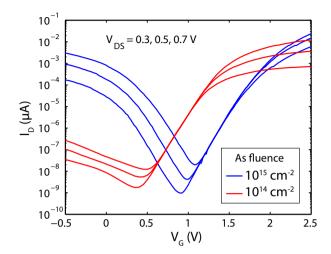

|   | 4.5  | I-V Characterization                       | 49 |

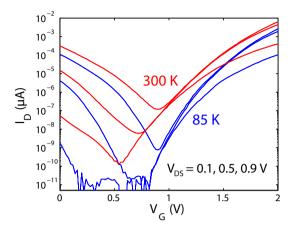

|   | 4.6  | Temperature Dependent Measurements         | 51 |

|   |      | 4.6.1 Trap Assisted Tunneling              | 51 |

|   |      | 4.6.2 Band Gap Extraction from SRH Current | 51 |

|   | 4.7  | Conclusion                                 | 54 |

| 5 | SiGe | e/Si Heterostructure NW TFET               | 55 |

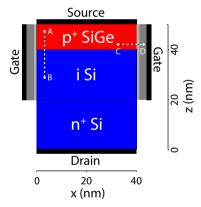

|   | 5.1  | Heterostructure TFET Concept               | 55 |

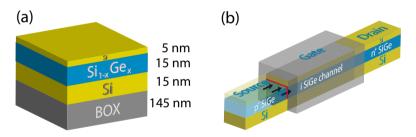

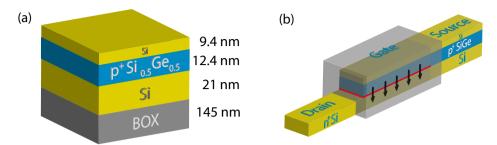

|   | 5.2  | Substrate and Device Structure             | 57 |

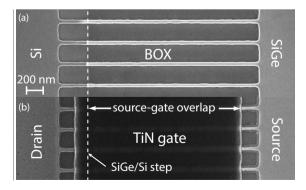

|   | 5.3  | Device Fabrication                         | 59 |

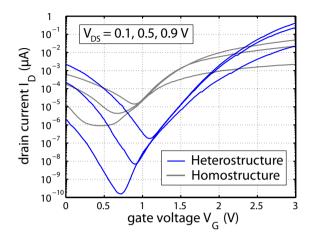

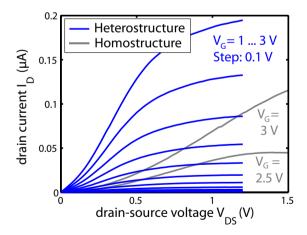

|   | 5.4  | Device Characterization                    | 60 |

|   |      | 5.4.1 Transfer and Output Characteristics  | 60 |

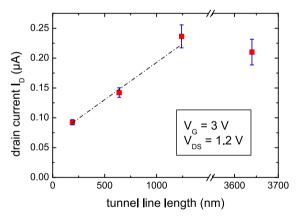

|   |      | 5.4.2 Increased Tunnel-Junction Area       | 62 |

|   |      | 5.4.3 Temperature Dependence               | 63 |

|   |      | 5.4.4 Reduction of Ambipolarity            | 64 |

|   | 5.5  | Device Simulation                          | 65 |

|   |      | 5.5.1 TCAD Sentaurus                       | 65 |

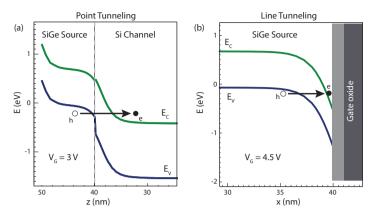

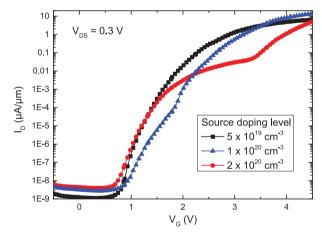

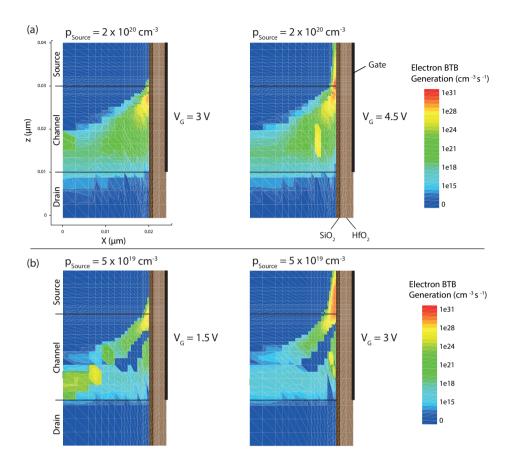

|   |      | 5.5.2 Point and Line Tunneling             | 65 |

|   | 5.6  | Conclusion                                 | 69 |

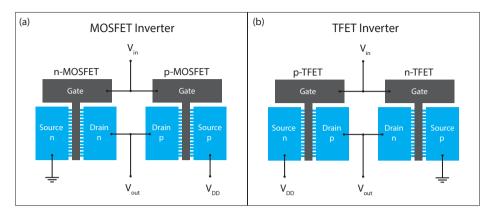

| 6 | Logi | ic Application                             | 71 |

|   | 6.1  | The Inverter                               | 71 |

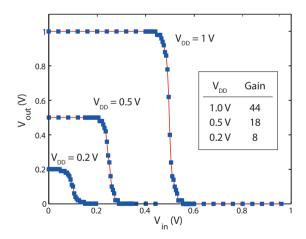

|   | 6.2  | Voltage Transfer Characteristics           | 74 |

|   |      | 6.2.1 MOSFET Inverter                      | 74 |

|   |      | 6.2.2 TFET Inverter                        | 76 |

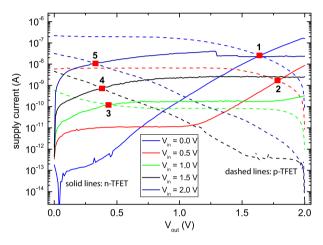

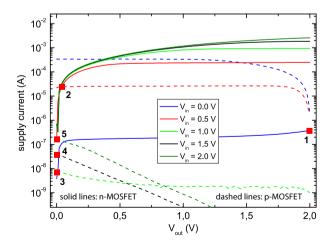

|   | 6.3  | Inverter Supply Current                    | 77 |

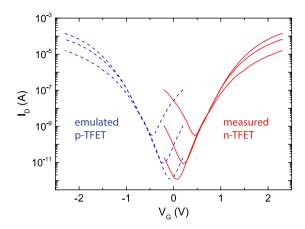

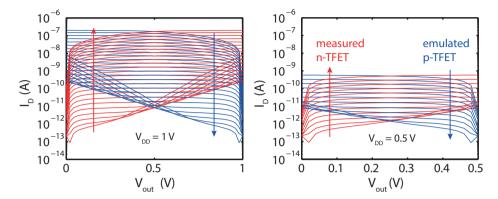

|   | 6.4  | Emulated Heterostructure TFET Inverter     | 79 |

|   | 6.5  | Conclusion                                 | 82 |

| 7 | Low  | Frequency Noise                            | 85 |

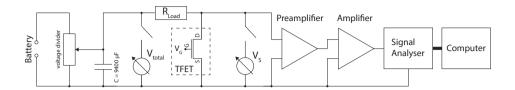

|   | 7.1  | Measurement Setup                          | 85 |

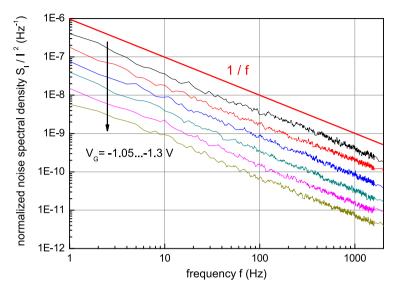

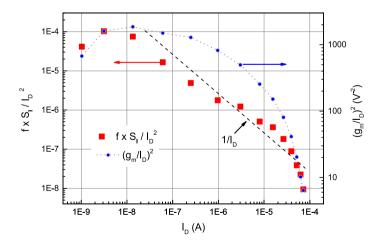

|   | 7.2  | LFN Measurements                           | 86 |

|   |      | 7.2.1 MOSFET                               | 87 |

|   |      | 7.2.2 TFET                                 | 89 |

| _   |            | Cont                 | ents           |

|-----|------------|----------------------|----------------|

|     | 7.3<br>7.4 |                      | 93<br>95<br>95 |

| 8   | ,          | nclusion and Outlook | 97             |

| Bi  | bliog      | raphy                | 100            |

| Lis | st of      | Publications         | 110            |

| Cı  | ırricu     | ılum Vitae           | 115            |

| A   | cknov      | wledgments           | 116            |

## 1 Introduction

In 2013, 4.5 billion people worldwide are in possession of a mobile subscription, which means that 63% of the world population uses mobile communication [110]. In the most recent quarter, the number of subscriptions increased by over 100 million. Nowadays, more than half of the sold mobile phones are smartphones, that have caused the mobile data traffic to increase by about 80% in the past year. Current predictions assume an increase of mobile data traffic by a factor of 10 until 2019. The evolution of smartphones and the need for increasing computational speed in the palm of our hand, however, causes a trade-off with battery life time, which is down to one or two days for a current smartphone under typical usage. Thus, power consumption of mobile devices becomes a growing issue.

Power consumption is also an issue for new electronic systems, such as sensors with application in industry, medicine and every day products, running without external power supply. For those devices, that rely for example on photo voltaic, thermoelectric generators or external radio frequencies (RFID) as power supply, low power consumption of the integrated circuits is essential.

Today, semiconductor based processors are utilized in almost every portable electronic device. These processors rely on metal-oxide-semiconductor field-effect transistors (MOSFETs) as switches for performing logic operations. MOSFETs allow for switching current by applying a voltage to a control gate. In contrast to an ideal switch, which should have zero current in the off-state and switch to the on-state instantaneously, a finite current flows in the off-state of a MOSFET and a certain voltage difference, the supply voltage  $V_{DD}$ , has to be applied to the gate to switch the device from the off- to the on-state. The gate voltage difference to increase the current in a transistor is described by the parameter S. The broadening of the Fermi distribution function sets a physical lower limit for S in a MOSFET. Thus, scaling  $V_{DD}$  is limited under consideration of sufficient current difference between on-state and off-state.

The current flowing through a transistor dissipates energy by heating the device. Even though the current and thus the dissipated heat in a single transistor are small, the dense packing of billions of transistors in modern CPUs causes a considerable energy dissipation, which discharges the battery in mobile devices. The power consumed in integrated circuits for switching transistors scales quadratic with the power supply  $(P \sim V_{DD}^2)$ , which makes scaling of  $V_{DD}$  a powerful tool for reducing power consumption.

In order to switch a transistors with smaller  $V_{DD}$  novel concepts relying on different charge transport mechanisms, that allow for values of S beating the MOSFET limitation, are needed. One example of such a new concept is the impact ionization transistor, which enables very steep values of S [31]. It has been shown though that this concept has essential drawbacks concerning switching speed since the finite time for the carrier multiplication process limits the minimum switching time of the device [93]. Another concept that was proposed as a steep switching device relies on a superlattice heterostructure to filter the Fermi distribution function and thus enables small values of S, which was proposed and investigated by simulations in [29]. However, device fabrication and integration of this structure proves to be rather challenging due to high requirements in terms of process variation.

One of the most promising concepts for a steep switching device is the tunnel field-effect transistor (TFET), that relies on quantum mechanical band-to-band tunneling (BTBT) as transport mechanism. The phenomenon of BTBT was already observed and described by Esaki in 1958 in narrow germanium p-n diodes [21] while the concept of a BTBT transistor device was first proposed an experimentally demonstrated in the late 1980s [5][99]. Since that time various TFET designs have been proposed and fabricated [91][41]. However, a BTBT transistor experimentally demonstrating subthreshold swings S smaller than the 60 mV/dec limitation of MOSFETs was realized first in 2004 [3]. Even though subthreshold swings below 60 mV/dec have been demonstrated up to now in TFETs with various concepts and materials, the average switching slopes are still well above 60 mV/dec and drive currents are typically below the limits of the international technology roadmap for semiconductors (ITRS), setting the aims for developments in future CMOS technology. Theoretical predictions, however, show that TFETs offer superior performance and consume less power at  $V_{DD}$  below 0.3 V, compared to MOSFETs [4].

Furthermore, the TFET concept offers the advantage of easy integration in current CMOS technology, since basically TFETs can be fabricated with a MOSFET process just by using opposite doping species in source and drain, in contrast to doping source and drain with the same doping type like in a MOSFET. However, the optimization of TFET structures follows different rules due to the deviating physical transport mechanism in the devices. Increasing the on-current in a TFET is especially important since the on-current defines the switching speed of the transistor. Due to the BTB tunneling probability, that is always smaller than one, on-current in a TFET is smaller compared to a MOSFET, where the probability of transmitting carriers from the source to the drain is equal to one in the on-state.

Within the framework of this thesis, different TFET structures based on silicon and silicongermanium nanowire structures are realized experimentally. The focus of the TFET device design is to increase the tunneling probability. Different fabricated TFET structures are analyzed in detail and concepts for optimization are deduced from measurement results as well as TCAD simulations. The content of this thesis is subdivided in eight chapters. Subsequent to this introductory chapter, chapter 2 presents the theoretical background and the underlying physical relations. which are used to develop the design and process for the TFETs and to interpret the measurement results. Chapter 3 exhibits experimental results on nanowire TFET and MOSFET structures fabricated on strained silicon on insulator substrates. The current-voltage characteristics of MOSFETs and TFETs are compared and various peculiarities of the TFET are explained. Chapter 4 presents results on nanowire TFETs fabricated on silicon-germanium substrates. The process implications of this material system are studied and performance improvement by different germanium concentrations is investigated. Chapter 5 introduces a heterostructure based TFET concept, that enhances BTBT by an enlarged tunnel junction area and in situ doping of the source. TCAD simulations are performed to further study the device characteristics and differences of the homo- and heterostructure TFET concept. Chapter 6 exhibits experimental results on inverters as simple logic elements build from TFETs presented in chapter 3. Furthermore, the implications of TFET device improvement on the inverter performance are demonstrated based on the heterostructure TFETs from chapter 6. Chapter 7 presents a comparative analysis of low frequency noise in MOSFETs and TFETs fabricated within the framework of this thesis. Chapter 8 concludes the findings and gives an outlook on possibilities for continuing the research on TFETs based on this work.

## 2 Theoretical Background

In this chapter the theoretical background and basic physical relations correlated with the later on presented experimental work are established. The metal-oxide-semiconductor field-effect transistor (MOSFET) and tunnel field-effect transistor (TFET) are introduced and their subthreshold characteristics are derived. Since this work focuses on TFETs, several additional effects influencing the TFET device performance are explained. The possibilities to increase the TFET performance by various design aspects are discussed subsequently. Finally a measurement technique for gate interface characterization is introduced, that is used to analyze the fabricated TFETs.

#### 2.1 Power Consumption in Integrated Circuits

The power which is dissipated by integrated circuits can be divided into two contributions. The first is the dynamic power consumption  $P_{dynamic}$ , which is correlated with the charging and discharging of load capacitances  $C_{load}$  when the transistors switch their state:

$$P_{dynamic} = C_{load} \cdot V_{DD}^2 \cdot f \,, \tag{2.1}$$

where f is the switching frequency.  $P_{dynamic}$  has a quadratic dependence on the supply voltage  $V_{DD}$  of the integrated circuit. The second contribution is the static power consumption of the transistors in the off-state:

$$P_{static} = I_{OFF} \cdot V_{DD} \,, \tag{2.2}$$

depending on  $V_{DD}$  and the leakage current of the transistor in the off-state  $I_{OFF}$ . An important figure of merit is the inverse subthreshold swing or subthreshold slope S that relates  $I_{OFF}$  to  $V_{DD}$  [41]:

$I_{OFF} \approx I_{ON} \cdot 10^{-\frac{V_{DD}}{S}} \,. \tag{2.3}$

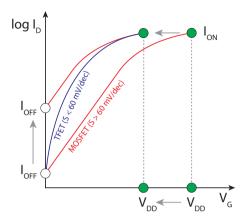

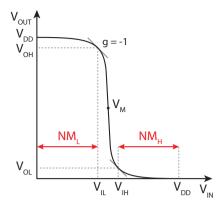

This equation shows that a decrease of  $V_{DD}$  at constant  $I_{ON}$  and S results in a rapid increase of  $I_{OFF}$ . This relation is illustrated in the schematic  $I_D$ - $V_G$  characteristics in Fig.2.1. Switching devices with a steeper average subthreshold swing are needed in order to maintain low off-state leakage for scaled down  $V_{DD}$  and thus reduced power consumption.

Figure 2.1: Schematic  $I_D$ - $V_G$  characteristics of a MOSFET limited to  $S > 60\,\mathrm{mV/dec}$  and a TFET with  $S < 60\,\mathrm{mV/dec}$ . Smaller average S is needed for supply voltage  $V_{DD}$  scaling without increasing  $I_{OFF}$ .

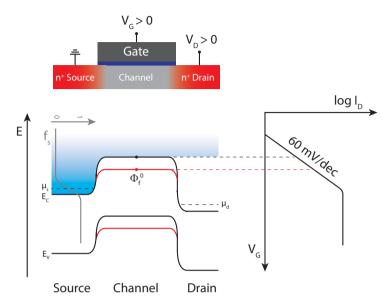

#### 2.2 MOSFET

A metal-oxide-semiconductor field-effect transistor (MOSFET) is a three terminal device based on a MOS capacitor. A schematic illustration of a n-channel MOSFET structure is shown in Fig.2.2. The gate electrode is electrically isolated from the semiconductor channel by a gate dielectric. In case of the n-channel MOSFET, the source and drain regions are  $n^+$ -doped. Fig.2.2 also shows the conduction and valence band edge energies in the semiconductor channel from source to drain. The principle of current switching in a MOSFET is the injection of carriers from a thermally broadened Fermi distribution function in the source over the potential barrier of the conduction band in the channel region. By applying a positive gate voltage  $V_G$  the bands in the channel region move down and electrons transport from source to drain is enabled. The increase of drain current  $I_D$  with applied  $V_G$  depends on the broadening of the Fermi distribution function.

#### 2.2.1 Subthreshold Characteristics

The Landauer formalism can be used as a simple 1D model to calculate the current flow in a MOSFET [15]:

$$I_D = \frac{2e}{h} \int_{-\infty}^{\infty} dE \, T(E) \left( f_s(E) - f_d(E) \right) = \frac{2e}{h} \int_{\Phi_x^0}^{\infty} dE \left( f_s(E) - f_d(E) \right) \,, \tag{2.4}$$

where e, h,  $f_s$  and  $f_d$  are, respectively the elementary charge, the Planck constant and the Fermi distribution functions in the source and drain.  $\Phi_f^0$  is the potential barrier height for

the electrons, which is given by the conduction band edge energy in the channel. T(E) denotes the transmission probability, which is T(E)=1 for  $E>\Phi_f^0$  and T(E)=0 else. In the subthreshold regime  $f_s$  and  $f_d$  can be approximated by the Boltzmann distribution, since  $\Phi_f^0$  is much larger than the chemical potentials  $\mu_s$  and  $\mu_d$  in source and drain, respectively. Since  $\mu_s>\mu_d$ , due to the applied  $V_{DS}$ ,  $f_d\ll f_s$  in this regime and  $f_d$  can be neglected. Based on these assumptions (2.4) becomes:

$$I_D = \frac{2e}{h} \int_{\Phi_f^0}^{\infty} dE \exp\left(-\frac{E - \mu_s}{k_B T}\right) = \frac{2e}{h} k_B T \exp\left(-\frac{\Phi_f^0 - \mu_s}{k_B T}\right). \tag{2.5}$$

$\Phi_f^0$  is a function of the gate voltage  $V_G$  [49]:

$$\partial \Phi_f^0 = e \left( \frac{C_{ox}}{C_{ox} + C_{devl} + C_{it}} \right) \partial V_G \tag{2.6}$$

where  $C_{depl}$ ,  $C_{it}$  and  $C_{ox}$  are the depletion, interface and gate oxide capacitance, respectively. The inverse subthreshold slope S can be calculated from the  $I_D$ - $V_G$  characteristics using (2.5) and (2.6):

$$S = \left[\frac{\partial \log I_D}{\partial V_G}\right]^{-1} = \ln(10) \left[\frac{\partial I_D}{\partial \Phi_f^0} \frac{\partial \Phi_f^0}{\partial V_G} \frac{1}{I_D}\right]^{-1} = \ln(10) \frac{k_B T}{e} \left(1 + \frac{C_{depl} + C_{it}}{C_{ox}}\right). \tag{2.7}$$

Hence S in a MOSFET has a lower limit depending on the broadening of the Fermi distribution function with temperature. At 300 K and in the case of  $C_{ox} \gg C_{depl} + C_{it}$  this lower limit is

$$S = \ln(10) \frac{k_B T}{e} \approx 60 \,\text{mV/dec}$$

(2.8)

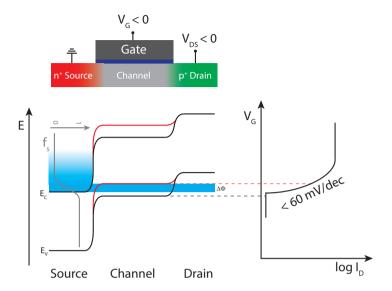

#### 2.3 Tunnel Field-Effect Transistor

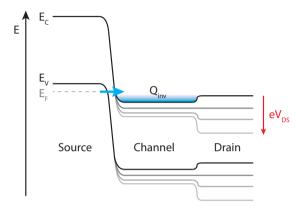

A tunnel-FET (TFET) is a gated p-i-n structure, which is operated in reverse bias. This means in contrast to the MOSFET source and drain are doped with opposite dopant species. A schematic of a TFET structure is shown in Fig.2.3. The transport mechanism in a TFET relies on band-to-band tunneling (BTBT) instead of thermal emission over a potential barrier as in a MOSFET. The band edge energies of valence and conduction band in a p-channel TFET structure are shown schematically in Fig.2.3. In p-channel configuration the source is n<sup>+</sup>-doped and a negative voltage  $V_{DS}$  is applied to the p-doped drain. By applying a negative voltage to the gate the bands in the channel region are moved up and an energy overlap  $\Delta\Phi$  of source conduction and channel valence band edge is created. The energy interval  $\Delta\Phi$  allows for BTBT from the source into the channel. Here the confined tunneling window acts like a band-pass filter for electrons from the source cutting off the high and

Figure 2.2: Schematic illustration of a n-channel MOSFET structure, the valence and conduction band edge energies along transport direction for two different gate voltages and the corresponding  $I_D$ - $V_G$  characteristics.

low energy tail of the Fermi distribution function. Thus, the carrier transport in the TFET becomes independent from the broadening of the Fermi function.

#### 2.3.1 Band-to-Band Tunneling

In quantum mechanics particles, such as electrons, can be represented by wave functions. In contrast to the classical picture these wave functions do not terminate on a finite potential barrier, but penetrate into it. Thus, there is a certain probability that an electron can tunnel through a potential barrier of finite width. In the Wentzel-Kramers-Brillouin (WKB) approximation a potential U(x), that does not change rapidly with x, is approximated with infinitesimal wide rectangular potentials. The WKB tunneling probability  $T_{WKB}$  is given by [98]

$$T_{WKB} = \exp\left(-2\int_{x_1}^{x_2} |k(x)| dx\right),$$

(2.9)

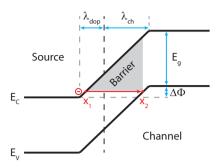

where k(x) is the wave vector of the carrier and  $x_{1,2}$  the starting and end point of the tunneling path, respectively. The tunneling barrier for a BTBT process can be approximated as a triangular barrier, which is illustrated in Fig.2.4. The wave vector for an electron with

Figure 2.3: Schematic illustration of a p-channel TFET structure, the valence and conduction band edge energies along transport direction for two different gate voltages and the corresponding  $I_D$ - $V_G$  characteristics.

the energy E in the conduction band can be written as:

$$k(x) = \sqrt{\frac{2m^*}{\hbar^2}(E - E_C)} = \sqrt{\frac{2m^*}{\hbar^2}(-e\mathcal{E}x)},$$

(2.10)

where the energy difference of the electron to the conduction band  $(E - E_C)$  was substituted in the second step by the corresponding electric field  $\mathcal{E}$  in the junction. Plugging (2.10) into (2.9) and using  $x_1 = 0$  and  $x_2 = E_g/e\mathcal{E}$  yields:

$$T_{WKB} = \exp\left(-\frac{4\sqrt{2m^*}E_g^{3/2}}{3\hbar e\mathcal{E}}\right). \tag{2.11}$$

The spatial width of the tunnel junction is determined by the sum of the screening length in the source  $\lambda_{dop}$  and the channel  $\lambda_{ch}$  [46][88].  $\lambda_{dop}$  is small for a steep doping profile in the source, whereas  $\lambda_{ch}$  decreases for high electrostatic channel control by the gate. The electric field in the junction can hence be expressed as  $e\mathcal{E} \approx (E_g + \Delta\Phi)/(\lambda_{dop} + \lambda_{ch})$  and (2.11) becomes:

$$T_{WKB} = \exp\left(-\frac{4(\lambda_{dop} + \lambda_{ch})\sqrt{2m^*}E_g^{3/2}}{3\hbar(\Delta\Phi + E_g)}\right). \tag{2.12}$$

This result shows that a large tunneling probability is observed for a small effective mass, small  $E_g$ , a steep source doping profile and a good electrostatic channel control.

Figure 2.4: Approximation of the BTBT barrier as a triangular potential.

#### 2.3.2 Subthreshold Characteristics

In order to calculate the subthreshold characteristics of a TFET the Landauer formalism from equation (2.4) can be used with T(E) given by  $T_{WKB}$  from equation (2.12). Carrier injection from the drain side can be neglected ( $f_d=0$ ) and the energy interval where tunneling occurs is given by the energy overlap  $\Delta\Phi=E_{CV}-E_{SC}$  of channel valence and source conduction band for the p-channel TFET. Assuming the band edge energies can be approximated as shown in Fig.2.4,  $T_{WKB}$  is independent of E for the energy interval  $\Delta\Phi$ . Hence,  $I_D$  can be expressed as:

$$I_D = T_{WKB} \cdot \frac{2e}{h} \int_0^{\Delta\Phi} dE \, f_s(E) = T_{WKB} \frac{2e}{h} F(\Delta\Phi) \,, \tag{2.13}$$

where  $F(\Delta\Phi)$  is the integral over the Fermi function. Assuming that the channel potential varies one to one with the applied gate potential  $\partial V_G/\partial\Delta\Phi = 1/e$ , the derivative of  $I_D$  becomes:

$$\frac{\partial I_D}{\partial V_G} = e \frac{\partial I_D}{\partial \Delta \Phi} = \frac{2e^2}{h} \left[ \frac{\partial T_{WKB}}{\partial \Delta \Phi} F(\Delta \Phi) + T_{WKB} \frac{\partial F(\Delta \Phi)}{\partial \Delta \Phi} \right] \,. \tag{2.14}$$

A high tunneling probability is necessary to achieve reasonable on-current and performance in a TFET. If a tunneling probability close to unity is achieved,  $T_{WKB}$  varies only slightly with  $\Delta\Phi$  and the first term in equation (2.14) can be neglected. Combining (2.13) and (2.14) S can be calculated by:

$$S = \left[\frac{\partial \log I_D}{\partial V_G}\right]^{-1} = \ln(10) \left[\frac{\partial I_D}{\partial V_G} \frac{1}{I_D}\right]^{-1} = \ln(10) \left[e\frac{\partial I_D}{\partial \Delta \Phi} \frac{1}{I_D}\right]^{-1}$$

$$= \ln(10) \left[\frac{2e^2}{h} T_{WKB} \frac{\partial F(\Delta \Phi)}{\partial \Delta \Phi} \frac{1}{T_{WKB} \frac{2e}{h} F(\Delta \Phi)}\right]^{-1}$$

$$= \frac{\ln(10)}{e} \frac{F(\Delta \Phi)}{\frac{\partial F(\Delta \Phi)}{\partial \Delta \Phi}}.$$

(2.15)

For small  $\Delta\Phi$  a Taylor expansion of the integral function  $F(\Delta\Phi)$  to the first order yields:

$$S = \frac{\ln(10)}{e} \Delta \Phi \,. \tag{2.16}$$

This relation reveals that S for a TFET has no first order temperature dependence, in contrast to the MOSFET. However, S in a TFET depends linearly on  $\Delta\Phi$  and thus S increases for increasing  $V_G$ , whereas S in a MOSFET is independent of  $V_G$ .

#### 2.3.3 Ambipolarity

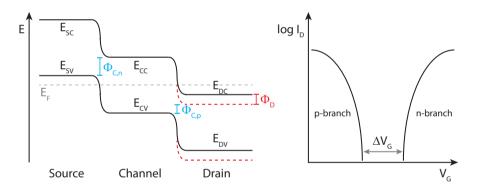

Due to the symmetric p-i-n structure of a TFET, BTBT can occur at the n-i as well as at the p-i junction when the bands in the channel region are shifted up and down, respectively. The applied gate voltage  $V_G$  causes a shift in the channel band energy edges by  $\Phi_C$ . Fig.2.5 shows an illustration of the valence and conduction band edges in a TFET. The drain voltage  $V_{DS}$  is applied to the n-doped region, which corresponds to a n-channel TFET configuration. In TFET operation the p-i-n diode is reverse biased and hence  $V_{DS}$  is positive in the n-channel configuration, shifting down the drain bands by the energy  $\Phi_D$ .

Figure 2.5: Illustration of the valence and conduction band edge energies in a p-i-n TFET structure (left) and the corresponding  $I_D$ - $V_G$  characteristics with symmetric p- and n-branch (right).

Fig.2.5 shows a schematic  $I_D$ - $V_G$  characteristics of a TFET. The on-set of the p- and n-branch are separated by a gate voltage difference  $\Delta V_G$ , that corresponds to a shift of the channel bands by  $\Phi_{C,n} + \Phi_{C,p}$ :

$$e\Delta V_G = \Phi_{C,n} + \Phi_{C,p} = E_{CC} - E_{SV} + E_{DC} - \Phi_D - E_{CV}$$

=  $E_q - \Phi_D - (E_{SV} - E_{DC})$ . (2.17)

$E_{CC}$ ,  $E_{CV}$ ,  $E_{SV}$  and  $E_{DC}$  are the band edge energies as given in Fig.2.5 and  $E_{CC} - E_{CV}$  can also be expressed as the band gap  $E_g$ .  $E_{SV} - E_{DC}$  is positive in case of degenerately

doped source and drain regions, when the Fermi energy  $E_F$  lies within the band. This demonstrates that the separation of p- and n-branch in the  $I_D$ - $V_G$  characteristics depends on  $E_g$  and decreases with applied  $V_{DS}$  and high source and drain doping level. Hence, for too small  $E_g$  or too high  $V_{DS}$  p- and n-branch can intersect and degrade the off-state. The separation of p- and n-branch given by equation (2.17), however, is the ideal case when

The separation of p- and n-branch given by equation (2.17), however, is the ideal case when BTBT is the only transport mechanism occurring in the TFET. The following sections introduce additional effects causing a further closing of the gap between p- and n-branch.

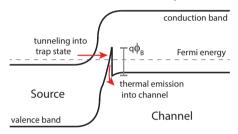

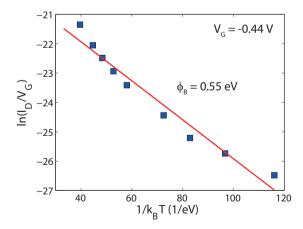

#### 2.3.4 Trap Assisted Tunneling

In addition to the BTBT process that sets in when the applied  $V_G$  is large enough to create an energy overlap of source and channel bands trap assisted tunneling (TAT) processes have to be taken into account in experimental TFET structures. TAT describes the process when carriers from the source tunnel into trap states within the channel band gap and reach the channel bands by thermal excitation from the trap states [73]. Trap states in the tunnel junction are introduced by oxide interface traps, defects due to ion implanted junctions or simply by the presence of dopant atoms. TAT sets in at smaller values of  $V_G$ , before an energy window for BTBT from source to channel band edges is opened. Hence the separation of pand n-branch, which was calculated before, is reduced.

Since the transfer of the carriers from the trap states into the channel relies on thermal excitation it depends on the broadening of the Fermi distribution function. Thus, current generated by TAT has the same limitation of S to  $60\,\mathrm{mV/dec}$  as a MOSFET. Due to the temperature dependence the thermal excitation and thus TAT can be suppressed at low temperatures.

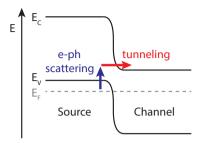

#### 2.3.5 Phonon-Absorption Assisted Tunneling

The scattering of electrons with phonons influences TFET performance. For BTBT in indirect semiconductors, such as silicon with a  $\Gamma$ - $\Delta$  band gap, phonon interaction with tunneling charge carriers is needed for momentum conservation. Due to electron-phonon scattering the energy of electrons in the source can be increased above the valence band edge as shown schematically in Fig.2.6. If the electron energy exceeds the conduction band energy in the channel BTBT is enabled, even though there is no energy overlap of source valence and channel conduction band. The maximum energy an electron can gain in Si is given by the transversal-optical phonon with 63 meV at corresponding wave vector [7]. Also transversal-acoustic phonons with 18.6 meV contribute to the phonon-absorption assisted tunneling [90].

Due to the onset of BTBT at smaller  $V_G$ , caused by electron-phonon scattering, S of the TFET is degraded and the n- and p-branch in the  $I_D$ - $V_G$  characteristics move closer together [55][53][63]. The phonon assisted tunneling also introduces a temperature dependence of S for small  $V_G$  since the phonon occupation is larger at higher T.

Figure 2.6: Illustration phonon assisted BTBT in a n-channel TFET.

#### 2.3.6 Shockley-Read-Hall Recombination

The Shockley-Read-Hall (SRH) recombination mechanism describes the recombination of conduction band electrons and valence band holes with the assistance of trap states within the band gap [87]. These trap states are for example introduced by dopant atoms. The recombination process is non-radiative and the electron energy is transferred to lattice vibrations. The SRH recombination is much more likely compared to direct recombination due to the smaller energy difference. The recombination rate  $R_{SRH}$  for a single-level trap is given by [20]:

$$R_{SRH} = \frac{np - n_i^2}{\tau_p \cdot (n + n_1) + \tau_n \cdot (p + p_1)},$$

(2.18)

with

$$n_1 = n_i \exp\left(\frac{E_T - E_F}{k_B T}\right), p_1 = n_i \exp\left(\frac{E_F - E_T}{k_B T}\right), \qquad (2.19)$$

where  $\tau_n$  and  $\tau_p$  are the carrier lifetimes of electrons and holes, respectively.  $E_T$  is the energy level of the trap state and  $E_F$  is the Fermi energy. The number of intrinsic carriers in a semiconductor is given by:

$$n_i = \sqrt{N_C N_V} \exp\left(-\frac{E_g}{2k_B T}\right) = AT^{\frac{3}{2}} \exp\left(-\frac{E_g}{2k_B T}\right), \tag{2.20}$$

where  $N_C$  and  $N_V$  are the densities of states in conduction and valence band, respectively. A is a constant depending on the density of states, effective masses of electrons and holes and the number of equivalent conduction bands [98]. Equation (2.20) shows that the intrinsic carrier concentration increases with decreasing band gap  $E_g$  [34].

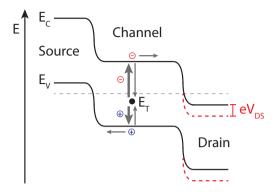

Although the channel region of a TFET is called intrinsic, the substrates used to fabricate the devices have a slight background dopant concentration in the order of  $10^{16} \,\mathrm{cm^{-3}}$  allowing for SRH generation-recombination in the channel region. This process is illustrated in Fig.2.7. The p-i-n diode in a TFET is reversed biased in standard operation, and electrons and holes flow from the channel region to the n-doped and p-doped region, respectively. n

Figure 2.7: Illustration of the SRH generation-recombination process at trap states within the band gap. Under reverse bias conditions holes flow to the p-doped source and electrons to the n-doped drain.

and p decrease in the channel region below the intrinsic carrier number  $n_i$  and  $R_{SRH}$  in equation (2.20) becomes negative. This means the SRH generation exceeds the recombination. The SRH generation contributes to the off-state current in a TFET and is largest under flat band voltage conditions. An accumulation of either electrons or holes in the channel by applied  $V_G$  above or below  $V_{FB}$  decreases the generation current.

#### 2.3.7 Drain Induced Barrier Thinning

In contrast to the MOSFET that shows a linear onset in  $I_D$ - $V_{DS}$  characteristics, most experimental demonstrated TFETs exhibit a superlinear onset [88] [83]. This characteristic is undesired since the current saturation is degraded. The reason for the superlinear behavior can be explained by Fig.2.8. When a gate voltage  $V_G$  large enough to enable BTBT is applied under zero  $V_{DS}$  electrons can tunnel into the channel and form an inversion charge  $Q_{inv}$  that screens the gate potential. Due to the screening of the gate potential the bands in the channel region can not be shifted further by larger applied  $V_G$ . By applying a positive  $V_{DS}$  the inversion charge and hence the screening of  $V_G$  in the channel is reduced. Thus, the bands in the channel move down and the tunnel distance at the source-channel junction decreases with increasing  $V_{DS}$ . This effect is called drain induced barrier thinning (DIBT). The DIBT can be avoided by going to the quantum capacitance limit, where the oxide capacitance  $C_{ox}$  is large compared to the quantum capacitance  $C_q$  [47]. In this case the channel potential changes one-to-one with the applied  $V_G$ . However, since  $C_q$  is proportional to the density of states (DOS) this limit can only be effectively reached in one-dimensional structures. For Si devices this limit is only reached for nanowire devices with diameters below 5 nm.

Also the source doping concentration influences the DIBT. A degenerately doped source provides a small  $\lambda_{dop}$ , reducing the tunneling distance and increasing the tunneling proba-

bility. Under these conditions the tunneling distance varies only slightly with a change of the channel band position and thus also DIBT is reduced [68][30]. However, there is a trade-off since for a highly degenerated source the Fermi function lies well within the band and the energetic window allowing for tunneling cuts out the Boltzmann part of the distribution function [49]. This limits S to  $60 \,\mathrm{mV/dec}$  as in the case of a MOSFET.

Figure 2.8: Schematic illustration of the drain induced barrier thinning (DIBT) at constant  $V_G$  and increasing  $V_{DS}$ .

#### 2.4 TFET Design Considerations

Based on the theoretical considerations about the working principle of TFETs presented in the previous sections, design concepts and rules for the fabrication of such devices can be deduced. The design concepts, which are utilized in the devices presented in this work are described in the following sections.

#### 2.4.1 Multi-Gate Structures

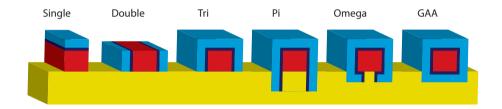

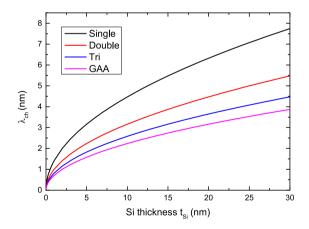

As previously discussed a good electrostatic gate control, which is represented by a small screening length  $\lambda_{ch}$ , is crucial in TFETs in order to achieve a high tunneling probability and thus high on-current.  $\lambda_{ch}$  can be calculated for a fully depleted SOI MOSFET with a single planar gate from Poisson's equation [13]:

$$\lambda_{ch} = \sqrt{\frac{\varepsilon_{si}}{\varepsilon_{ox}} t_{si} t_{ox}}, \qquad (2.21)$$

where  $\varepsilon_{si}$ ,  $\varepsilon_{ox}$ ,  $t_{si}$  and  $t_{ox}$  are, respectively, the dielectric constants and layer thicknesses of the silicon and gate oxide layer.  $\lambda_{ch}$  can further be reduced by going from a planar device concept to multi-gate configurations [22]. Different types of multi-gate structures with double-, tri-,  $\Omega$ -,  $\Pi$ - and gate-all-around (GAA) - configuration are depicted in Fig.2.9. Analytical calculations [13] and numerical simulations [59] reveal that  $\lambda_{ch}$  in double-, triand GAA-configuration for a square channel cross-section is given by (2.21) multiplied by a factor  $\sqrt{1/2}$ ,  $\sqrt{1/3}$  and  $\sqrt{1/4}$ , respectively.

Fig.2.10 exhibits calculated values of  $\lambda_{ch}$  for different gate configurations as a function of the Si thickness for a square cross-section and a gate dielectric of 3 nm HfO<sub>2</sub>. The GAA structure provides the best possible gate control. However, the processing complexity for these type of gates is much larger compared to a tri-gated structure, due the need for freestanding nanowires. In this work tri- and  $\Omega$ -gated nanowires are utilized for TFET application, since they provide a good compromise between process complexity and improved gate control. Fig.2.10 reveals that the improvement of  $\lambda_{ch}$  for a tri-gate compared to a planar single gate is quite large, while the additional improvement due to a GAA structure is rather small.

Figure 2.9: Schematic of various gate configuration types.

Figure 2.10: Calculated values of  $\lambda_{ch}$  for different gate configurations as a function of the Si thickness  $t_{Si}$ .

#### 2.4.2 High- $\kappa$ Gate Dielectrics

A large oxide capacitance  $C_{ox}$  is crucial in field-effect controlled devices to gain a good electrostatic control of the channel potential by the applied gate voltage, as shown in equation (2.6). Larger  $C_{ox}$  can be realized by decreasing the gate oxide thickness  $t_{ox}$  according to:

$$C_{ox} = \varepsilon_0 \varepsilon_{ox} \frac{A}{t_{ox}}, \qquad (2.22)$$

where A is the area of the capacitor,  $\varepsilon_0$  and  $\varepsilon_{ox}$  are the vacuum permittivity and the relative permittivity of the oxide, respectively. However, if  $t_{ox}$  is in the range of 1 nm the leakage current from the channel to the gate through the gate dielectric becomes too large to achieve acceptable device performance.

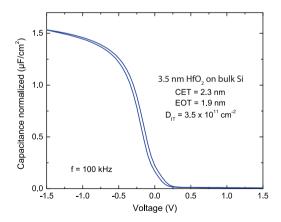

Originally, SiO<sub>2</sub> was used as a gate dielectric, since it has a large band gap, large band offsets to Si and can be fabricated simply by thermal oxidation of Si structures. One way of increasing  $C_{ox}$  further is utilizing dielectric materials that offer higher values of  $\varepsilon_{ox}$ , that is also sometimes denoted with  $\kappa$  in this context. These so called high- $\kappa$  dielectrics offer  $\varepsilon_{ox}$  values that can be many times higher than  $\varepsilon_{ox} = 3.9$  for SiO<sub>2</sub>. Hence,  $t_{ox}$  can be increased for high- $\kappa$  materials compared to SiO<sub>2</sub> and the leakage currents decrease. Especially rare earth based oxides like HfO<sub>2</sub> exhibit sufficiently high  $\varepsilon_{ox}$  and are well suited for CMOS integration [109][33]. HfO<sub>2</sub> was introduced in the 45 nm node in 2007 [70].

In this work Al<sub>2</sub>O<sub>3</sub> with  $\varepsilon_{ox} \approx 9$  and HfO<sub>2</sub> with  $\varepsilon_{ox} \approx 18$ , both grown by atomic layer deposition (ALD), are employed in order to increase  $C_{ox}$  and decrease  $\lambda_{ch}$  (see eq.(2.21)) in TFETs.

#### 2.4.3 Density of Interface and Oxide States

Charged interface states between semiconductor channel and gate dielectric can screen the gate electrical potential and deteriorate the control of the channel potential by the applied gate voltage. Charged interface trap states are for example introduced by surface contamination prior to the gate stack deposition or unsaturated chemical bonds of the semiconductor or high- $\kappa$  dielectric, which are always present in fabricated devices. Thus, characterization and improvement of the density of interface states  $D_{it}$  is important in the TFET optimization process.

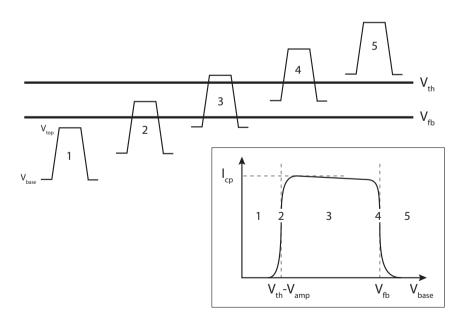

One possibility to investigate  $D_{it}$  is measuring the charge-pumping (CP) current  $I_{cp}$  [32]. CP measurements can be performed on bulk MOSFETs where source and drain are shortcut and  $I_{cp}$  is measured between source/drain and the bulk substrate. However, the CP technique can also be applied to gated p-i-n structures [19] which makes it applicable for TFETs.

The CP measurement setup for a TFET on SOI device is shown in Fig.2.11. The signal from a pulse generator is applied to the gate, while a small reverse bias is applied to the drain contact and the source is at ground potential. The charge pumping current  $I_{cp}$  is measured at the drain contact.

Figure 2.11: Schematic of the setup for charge pumping measurements on a TFET.

Figure 2.12: Schematic of the base-level charge pumping technique and the corresponding CP-current  $I_{cp}$  as a function of the base voltage  $V_{base}$ .

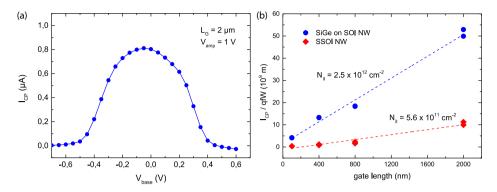

The working principle of the CP measurement is illustrated in Fig.2.12. Voltage pulses with constant amplitude  $V_{amp}$  and frequency f are applied to the gate contact.  $I_{cp}$  is measured at the drain while the base voltage  $V_{base}$  of the pulses is swept from  $V_{base} < V_{fb} - V_{amp}$  to  $V_{base} > V_{th}$ . The maximum  $I_{cp}$  is generated when for the applied voltage pulse  $V_{base}$  is below  $V_{fb}$  and  $V_{top}$  above  $V_{th}$ . In this case the channel is pumped from accumulation to inversion and the traps in the interface and oxide are filled in inversion with electrons. When the channel is pumped back into accumulation, within a time that is small compared to the trap lifetime, holes that are injected as majority carriers from the drain, recombine with the trapped electrons, thus causing a recombination current.

For very thin oxide layers a gate leakage current can add to  $I_{cp}$  and also a band-to-band tunnel current can occur due to the highly doped source and drain in a TFET. These current contributions can be determined by measuring  $I_{cp}$  at low frequency ( $f \approx 1 \, \mathrm{kHz}$ ), since they are not frequency dependent compared to the CP recombination current.

The measured  $I_{cp}$  is given by

$$I_{cp} = N_t A f e \,, \tag{2.23}$$

where A is the gate area and  $N_t$  the number of interface and oxide traps per area. In high- $\kappa$  gate stacks both, interface and oxide traps, contribute to  $I_{cp}$  [100]. The density of interface and oxide states  $D_t$  follows from normalizing  $N_t$  to the energy interval. A profile of the traps as a function of the distance from the interface can be measured by changing the discharge time, due to the spatial life time dependence of the traps.

## 3 Strained SOI Nanowire TFET

This chapter presents results on nanowire (NW) tunneling field effect transistors (TFETs) with high- $\kappa$ /metal gate fabricated on strained silicon on insulator (SSOI) substrate. As discussed in the theory section 2.3.1 the on-current in a TFET benefits especially from a small band gap  $E_g$  and a small screening length of the electrical potential  $\lambda$ . The design of the NW TFET presented here was conceived in order to improve exactly these two important device parameters. The biaxially tensile SSOI substrate offers reduced  $E_g$ , while the HfO<sub>2</sub>/TiN gate stack in combination with the NW array design guarantees good electrostatic gate control, and hence small  $\lambda$ . In the first part of this chapter the fabrication of NW array TFETs on SSOI is described. In the second part the resulting strain in the processed NWs is discussed. Part three compares the current-voltage (I-V) characteristics of the NW TFETs to reference NW MOSFETs highlighting fundamental differences between both device types. Part four analyzes the influence of the nanowire cross-section on the device performance. Part five presents a temperature dependent I-V analysis of the devices including comparisons to analytical models and device simulation.

#### 3.1 Device Fabrication

#### SSOI Substrate

Strained silicon (sSi) on insulator substrates with a sSi thickness of 15 nm were used to fabricate the NW array TFETs. The biaxial tensile strain in the sSi layer is  $\epsilon=0.8\,\%$  which correspondes to a stress of  $\sigma=1.3\,\mathrm{GPa}$  [27]. To fabricate the sSOI wafers a silicon layer is grown pseudomorphically on relaxed  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  with a Ge content of  $x=20\,\%$  [36][37]. Subsequently the sSi layer is transferred by wafer bonding technique onto a wafer with 145 nm thick  $\mathrm{SiO}_2$  on Si [9][27]. The sSi layer of the resulting SSOI wafer has a (001) surface and a background p-doping level of  $1\times10^{15}\,\mathrm{cm}^{-3}$ .

#### **Process Steps**

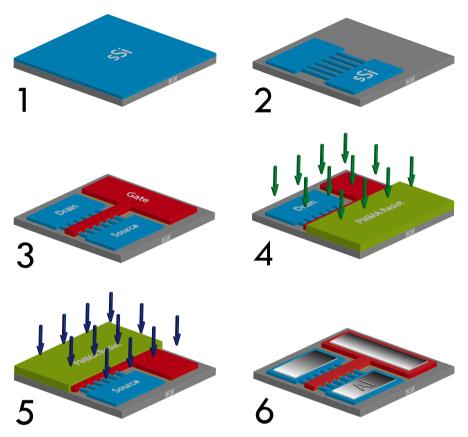

Fig.3.1 shows schematic images of the sample at important process steps during the fabrication. The process was carried out on  $19.5 \times 19.5 \,\mathrm{mm^2}$  pieces cut from a  $300 \,\mathrm{mm}$  wafer. Because of the nanowire array design very high resolution and alignment accuracy for the lithographic steps during the process are needed. Patterning of the NWs as well as the alignment of the gate and implantation windows require electron-beam lithography. In the

Figure 3.1: Schematic illustration of a TFET device at differnt steps during the processing.

following the process for the SSOI NW array p-TFET fabrication will be described in step by step:

- A precleaning of the sample pieces was performed to remove the resist protecting

the samples during sawing of the wafer into pieces. To remove the resist acetone and

propanol were used in combination with an ultrasonic bath. Subsequently the samples

were cleaned in Piranha etch with H<sub>2</sub>SO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub> (4:1).

- 2. Optical lithography using UV6.06 resist was used to transfer the electron-beam marker pattern with 15 × 15 μm² squares on the sample. Subsequently the markers were etched by reactive ion etching (RIE) in a three step process etching the top sSi layer with SF<sub>6</sub>/O<sub>2</sub>, the buried oxide with CHF<sub>3</sub> and the Si substrate with SF<sub>6</sub>/Ar plasma. The UV6.06 resist mask was removed using acetone and propanol. The resulting marker depth is about 700 nm.

- 3. The sample was coated with electron-beam sensitive PMMA resist 949.04/200K and the pattern for the nanowire array and mesa structure was written by electron-beam lithography. After development of the resist the pattern was transferred into the strained Si layer by RIE using a SF<sub>6</sub>/O<sub>2</sub> plasma at low temperature. The remaining PMMA resist was removed in an O<sub>2</sub> plasma process. The resulting NW array connecting two larger areas of sSi was shown schematically in Fig.3.1(2).

- 4. Subsequent to a standard RCA cleaning the gate stack was deposited. The high-κ dielectric HfO<sub>2</sub> is deposited by atomic layer deposition (ALD) and the gate metal TiN by atomic vapor deposition (AVD).

- 5. The sample was coated with negative electron-beam resist hydrogen silsesquioxane (HSQ XR-1541) and the **gate pattern** and gate pads were written by e-beam lithography. After development of the HSQ resist the TiN layer was patterned by RIE using SF<sub>6</sub>/Ar plasma. The HfO<sub>2</sub> was structured by wet chemical etching with HF acid. The resulting NW array with patterned gate stack was shown in Fig.3.1(3).

- 6. Two e-beam lithographies were needed as masks for the ion implantations. In both cases a 650 nm thick layer of PMMA 669.07/600K was used as **ion implantation** mask. First the source side of the TFET was covered and the implantation of BF<sub>2</sub><sup>+</sup> ions into the drain was performed. Only half of the gate was covered with resist in order to allow for a self aligned implantation process. In the second step the drain side of the TFET was covered and As<sup>+</sup> ions were implanted into the source region. This process is illustrated in Fig.3.1(4) and (5). Activation of the dopants was carried out by a rapid thermal spike annealing at 1000 °C in nitrogen atmosphere.

- 7. The sample was coated with negative tone photoresist nLOF2020 and contact windows at source, drain and gate were opened using optical lithography. After HF dipping to remove the native oxide, 150 nm Al was deposited for contact metalization by electron-beam evaporation. The redundant Al was removed by a lift-off process in acetone.

- 8. A forming gas annealing at 400 °C in 90%  $N_2$  and 10%  $H_2$  for 10 minutes was performed in order to improve the high- $\kappa$  interface quality as well as contact quality of the Al pads on the doped Si layer.

The processed p-TFETs can also be measured as n-TFET just by redefining source and drain contacts. Ion implantation energy and dose have been chosen carefully according to TRIM simulations, based on the amorphization limit in Si at a vacancy concentration of  $8.95 \times 10^{21} \, \mathrm{cm}^{-3}$  [69]. The implantation peak of the ion distribution was chosen to be close to the top of the sSi layer in order keep a thick enough crystalline seed layer to allow for solid phase epitaxial regrowth (SPER) during rapid thermal annealing (RTA) as shown in

[10]. Both dopant types were implanted to a fluence of  $1.5 \times 10^{15} \text{cm}^{-2}$ .

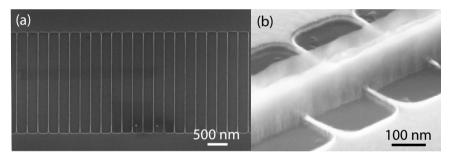

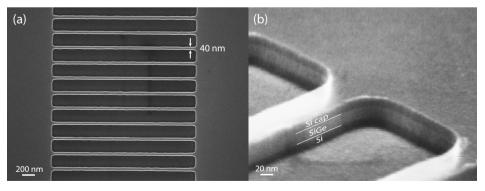

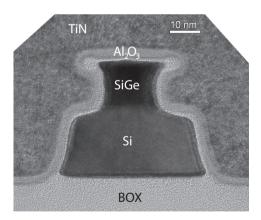

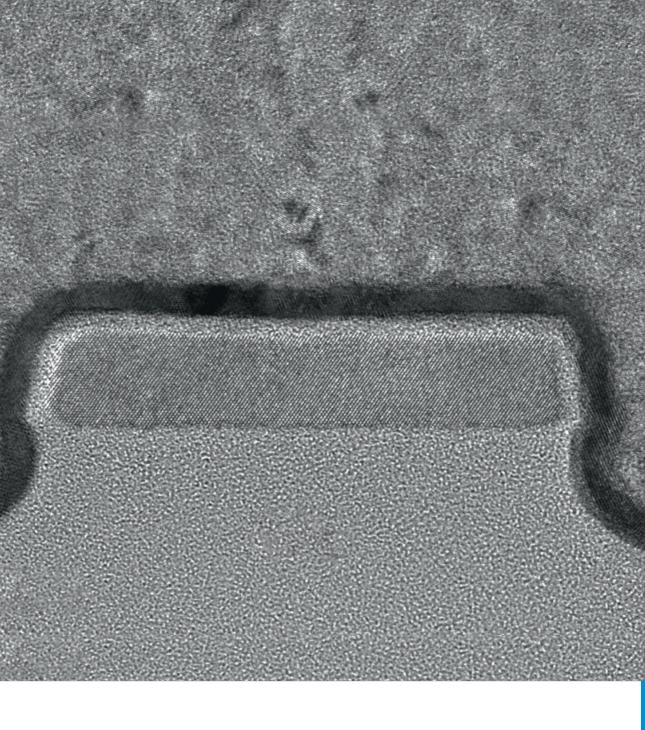

The NW array of each device consists of 1000 NWs in parallel with a pitch of 200 nm. Four different lengths of NWs with 500, 800, 1200 and 2400 nm and corresponding gate lengths of 100, 400, 800 and 2000 nm have been fabricated. Two batches of these TFETs with NW cross-sections of  $10 \times 50 \, \mathrm{nm^2}$  and  $10 \times 10 \, \mathrm{nm^2}$  have been processed, respectively. Fig.3.2 (a) shows a scanning electron microscope (SEM) image of a NW array with 10 nm wide and 2.5  $\mu$ m long NWs. A section of a NW array with 500 nm long wires and a 100 nm gate length TiN gate is shown in Fig.3.2 (b). Fig.3.3 (a) and (b) exhibit cross sectional transmission electron microscope (TEM) images of single NWs with 50 nm and 10 nm width, respectively, underneath the HfO<sub>2</sub>/TiN gate.

In the batch with the  $10\,\mathrm{nm}$  wide NWs, MOSFETs have been processed on the same chip together with the TFETs. For processing additional MOSFETs only the implantation mask in step 6 of the process description was changed. In case of the BF<sub>2</sub> implantation the whole n-MOSFET was covered by resist while boron was implanted in source and drain of the p-MOSFET and vice versa in case of the As implantation.

Figure 3.2: (a) Scanning electron microscope (SEM) image of a nanowire array with 2.4  $\mu$ m long and 10 nm wide NWs; (b) SEM image of 500 nm long NWs with a 100 nm long TiN gate.

Figure 3.3: Cross-sectional transmission electron microscope (TEM) images of single NWs with (a)  $10 \times 50 \text{ nm}^2$  and (b)  $10 \times 10 \text{ nm}^2$  in a SSOI NW array TFET with high- $\kappa/\text{metal}$  gate.

### 3.2 Uniaxial NW Strain

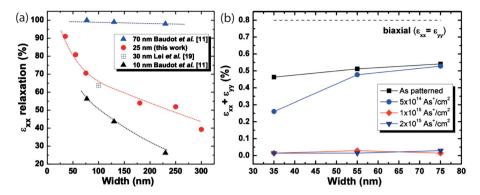

The 15 nm thick sSi layer of the (001) SSOI substrate has a biaxial tensile strain of  $\varepsilon=0.8\,\%$ . The channel of the fabricated NWs is oriented in [110] direction. Several publications show that due to the patterning of nanowires on biaxially tensile strained silicon the strain across the NW relaxes while the strain along the NW is maintained. This effect is demonstrated theoretically by 2D finite element simulations in [23] and experimentally by X-ray diffraction in [6]. Raman measurements performed on nanowires, fabricated by a process similar to the one used in this work, confirm that uniaxial strain along ion implanted nanowires recovers after spike annealing of the partially amorphized sSi layer [69].

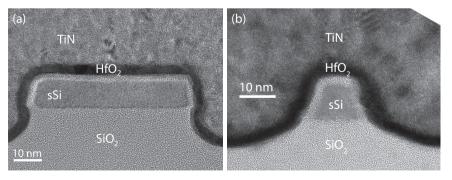

Figure 3.4: (a) Output and (b) transfer characteristics of strained Si NWs with HfO<sub>2</sub>/poly-Si gate stack fabricated by Sandow [83].

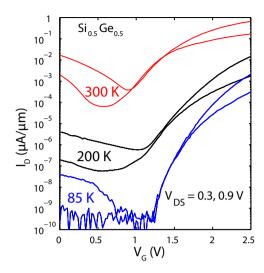

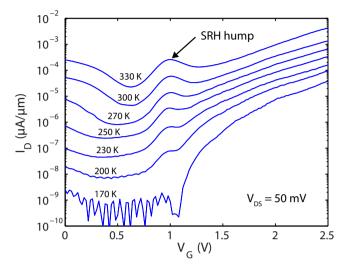

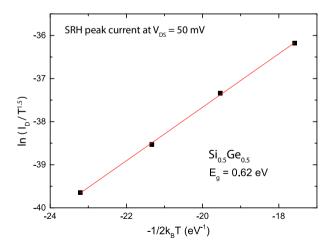

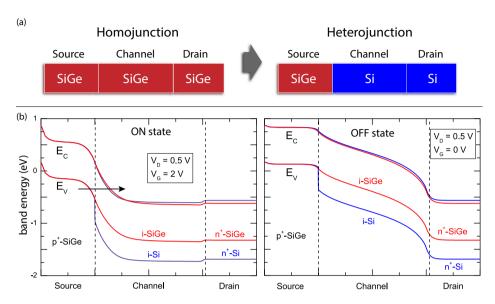

Nanowire array TFETs using SiO<sub>2</sub> as a gate dielectric and poly-Si as gate are demonstrated in [89]. Fig.3.4 exhibits output and transfer characteristics of these devices. The comparison of TFETs fabricated on SOI and sSOI substrate reveals an increase in on-current by a factor of six for the strained Si. The transfer characteristics in Fig.3.4 also show a slight increase in the off-current ( $I_{OFF}$ ) of the TFET with sSi NWs. From this change in  $I_{OFF}$  the actual reduction of  $E_g$  for strained Si NWs compared to unstrained NWs was estimated.  $I_{OFF}$  in a TFET is dominated by a Shockley-Read-Hall (SRH) generation-recombination current in the reverse-biased p-i-n diode causing the small hump in between the two branches of the transfer characteristics. The SRH current is proportional to the intrinsic carrier concentration  $n_i = \exp(-E_g/2k_BT)$ , where  $k_B$  is the Boltzmann constant and T the temperature. The band gap difference  $\Delta E_g$  between Si and sSi can be extracted from the  $I_{OFF}$  values of both devices by:

$$\frac{I_{OFF(sSi)}}{I_{OFF(Si)}} = \exp\left(\frac{\Delta E_g}{2k_BT}\right). \tag{3.1}$$

With  $I_{OFF}$  values shown in Fig.3.4 at  $V_{DS} = -0.05 \,\text{V}$  the strain induced decrease of  $E_g$  was calculated to approximately  $\Delta E_g = 30 \,\text{meV}$ .

Figure 3.5: (a) Relaxation of strain across sSi Nanowires patterned from biaxial tensile strained Si layers as a function of NW width. (b) Strain in patterned NWs after implantation with different As fluence and spike annealing as a function of NW width measured by Raman spectroscopy. [69]

Deformation potential theory calculations in [62] provide values for the reduction of band gap energy in Si for strain  $\varepsilon$  of  $\Delta E_g = -17.01\,\mathrm{eV} \times \varepsilon$  for biaxial and  $\Delta E_g = -6.19\,\mathrm{eV} \times \varepsilon$  for uniaxial [110] tensile strain, respectively. In [69] NWs of different widths are patterned on SSOI substrate with a sSi thickness of 25 nm. Fig.3.5(a) shows the strain relaxation across a sSi NW in dependence of the NW width for different layer thicknesses. Fig.3.5(b) exhibits the sum of the lateral strain components measured by Raman spectroscopy for as-patterned NWs and NWs with different As<sup>+</sup> implantation fluence after spike annealing. According to these results one can assume that the strain across the sSi NWs with a cross-section of  $20\times20\,\mathrm{nm}^2$  in [89] is almost completely relaxed. This implies that the remaining strain in the NW is uniaxial in the [110] direction and  $\varepsilon$  can be estimated from Fig.3.5(b) to approximately 0.5%. Based on these results the band gap reduction due to the uniaxial strain in the NW of [89] becomes  $\Delta E_g = -17.01\times0.5\% = -31\,\mathrm{meV}$ . This value is in good agreement with  $\Delta E_g$  deduced from measured  $I_{OFF}$  values in Fig.3.4(b). In order to increase the performance of SSOI NW TFETs further in this work a high- $\kappa$ /metal gate stack is introduced in the fabrication process, enhancing electrostatic gate control.

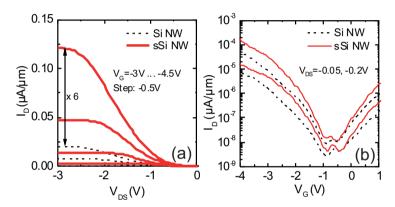

# 3.3 Current-Voltage Characteristics of NW TFET and MOSFET

TFETs are a promising candidate for replacing MOSFETs especially in low power application. However, the possibility for steep switching slopes and small off-currents are only some of the points where TFETs differ from MOSFETs. Also other differences in the current-voltage (I-V) characteristics of TFETs and MOSFETs can have crucial implications on the behavior of integrated circuits for digital logic or analog applications. Thus, the I-V characteristics of a TFET need to be studied in depth to enable suitable circuit design. Deviations

in the *I-V* characteristics from a MOSFET may result in challenges but also in opportunities for new applications. In this section *I-V* characteristics of NW array TFETs and MOSFETs are presented and compared. The MOSFET and TFET devices are fabricated with the same process described in section 3.1 on the same chip. The only difference of MOSFET and TFET is the doping of source and drain regions. Whereas source and drain of the TFET are doped with the opposite doping type, in the MOSFET, both are doped with either As or B to form a n-MOSFET and p-MOSFET, respectively.

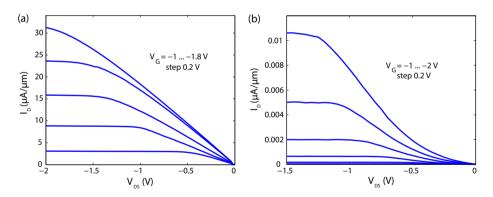

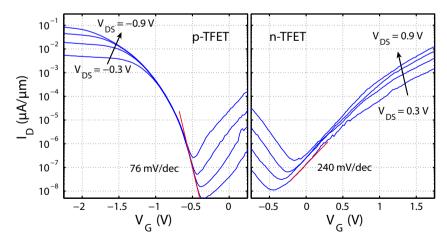

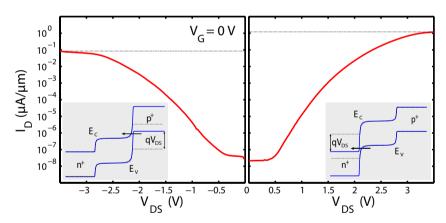

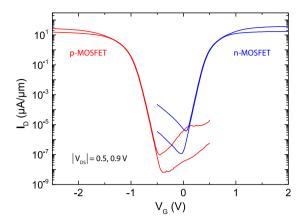

The I-V characteristics of the SSOI NW TFETs and MOSFETs were measured using a Keithley SCS4200 semiconductor analyzer. Due to the symmetric design of the devices the TFET can be operated in n-channel as well as in p-channel mode. In the p-channel configuration the n-doped region acts as the source, whereas in the n-channel TFET the p-doped region becomes the source. The p-i-n junction in the TFET is reverse biased. For this reason the applied drain voltage  $V_{DS}$  is negative in case of the p-channel device and positive in case of the n-channel device. The source is in both cases put to ground potential. The applied gate voltage  $V_G$ , which opens the energy window for BTBT at the source-channel junction is negative in case of the p-channel and positive in case of the n-channel TFET.  $V_G$  is measured with respect to the grounded source contact. For the MOSFET applied  $V_{DS}$  and  $V_G$  are positive for the n-channel and negative for the p-channel device.

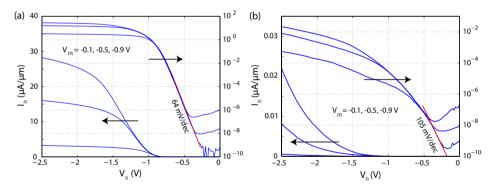

Figure 3.6:  $I_D$ - $V_G$  characteristics of SSOI NW array (a) MOSFET and (b) TFET with  $10 \times 10 \text{ nm}^2$  NW cross-section and 400 nm gate length in linear and logarithmic scale of the  $I_D$ .

In the following, I-V characteristics of NW array MOSFETs and TFETs with  $10 \times 10 \,\mathrm{nm}^2$  NW cross-section and 400 nm gate length are compared. The drain current  $I_D$  is normalized to the circumference of the NW which is covered by the gate. The comparison is limited to p-channel TFET and MOSFET devices, since the performance of p-channel Si TFETs exceeds that of n-channel devices due to better tunnel junction quality at the As doped junction, which will be further discussed in section 3.4.2. The drain current  $I_D$  is measured for both devices in dependence of  $V_G$  at various fixed values for  $V_{DS}$  and in dependence of

Figure 3.7: Inverse subthreshold slope S in dependence of  $I_D$  for SSOI NW array MOSFET and TFET with  $400\,\mathrm{nm}$  gate length.

$V_{DS}$  at different values for  $V_G$ . The former is also referred to as transfer characteristics while the latter is called output characteristics.

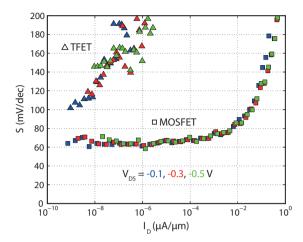

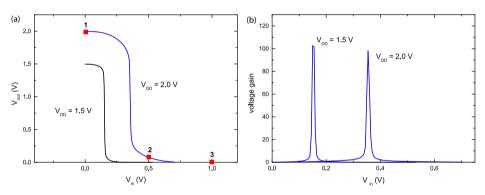

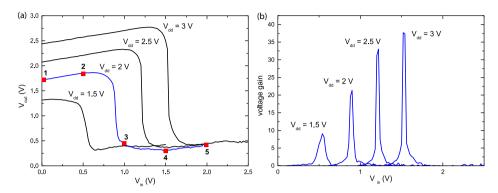

Fig.3.6 exhibits a comparison of transfer characteristics of p-MOSFET and p-TFET, both shown in logarithmic and linear y-axis scale. The characteristics of MOSFET and TFET reveal fundamental differences. The NW p-MOSFET switches over more than seven orders of magnitude of  $I_D$  with almost constant slope. This is shown more clearly in the graph of the inverse subthreshold slope S in dependence of  $I_D$  in Fig.3.7. S is close to the ideal 60 mV/dec with an average of 64 mV/dec between  $I_D = 10^{-9} \,\mu\text{A}/\mu\text{m}$  and  $I_D = 10^{-5} \,\mu\text{A}/\mu\text{m}$ . The shift of the transfer curves with increasing  $V_{DS}$  is very small proving a negligible drain induced barrier lowering (DIBL) effect. The close to ideal S and small DIBL indicates excellent gate control. The logarithmic TFET transfer characteristics in Fig.3.6 (b) exhibits a rather round shape compared to the MOSFET characteristics. S increases with  $I_D$  as shown in Fig.3.7 in contrast to the MOSFET, where S is constant over several orders of magnitude. The minimum slope in the TFET is  $105 \, \text{mV/dec}$ . This behavior of transfer characteristics is conform with the theoretical expectation. The inverse subthreshold slope of a MOSFET is given by [49] (p.347):

$$S = \left(\frac{\partial \log(I_D)}{\partial V_G}\right)^{-1} = \frac{k_B T}{q} \ln 10 \left(1 + \frac{C_d + C_{it}}{C_{ox}}\right),\tag{3.2}$$

where  $C_{ox}$  is the oxide capacitance,  $C_d$  the depletion capacitance and  $C_{it}$  the interface capacitance. Hence, S is independent of  $V_G$  and constant in the subthreshold region. The ideal value for  $S = (k_B T/q) \ln 10 \approx 60 \,\text{mV/dec}$  at 300 K can only be reached, if  $C_{ox}$  is much larger than  $C_d + C_{it}$ . Small  $C_d$  requires a low channel doping and  $C_{it}$  depends on the interface

state density between channel and gate dielectric. The observed close to ideal value for S proves that this condition for the capacitances is fulfilled.

For a TFET the subthreshold slope is calculated as [48]:

$$S \approx \frac{\ln(10)}{e} \Delta \Phi \,, \tag{3.3}$$

if the tunneling probability  $T_{WKB}$  is close to unity, which means that the change of  $T_{WKB}$  with  $V_G$  is small. The dependence on the energetic overlap of source conduction and channel valence band  $\Delta\Phi$ , causes S to increase with the applied  $V_G$ , since the overlap  $\Delta\Phi$  increases with rising gate potential. This dependence of S on  $V_G$  has crucial implications on TFET performance, since the average subthreshold slope over the whole current range from  $I_{OFF}$  to  $I_{ON}$  needs to be below  $60\,\mathrm{mV/dec}$  to actually reduce the supply voltage compared to the MOSFET.

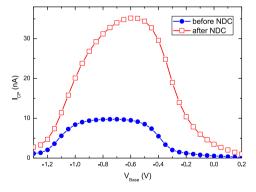

The off-currents  $(I_{OFF})$  in MOSFET and TFET both are below  $10^{-9} \,\mu\text{A}/\mu\text{m}$  at  $V_{DS} = -0.1\,\text{V}$ .  $I_{OFF}$  increases in both devices with increasing  $V_{DS}$ . This effect is known as gate induced drain leakage (GIDL) in a MOSFET and is caused by BTBT at the channel drain junction due to the strong band bending at large gate-to-drain voltage difference. It is pronounced for devices with high- $\kappa$  gate dielectrics and good electrostatic channel control due to the large potential variation of the channel bands with respect to the bands in the drain. The strong band bending decreases the BTBT distance at the channel-drain junction. In a TFET the increase of  $I_{OFF}$  with increasing  $V_{DS}$  is also caused by BTBT at the channel drain junction. The n-channel TFET is switched on due to the symmetric TFET design. The ambipolar behavior of a TFET degrades  $I_{OFF}$  and is especially problematic in digital logic circuits, since the OFF-state of the device is not well defined (see chapter 6).

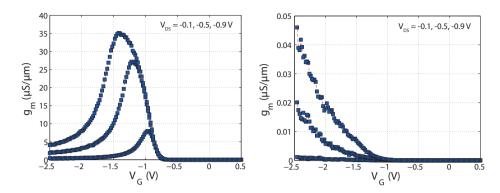

Fig.3.8 shows the transconductance  $g_m$  of the NW MOSFET and TFET derived from the transfer characteristics. Also  $g_m$  exhibits a distinct difference for both devices. Whereas  $g_m$  of the MOSFET has a peak at  $V_G$  between  $-1\,\mathrm{V}$  and  $-1.5\,\mathrm{V}$  depending on  $V_{DS}$ ,  $g_m$  of the TFET increases over the whole range of  $V_G$ .

Fig.3.6 and Fig.3.8 reveal that  $I_{ON}$  and  $g_m$  of the p-MOSFET are about three orders of magnitude higher compared to the p-TFET at the same bias conditions. This means that the resistance of the TFET is also three orders of magnitude higher. Since the NW p-TFET and p-MOSFET are fabricated with the same process on one chip, only with opposite doping types for the source, the channel resistance  $R_{ch}$  is comparable for both devices. From n- and p-MOSFETs with four different gate length the source-drain resistance  $R_{S/D}$  was extracted.  $R_{S/D}$  is 820  $\Omega$  and 1049  $\Omega$  for n- and p-MOSFETs, respectively [84]. Due to the n-doped source and p-doped drain of the p-TFET,  $R_{S/D}$  of this device should be in between these values. Since  $R_{ch}$  and  $R_{S/D}$  are in the same range for MOSFET and TFET the additional large series resistance of the TFET can be attributed to the resistance of the tunneling barrier  $R_{TB}$ . Channel resistance in a MOSFET is caused by the limited carrier mobility. Due to the much smaller current in the TFET channel mobility does not influence the

Figure 3.8: Transconductance  $g_m$  of the SSOI NW array MOSFET and TFET with  $400\,\mathrm{nm}$  gate length.

TFET performance for the measured devices. However, one should note that  $R_{TB}$  depends on  $T_{WKB}$  with exponential dependence on the tunnel junction parameter  $E_g$ ,  $m^*$  and  $\lambda$ . In the case of improved tunnel junction parameter, when  $T_{WKB}$  in eq. (2.12) becomes close to unity, the tunneling resistance can become comparable to  $R_{ch}$  and  $R_{S/D}$ . At this point the TFET current can be limited by channel mobility as in a MOSFET.

Figure 3.9:  $I_D$ - $V_{DS}$  characteristics of SSOI NW array (a) MOSFET and (b) TFET with  $10 \times 10 \text{ nm}^2$  NW cross-section and 400 nm gate length.

Output characteristics of p-MOSFET and p-TFET are shown in Fig.3.9. Besides the difference in  $I_{ON}$ , also the shapes of the output curves differ. The onset of the MOSFET is linear and  $I_D$  saturates for increasing  $V_{DS}$ . The good current saturation of the devices once more proves small DIBL. The output characteristics of the TFET reveal a distinct S-shape, which is caused by drain induced barrier thinning (DIBT) [49]. The super-linear on-set, although it is often observed in TFET output characteristics, it is not an intrinsic TFET feature. Linear output characteristic of TFETs can be restored by adjusting the

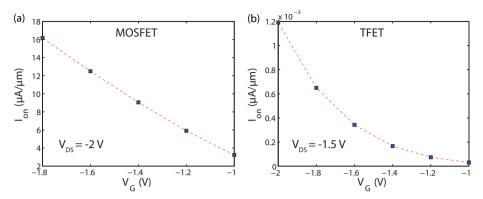

Figure 3.10: Gate voltage dependence of the on-current  $I_{ON}$  showing a linear dependence for the MOSFET (a) and en exponential dependence for the TFET (b).

Fermi distribution function in source and drain by a proper choice of doping levels [68][30]. Linear output characteristics are important in terms of digital logic application, since S-shaped  $I_D$ - $V_{DS}$  characteristics would deteriorate the device performance. An additional striking difference of MOSFET and TFET output characteristics is the  $V_G$  dependence of  $I_{ON}$  shown in Fig.3.10 at  $V_{DS} = -2\,\mathrm{V}$  and  $-1.5\,\mathrm{V}$  for MOSFET and TFET, respectively. Values are extracted from the output characteristics in Fig.3.9. In case of the MOSFET  $I_{ON}$  increases linearly with  $V_G$ , indicating current limitation by velocity saturation due to large source-drain electric field [98]. For a MOSFET with lower source-drain electric field current is limited by the mobility. In the case of a constant mobility  $I_{ON}$  then increases with  $V_G^2$ . Thus, the  $V_G$  dependence of  $I_{ON}$  is always expected between these two extreme cases of constant mobility and velocity saturation.  $I_{ON}$  in the TFET, in comparison, exhibits an exponential dependence of  $V_G$ . This is in agreement with the theoretical expectation, since current in the TFET is limited by BTBT probability.  $I_{ON}$  is proportional to  $T_{WKB}$ , which depends exponentially on  $V_G$ .

### 3.4 TFET Performance

The performance of TFET devices is influenced by several different factors. From eq.(2.12) it is known that the material parameters  $E_g$  and  $m^*$  and the parameter  $\lambda$ , which is defined by the device structure and junction quality, are the most important ones. In the following the influences of device dimensions and junction quality on these parameters will be discussed and an additional effect caused by high electric fields in the junction is described.

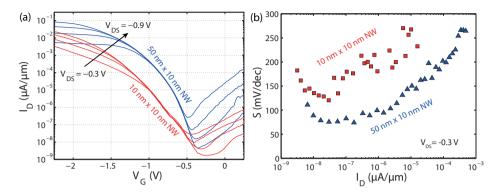

Figure 3.11: (a) Transfer characteristics of SSOI TFETs with  $100\,\mathrm{nm}$  gate length and NW cross-sections of  $50\times10\,\mathrm{nm}^2$  and  $10\times10\,\mathrm{nm}^2$ , respectively. (b) Inverse subthreshold slope S in dependence of  $I_D$ .

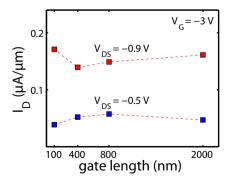

### 3.4.1 NW Cross-section and Gate Length

NW TFETs on SSOI have been fabricated with different NW cross-sections and gate lengths as described in section 3.1. A decrease in NW width results in an enhanced electrostatic gate control and thus a decreased  $\lambda_{ch}$  parameter in equation (2.12), which increases  $I_{ON}$  of the TFET. However there are additional effects that need to be taken into account, which will be discussed in this section.

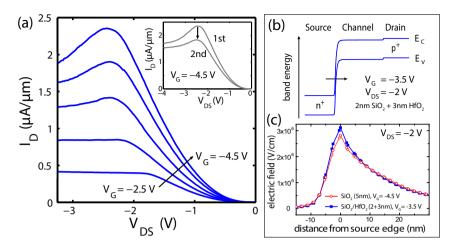

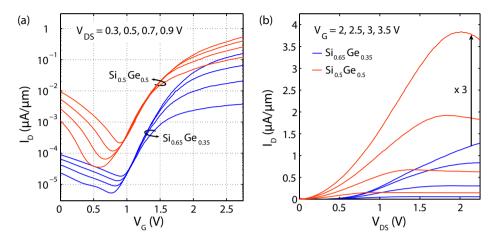

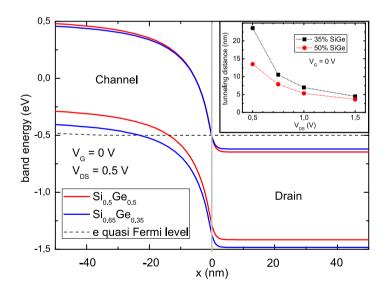

Fig.3.11 (a) shows the comparison of transfer characteristics of SSOI NW TFETs with 100 nm gate length and NWs with 10 nm and 50 nm width, respectively. The transfer characteristics reveal higher on-current as well as steeper S for NWs with  $50 \times 10 \, \mathrm{nm}^2$  cross-section compared to  $10 \times 10 \, \mathrm{nm}^2$  NWs. Fig.3.11 (b) shows a comparison of S in dependence of  $I_D$  for these two devices. The minimum slope of the TFET with 50 nm NW width is 76 mV/dec and  $120 \, \mathrm{mV/dec}$  for the 10 nm NWs. S degrades more rapid with increasing  $I_D$  for the thinner NWs than for the wider NWs. This result is unexpected since a better electrostatic gate control and hence higher performance are expected for a TFET with narrower NWs at constant gate dielectric thickness. However, this result can be explained by the two contributions to the screening length  $\lambda$ , which is given by  $\lambda = \lambda_{ch} + \lambda_{dop}$ .  $\lambda_{ch}$  is influenced by the electrostatic channel control, whereas  $\lambda_{dop}$  depends on the steepness of the source doping profile.

In case of the narrower NWs on the one hand  $\lambda_{ch}$  is decreased, but on the other hand  $\lambda_{dop}$  increases. The tunnel junction formation by ion implantation and spike annealing for activation is affected by the width of the NW. Dopant diffusion in Si NWs can be much higher compared to bulk Si [52]. The diffusion coefficient D of boron in vapor liquid solid (VLS) grown Si NWs for example was reported to be as high as  $D = 4.22 \times 10^{-16} \text{ cm}^2/\text{s}$  [11] compared to a bulk diffusivity of  $\approx 10^{-18} \text{ cm}^2/\text{s}$  at 500 °C [67]. The increased diffusivity is presumably caused by a larger dopant diffusion along the NW surface, due to impurities at

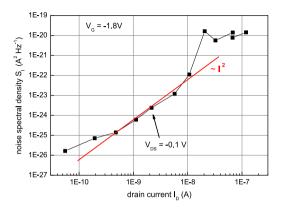

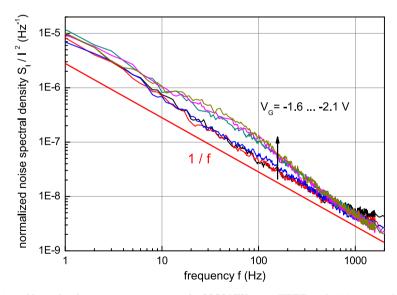

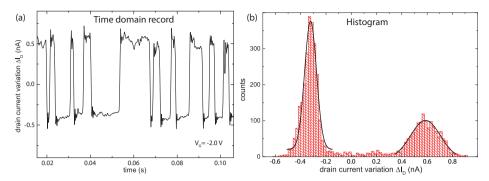

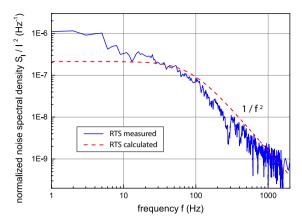

the interface to the gate dielectric [52]. The smaller NW has a larger surface to volume ratio, which could further enhance dopant diffusion compared to the wider NW. Increased dopant diffusion causes a broadening of the doping profiles in the junctions leading to degradation of  $\lambda_{dop}$  and thus smaller  $I_{ON}$  and larger S.  $I_{OFF}$  in the 10 nm NW TFET benefits from the increased boron diffusion at the drain junction. BTBT at the channel-drain junction is suppressed leading to reduced ambipolarity and smaller  $I_{OFF}$  compared to the 50 nm NW. Another aspect why the TFET with wider NWs outperforms the one with thinner NWs could be the reduction of  $E_g$  by the tensile strained substrate. As shown in section 3.2 the strain across a patterned NW relaxes and uniaxial strained NWs are obtained. The degree of relaxation, however, depends also on the NW cross-section. According to Fig.3.5 the strain across thin but wide NWs does not fully relax. Hence, a larger remaining strain component across the 50 nm NW would result in a smaller band gap compared to the 10 nm NW. Also a smaller crystalline seed layer in the narrower NWs after ion implantation may prevent SPER during dopant activation and result in higher trap density in the tunnel junction.