Zentralinstitut für Angewandte Mathematik

Untersuchungen zur Ablaufplanung bei Parallelrechnern mit virtuell gemeinsamem Speicher

Markus Andreas Linn

Berichte des Forschungszentrums Jülich ; 2931 ISSN 0944-2952 Zentralinstitut für Angewandte Mathematik Jül-2931 D 82 (Diss. RWTH Aachen)

Zu beziehen durch: Forschungszentrum Jülich GmbH - Zentralbibliothek D-52425 Jülich - Bundesrepublik Deutschland Telefon: 02461/61-6102 - Telefax: 02461/61-6103 - Telex: 833556-70 kfa d

# Untersuchungen zur Ablaufplanung bei Parallelrechnern mit virtuell gemeinsamem Speicher

Markus Andreas Linn

### **Kurzfassung**

Die Ablaufplanung von parallelen Programmen bei Rechnern mit virtuell gemeinsamem, real jedoch auf die Prozessoren verteiltem Speicher wird maßgeblich von zwei Problembereichen beeinflußt: Auf der einen Seite hängt der effiziente Betrieb dieser Rechner von der Lokalität der Daten ab; die Daten müssen am Ort des Zugriffs weitgehend lokal verfügbar sein, sonst ergeben sich permanent Datentransfers, die die Programmausführung verzögern. Auf der anderen Seite können unbalancierte Arbeitslasten die effiziente Ausführung behindern. Die Berücksichtigung beider Aspekte durch eine explizite Datenabbildung zur Maximierung der Datenlokalität bei gleichzeitiger Optimierung der thread-Scheduler-Algorithmen kann zu Effizienzvorteilen bei Systemen mit virtuell gemeinsamem Speicher führen.

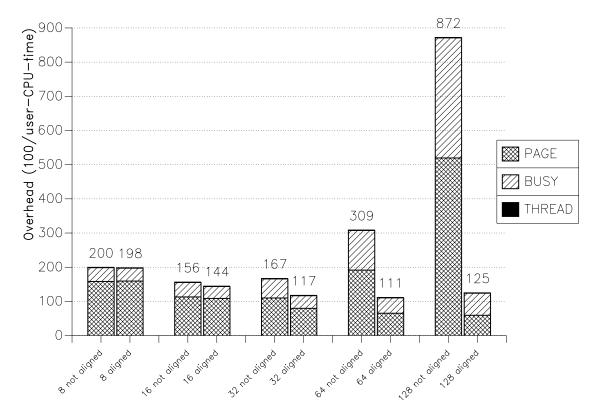

Die vorgestellten Ergebnisse basieren auf Untersuchungen, die mithilfe eines Simulationssystems durchgeführt wurden. Dazu wurden unabhängige Modelle für das Parallelrechnersystem, für den virtuell gemeinsamen Speicher und für die Arbeitslast entwickelt und implementiert. Die Scheduler-Komponente des Simulators umfaßt sowohl die bereits von den Systemen mit global gemeinsamem Speicher her bekannten thread-Scheduler-Algorithmen als auch neue algorithmische Varianten, die auf die besonderen Belange bei Systemen mit virtuell gemeinsamem Speicher geeignet angepaßt sind. Darüber hinaus ist eine explizite Datenabbildung entwickelt und in das Simulationssystem integriert worden. Die Untersuchungen zeigen, daß eine geeignete Datenabbildung von der Art der Arbeitslast abhängt und explizit wählbar sein muß. Ebenso muß auch das thread-Scheduling in Abhängigkeit von der Arbeitslast, deren Datenzugriffsstruktur und den daraus resultierenden Speicherreferenzen geeignet wählbar sein. Alle durchgeführten Untersuchungen zeigen, daß der Einfluß der Datenzugriffsmuster auf die Ausführungszeit erheblich ist: Der bei ungeeigneter Ablaufplanung entstehende Overhead kann in ungünstigen Fällen um Größenordnungen über dem eigentlichen CPU-Zeitbedarf einer Anwendung liegen. Dies zeigt die strategische Bedeutung einer effizienten Ablaufplanung bei Parallelrechnern mit virtuell gemeinsamem Speicher.

## Inhaltsverzeichnis

| 1. Einleitung                                                         |

|-----------------------------------------------------------------------|

| 2. Globaler Adreßraum für Rechner mit verteiltem Speicher 5           |

| 2.1. Virtual Shared Memory - Versuche der Einordnung 6                |

| 2.2. Konzepte der massiv-parallelen Programmierung                    |

| 2.2.1. Das DSM-Modell: Shared Memory auf einer NUMA-Architektur 11    |

| 2.2.2. Das CSM-Modell: Transformation von Shared-Memory-Programmen 11 |

| 2.2.3. Das VSM-Modell: Globaler Adreßraum durch Demand Paging 14      |

| 3. Virtual Shared Memory                                              |

| 3.1. Speichermanagement in VSM-Systemen                               |

| 3.1.1. Speicherzugriffsmodelle                                        |

| 3.1.2. Kohärenzstrategien                                             |

| 3.1.3. Implementierung von Kohärenzstrategien                         |

| 3.1.3.1. Software-Mechanismen: Page-Fault-Handler und -Server         |

| 3.1.3.2. Hardware-Mechanismen                                         |

| 3.1.4. Speicher-Allokation                                            |

| 3.1.5. Speicher-Mapping                                               |

| 3.1.6. Seitenersetzung                                                |

| 3.2. Prozeßverwaltung                                                 |

| 3.2.1. Prozeßkontrolle                                                |

| 3.2.2. Prozeßsynchronisation                                          |

| 3.2.3. Prozeß-Scheduling                                              |

| 3.2.3.1. Prozeßmigration                                              |

| 3.2.3.2. Kontextwechsel                                               |

| 4. Relevante Algorithmen zur Ablaufplanung                            |

| 4.1. Grundlagen für das Scheduling                                    |

| 4.1.1. Parallelisierungskonzepte                                      |

| 4.1.2. Beschreibungskriterien                                         |

| 4.1.3. Basismodelle                                                   |

| 4.2. Scheduling-Algorithmen für unabhängige Tasks                     |

| 4.3. Scheduling-Algorithmen für abhängige Tasks                       |

| 4.3.1. Scheduling in massiv-parallelen Systemen                       |

| 4.3.2. Scheduling in Shared-Memory-Systemen                           |

| 4.3.2.1. Job-bezogenes Scheduling                                     |

| 4.3.2.2. Locality-Scheduling                                          |

| 4.4. Loop-Scheduling                                    | 52        |

|---------------------------------------------------------|-----------|

| 4.5. Analyse der Algorithmen                            | 56        |

| 4.5.1. Das Job-Scheduling                               | 57        |

| 4.5.1.1. Task-Abhängigkeiten                            | 58        |

| 4.5.1.2. Verteiltes Scheduling                          | 60        |

| 4.5.1.3. Forderung nach Lokalität                       | 60        |

| 4.5.2. Das Thread-Scheduling                            | 60        |

| 4.6. Bewertung der Algorithmen                          | 61        |

| 5. Die Ablaufplanung in VSM-Systemen                    | 63        |

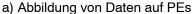

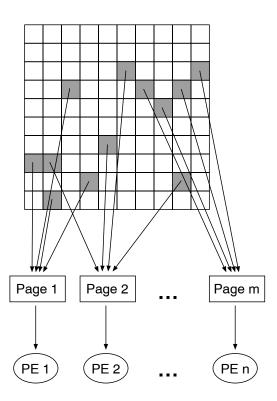

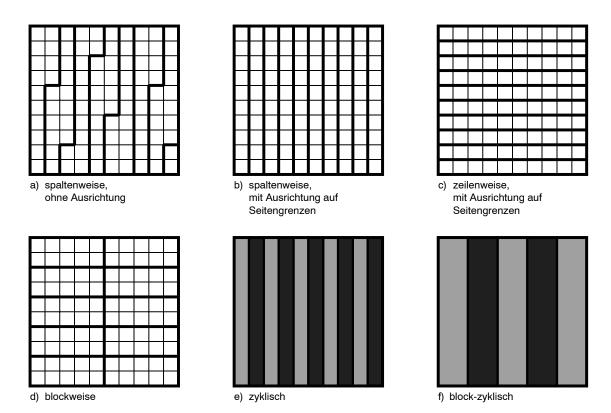

| 5.1. Die Abbildung von Daten auf Seiten                 | 63        |

| 5.2. Thread-Scheduling für charakteristische Schleifen  | 70        |

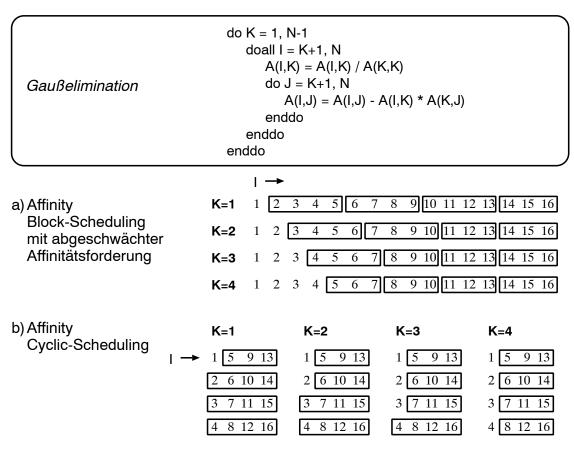

| 5.2.1. Schleifennester mit Affinität                    | 70        |

| 5.2.2. Schleifennester ohne Affinität                   | 73        |

| 5.2.3. Geschachtelte parallele Schleifen                | 74        |

| 6. Ein Virtual-Shared-Memory-Simulator                  | 81        |

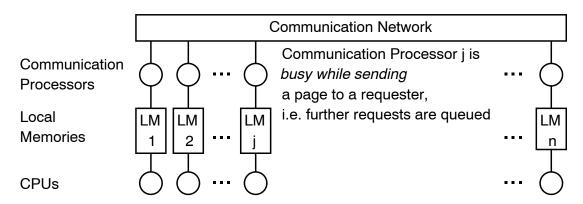

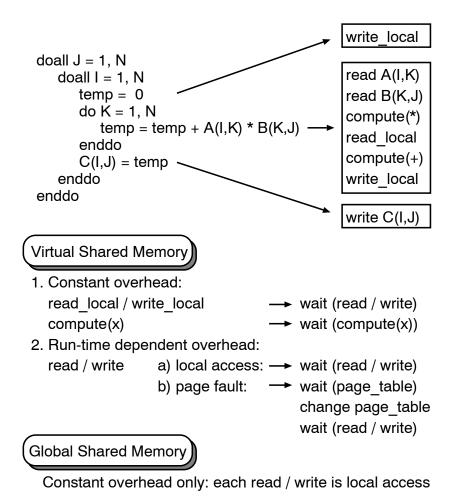

| 6.1. Das VSM-Modell                                     | 81        |

| 6.2. Das Multiprozessormodell                           | 84        |

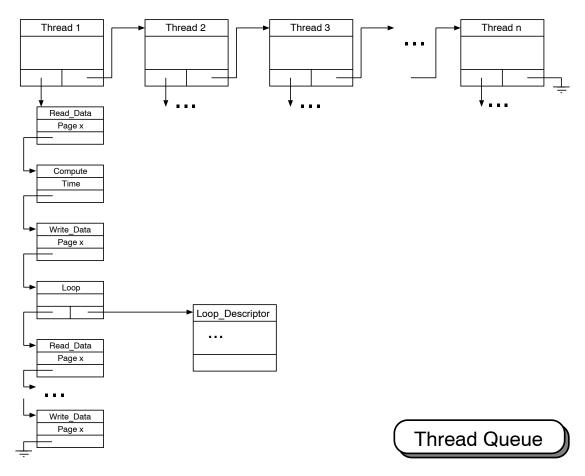

| 6.3. Das Arbeitslastmodell                              | 86        |

| 6.4. Simulationsparameter                               | 89        |

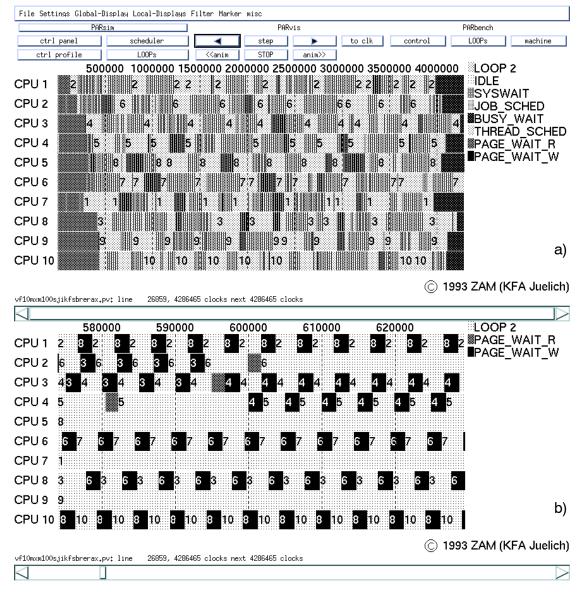

| 6.5. Auswertung der Simulationen                        | 92        |

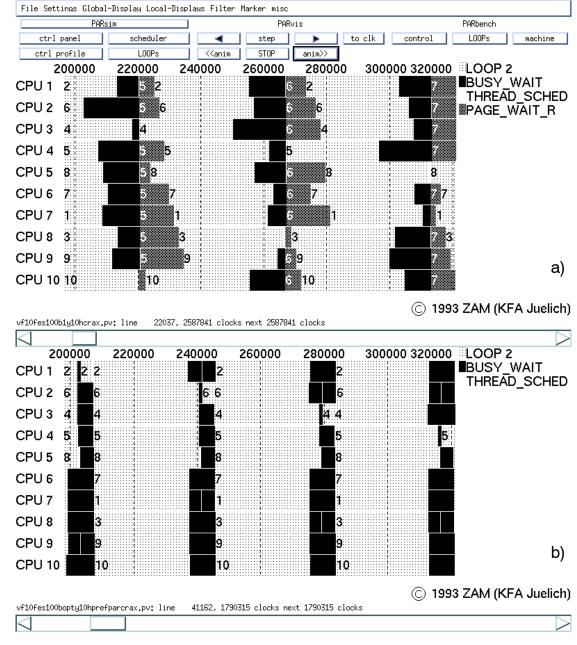

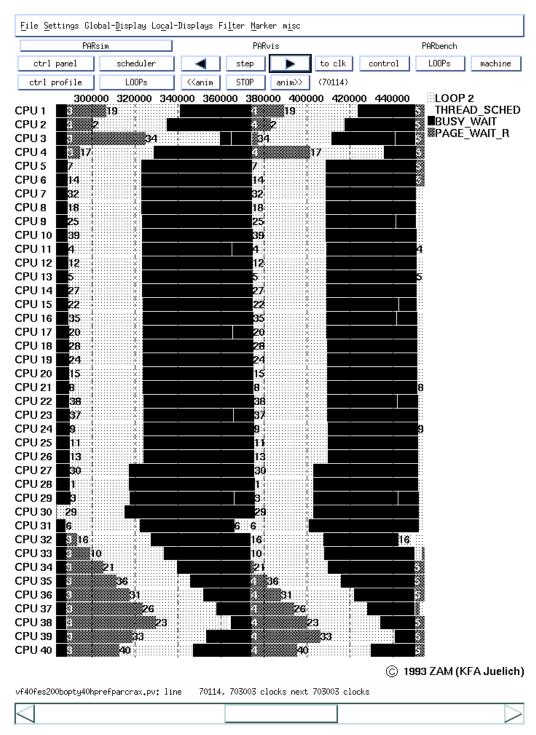

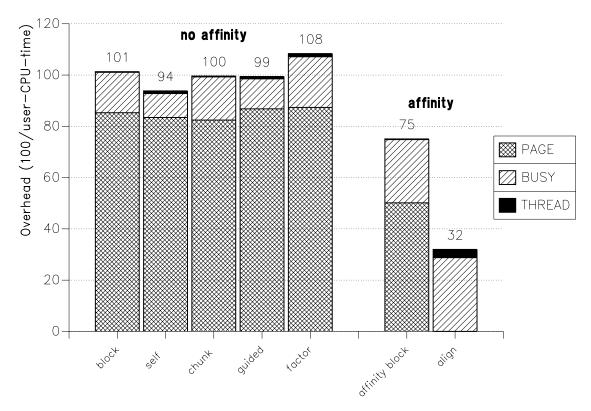

| 7. Simulationsergebnisse                                | 95        |

| 7.1. Der Einfluß der Abbildung von Daten auf Seiten     | 96        |

| 7.1.1. Fallstudien mit verschiedenen Programmkernen     | 96        |

| 7.1.2. Fallstudien bezüglich der Seitengröße            | 05        |

| 7.2. Thread-Scheduling für Seiten mit mehreren Vektoren | 07        |

| 7.3. Einfache Affinitäten in Schleifennestern           |           |

| 7.4. Affinität in triangularen Schleifennestern         | 14        |

| 7.5. Schleifennester mit Indexadressierung              |           |

| 7.6. Parallelität auf verschiedenen Schleifenebenen     |           |

| 8. Folgerungen für die Ablaufplanung in VSM-Systemen    | 33        |

| 9. Zusammenfassung und Ausblick                         | 43        |

|                                                         | <b>17</b> |

Die Historie der Entwicklung von elektronischen Rechnern ist seit Anbeginn geprägt durch eine immense Steigerung ihrer Leistungsfähigkeit. Dennoch stellt die maximale Rechenleistung heutiger Supercomputer für eine Vielzahl von Anwendern eine Grenze dar, die weit unterhalb der von ihnen benötigten Leistung liegt. Forschungsgegenstand in Naturwissenschaften und Technik sind heute zunehmend komplexe, nicht-lineare Systeme, für die sich das Werkzeug der numerischen Simulation als ein unverzichtbares Instrument entwickelt [CPME93, Hos91, Wil89]. In vielen Fällen können Lösungen aufgrund der Rechenzeitanforderungen nur näherungsweise oder aber nur für kleine Problemgrößen erhalten werden. Eine befriedigende Behandlung dieser Aufgabenstellungen erfordert weitere Leistungssteigerungen im Supercomputing; dazu können grundsätzlich die folgenden vier Bereiche beitragen:

- Technologie

- Architektur

- Algorithmik

- Software-Technik

Algorithmik und Software-Technik sind wesentlich an die Vorgaben durch die Architektur gebunden; Technologie und Architektur bestimmen ihrerseits die eigentliche Rechengeschwindigkeit bezogen auf Operationen pro Zeiteinheit. An der Steigerung der Leistungsfähigkeit von Supercomputern hat die Erhöhung der Rechengeschwindigkeit einen erheblichen Anteil [Led90b]; am meisten haben technologische Neuerungen beigetragen: Der Übergang von elektromechanischen Relais über Elektronenröhren und Transistoren zu integrierten Halbleiterbauelementen (ICs) mit immer höherer Integrationsdichte und Schaltgeschwindigkeit kennzeichnet die Verkürzung der Rechnertaktzeiten von Zehntelsekunden auf Nanosekunden. Da elektrische Signale in einer Nanosekunde nur etwa dreißig Zentimeter Laufstrecke zurücklegen, müssen für eine weitere Verkürzung der Taktzeit die räumlichen Abstände innerhalb der Rechner kleiner werden. Damit ist offensichtlich, daß eine weitere Verkürzung der Taktzeit auf absehbare Zeit nur begrenzt möglich ist, mit Sicherheit jedoch nicht um mehrere Größenordnungen; seit mehreren Jahren werden auf der technologischen Seite auch mit erheblichem Aufwand keine Beschleunigungen im erwünschten Maße, d.h. um Größenordnungen erzielt.

Die stagnierende Entwicklung auf der technologischen Seite läßt der Rechnerarchitektur eine wachsende Bedeutung zukommen und hat bereits in der Vergangenheit einer Klasse von Rechnern den Weg bereitet, die Gegenstand der aktuellen Forschung und Entwicklung ist, der Klasse von Multiprozessorrechnern mit MIMD-Architektur (MIMD = *Multiple Instruction stream - Multiple Data stream* [Fly66]). Den bis vor etwa zehn Jahren im Supercomputing führenden Einprozessorrechnern haben Multiprozessorrechner zum Beispiel der Firmen Cray oder NEC den Rang abgelaufen. Diese Multiprozessorrechner nutzen heute bis zu 4, 8 oder 16 Prozessoren, die auf einem gemeinsamen Speicher arbeiten; wegen der kleinen Prozessorzahl werden diese Rechner als moderat-parallel bezeichnet.

Einleitung 1

Eine Entwicklung in Richtung wachsende Prozessorzahl zeichnet sich seit einigen Jahren ab: Das Erreichen einer wiederum technologisch bedingten Grenze hat bei Rechnern mit vergleichsweise sehr viel mehr Prozessoren (massiv-parallele Rechner) zur Realisierung einer abermals neuen Architektur geführt: Multiprozessorrechner mit verteiltem Speicher. Damit ergeben sich drei Klassen von Rechnerarchitekturen: Die Einprozessorrechner, die moderat-parallelen Rechner mit gemeinsamem Speicher und die massiv-parallelen Rechner mit verteiltem Speicher.

Bei der Entwicklung neuer Rechnerarchitekturen hat die Entwicklung der zugehörigen System-Software nicht schritthalten können. Die neuartigen Architekturkonzepte bedingen ebenfalls neue Konzepte für die Software-getriebene Steuerung der Rechner; ohne entsprechende Betriebssystemunterstützung ist die ihrer Leistungsfähigkeit angemessene Nutzung nicht gewährleistet. Bei Einprozessorrechnern hat die System-Software aufgrund der langjährigen Weiterentwicklungen des von-Neumann-Konzeptes einen soliden Status erreicht und kann als weitgehend ausgereift bezeichnet werden. Bei Multiprozessorrechnern mit gemeinsamem Speicher sind trotz der erheblichen Erfolge der letzten Jahre entsprechende Implementierungen bisher noch lückenhaft; weiterführende Konzepte sind Gegenstand aktueller Entwicklungen: Die Integration von parallelen Programmen in eine Mehrbenutzerumgebung zum Beispiel kann in bestimmten Situationen nur durch neuartige Strategien zufriedenstellend gelöst werden [Nag93]. Die bei Rechnern mit verteiltem Speicher verwendeten Konzepte basieren zum Teil auf denen für Rechner mit gemeinsamem Speicher und sind damit ebenfalls verbesserungswürdig. Darüber hinaus stellt die Architektur des verteilten Speichers neue Anforderungen an die System-Software: Die Mehrzahl heutiger Rechner mit verteiltem Speicher realisiert das message-passing-Programmiermodell. Der wesentliche Nachteil des message passing die für viele Anwendungen aufwendige Programmierung durch die explizite Spezifikation der Datenkommunikation - hat bisher zu einer eingeschränkten Benutzerakzeptanz geführt. Verschiedene Forschungsprojekte beschäftigen sich heute mit der Programmierbarkeit von Rechnern mit verteiltem Speicher. Hinter den Schlagworten datenparallele Programmierung und virtuell gemeinsamer Speicher verbergen sich Programmiermodelle, die eine im Vergleich zum message passing einfachere Programmierung erlauben sollen [HPF93, Li86]. Eine allen Programmiermodellen zur Architektur des verteilten Speichers gemeinsame Problemstellung liegt in der geeigneten Gruppierung und Verteilung der Daten über den Speicher; die Programmausführung kann nur dann effizient sein, wenn die benötigten Daten im jeweiligen Speicher lokal verfügbar sind (Lokalität der Datenzugriffe). Bei der Definition von Programmiersprachen zu den Programmiermodellen werden Direktiven zur Beeinflussung der Datenverteilung und damit zur Erhöhung der Lokalität integriert [BGNP93, BKP93, HPF93].

Eine entscheidende Rolle für die Verbesserung der Lokalität kann in Rechnern mit verteiltem Speicher der Ablaufplanung zukommen. Die Ablaufplanung bei der Ausführung paralleler Programme umfaßt drei Problemstellungen: Die Identifikation von Parallelität innerhalb eines Programms, die Partitionierung der parallelen Programmteile in Teilaufgaben und das Scheduling der Teilaufgaben auf die Prozessoren. Die Identifikation von Parallelität bezieht sich auf den Algorithmus beziehungsweise auf dessen Darstel-

lung mithilfe der Programmiersprache; sie kann durch den Benutzer oder durch den Compiler erfolgen und soll in dieser Arbeit nicht weiter betrachtet werden. Die Partitionierung und das Scheduling sind jedoch von der zugrundeliegenden Rechnerarchitektur und dem Programmiermodell abhängig. In dieser Arbeit werden die Partitionierung und das Scheduling bei Rechnern mit virtuell gemeinsamem Speicher untersucht. Da es sich dabei um Parallelrechner mit verteiltem Speicher handelt, kommt insbesondere der Forderung nach Datenlokalität und den damit verbundenen zusätzlichen Anforderungen an Partitionierung und Scheduling große Bedeutung zu. Bisher wurden zu diesem Thema nur wenige Arbeiten veröffentlicht: Eine Arbeit aus jüngster Zeit behandelt die Partitionierung bei Rechnern mit virtuell gemeinsamem Speicher [GrWi93]. Für die Ablaufplanung bei Rechnern mit virtuell gemeinsamem Speicher ergibt sich eine zusätzliche Aufgabenstellung: Das Speicherkonzept unterstützt die automatische Partitionierung und Verteilung der Daten; um eine effiziente Ausführung zu erzielen, müssen Partitionierung und Verteilung auf die Datenzugriffsmuster von Anwendungsprogrammen abgestimmt werden können. Durch geeignete Strategien für diese Automatismen kann die Effizienz der Ausführung deutlich verbessert werden. Diesbezüglich sind in der Literatur bisher keine Arbeiten zu finden.

Das Modell des virtuell gemeinsamen Speichers überträgt das komfortable Progammiermodell des gemeinsamen Speichers auf Rechner mit verteiltem Speicher [Li86]. Daneben gibt es heute verwandte Modelle, die ähnliche Ziele verfolgen. Kapitel 2 versucht eine Abgrenzung der Modelle gegeneinander sowie deren Einordnung in bestehende Taxonomien.

Die in der Literatur beschriebenen Ansätze zum Modell des virtuell gemeinsamen Speichers basieren auf unterschiedlichen Teilkonzepten. Kapitel 3 stellt die verschiedenen Konzepte und bei der Implementierung verwendeten Mechanismen gegenüber; dabei stehen sowohl das Speichermanagement als auch die Prozeßverwaltung im Mittelpunkt.

In Multiprozessorrechnern bestimmt das Scheduling einen wesentlichen Teil der Ablaufplanung; im folgenden wird der Begriff Scheduling auch als Oberbegriff für die Kombination von Partitionierung und Scheduling verwendet. Die in der Vergangenheit entwickelten Ansätze basieren auf unterschiedlichen Rechnerarchitekturen und beschreiben eine Vielfalt von Algorithmen für das Scheduling auf verschiedenen Hierarchieebenen. Im Kapitel 4 werden Betrachtungen zum Scheduling angestellt, die sich in die Ebenen des Job-Scheduling und des *thread*-Scheduling gliedern. Für die Vergleichbarkeit werden zunächst allgemeine Beschreibungskriterien und jeweils zugrundeliegende Basismodelle erarbeitet.

Diese Arbeit stellt einen der ersten Schritte auf dem Gebiet des Scheduling in Rechnern mit virtuell gemeinsamem Speicher dar. Um eine Grundlage für weiterführende Arbeiten zu schaffen, werden die Betrachtungen auf das *thread-*Scheduling konzentriert. Kapitel 5 betrachtet das *thread-*Scheduling bei Rechnern mit virtuell gemeinsamem Speicher. Es werden Algorithmen und Strategien vorgestellt, die zu deutlichen Verbesserungen führen.

Die vorgestellten Algorithmen und Strategien werden mithilfe von Simulationsrechnungen untersucht. Kapitel 6 beschreibt ein Simulationssystem, das im Rahmen dieser

Einleitung 3

Arbeit implementiert worden ist. Das Simulationssystem basiert auf unabhängigen Modellen für das Multiprozessorsystem, für den virtuell gemeinsamen Speicher und für die auszuführenden Arbeitslasten.

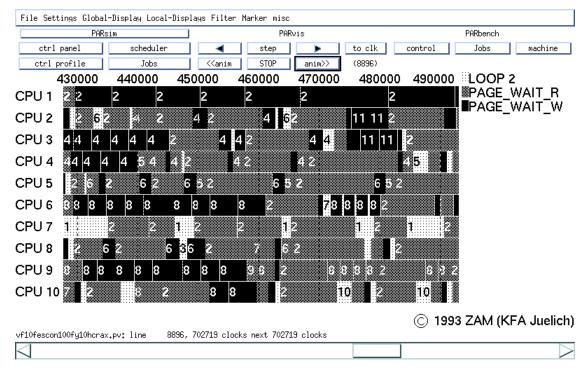

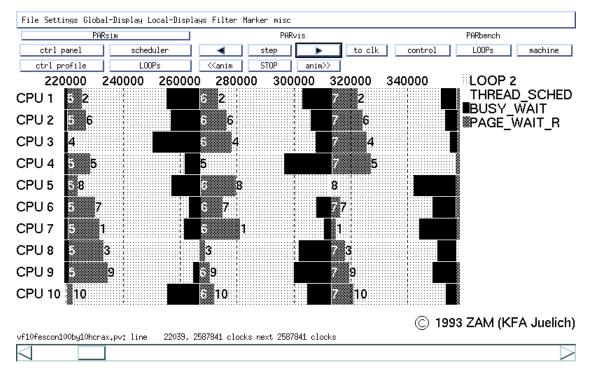

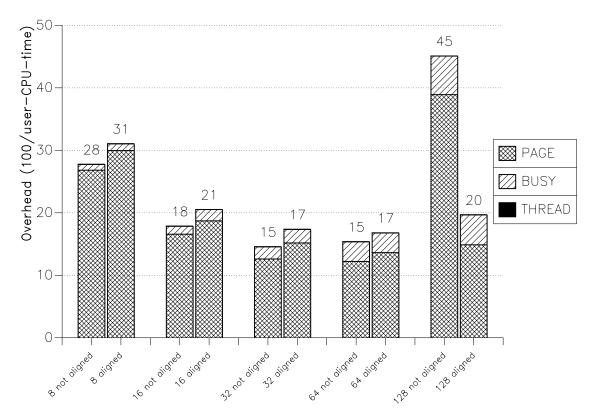

In Kapitel 7 erfolgt die Untersuchung der vorgestellten Algorithmen. Zu diesem Zweck stehen zum einen statistische Daten aus den Simulationsläufen zur Verfügung, die eine vergleichende Bewertung erlauben. Darüber hinaus generiert das Simulationssystem Informationen zu diskreten Zustandswechseln von Prozessen und Speicher, die Einsichten in diese Abläufe geben und zu neuen Strategien für die Ablaufplanung führen.

Den Simulationsuntersuchungen liegen reale Arbeitslasten zugrunde; die Arbeitslasten und die entsprechenden Untersuchungsparameter wurden so gewählt, daß für die Ablaufplanung relevante Problemstellungen jeweils umfassend behandelt werden konnten. Kapitel 8 verdeutlicht die Bedeutung der Untersuchungen im Gesamtkontext der Ablaufplanung, faßt die gewonnenen Ergebnisse zusammen und stellt Folgerungen für die Ablaufplanung in Systemen mit virtuell gemeinsamem Speicher auf.

#### 2. Globaler Adreßraum für Rechner mit verteiltem Speicher

Das Erreichen einer technologischen Grenze für die Geschwindigkeit einzelner Prozessoren und die Möglichkeit der Kombination von preiswerten Hochleistungs-Mikroprozessoren hat zur Entwicklung von Rechnern mit sehr großer Prozessorzahl geführt (massiv-parallele Rechner). Die mit wachsender Prozessorzahl entstehenden Anforderungen (eine ebenfalls wachsende Speicherbandbreite bei gleichbleibender Zugriffsverzögerung) bedingen eine Änderung des in Parallelrechnern mit nur wenigen Prozessoren bewährten Konzeptes eines globalen Speichers: Im Unterschied zu Rechnern, bei denen alle Prozessoren auf einen globalen Speicher einheitlich zugreifen können, wird in massiv-parallelen Systemen der Speicher über die Prozessoren verteilt, d.h. jedem Prozessor wird jeweils ein Speichermodul lokal zugeordnet. Aufgrund der Verteilung des Speichers ergibt sich eine Vielzahl neuer Problemstellungen für den Betrieb dieser Rechner. Die Programmierbarkeit massiv-paralleler Rechner stellt ein wesentliches Problem dar: In existierenden Systemen ermöglicht das message-passing-Programmiermodell eine komfortable Programmierung nur für wenige, besonders geeignete Anwendungen; für den universellen Einsatz massiv-paralleler Rechner stellt das message-passing-Programmiermodell ein entscheidendes Akzeptanzhemmnis dar. Für die meisten Anwendungen im wissenschaftlich-technischen Bereich ist die sharedmemory-Programmierung einfacher als die message-passing-Programmierung, da bei der shared-memory-Programmierung die Datenallokation für den Programmierer transparent ist; das shared-memory-Programmiermodell erlaubt, im Gegensatz zu explizit lokalen und nicht-lokalen Referenzen beim message-passing-Programmiermodell, die Verwendung von globalen Referenzen. Die wachsende Bedeutung von Rechnern mit verteiltem Speicher in Verbindung mit der Überlegenheit des shared-memory-Programmiermodells über das message-passing-Programmiermodell hat zur Entwicklung von Konzepten geführt, die die shared-memory-Programmierung auch auf Rechnern mit verteiltem Speicher ermöglichen. Die unterschiedlichen Konzepte implementieren verschiedene sharedmemory-Rechnermodelle, die sich durch die Art der Abbildung des shared memory auf den verteilten Speicher unterscheiden; die Abbildung wird durch die Hardware, durch das Betriebssystem, durch den Compiler oder durch eine Kombination dieser Komponenten unterstützt.

Ein wesentliches Rechnermodell dieser Kategorie verfolgt das Konzept des virtuell gemeinsamen Speichers; dieses Modell findet sich in der Literatur bereits seit 1986 [Li86]. Mit der Vielzahl der seitdem veröffentlichten Arbeiten zu diesem Konzept gibt es auch eine Vielfalt von Namen für dieses Rechnermodell, die von shared virtual memory, virtual shared memory, distributed virtually shared memory und distributed shared memory bis zu ALLCACHE memory reichen [Li86, GHSS91, BoIs91, BCZ90a, KSR92]. Diese Ansätze basieren auf einem Rechnermodell mit virtuell gemeinsamem Speicher, der jedoch nur logisch existiert und in der Realität auf einen verteilten Speicher abgebildet wird. Aus Gründen der Einheitlichkeit wird in diesem Zusammenhang im weiteren Verlauf dieser Arbeit von virtual shared memory (VSM) gesprochen.

Die Verschiedenartigkeit der Namen von VSM-Ansätzen geht einher mit unterschiedlichen Hardware-Plattformen und unterschiedlichen Implementierungen. Das Spektrum

der Hardware macht eine Einordnung des VSM-Modells in die Welt der Supercomputer-Parallelrechner problematisch. Abschnitt 2.1 setzt das Rechnermodell des *virtual shared memory* in Relation zu anderen Modellen aus dem Bereich der Supercomputer-Parallelrechner. In diesem Zusammenhang wird auch versucht, eine Abgrenzung des VSM-Modells gegenüber verwandten Modellen im Bereich der *shared-memory*-Rechnermodelle für Rechner mit verteiltem Speicher vorzunehmen; dabei werden Vorund Nachteile von Modellen und Konzepten diskutiert. Eine wesentliche Motivation des VSM-Modells liegt in der Programmierbarkeit von massiv-parallelen Rechnern; in Abschnitt 2.2 wird die Betrachtung auf massiv-parallele Systeme eingeschränkt, und es werden drei Konzepte für die massiv-parallele Programmierung beschrieben.

#### 2.1. Virtual Shared Memory - Versuche der Einordnung

In existierenden Taxonomien, die eine Einordnung von virtual-shared-memory-Systemen erlauben, sind Definitionen und Nomenklatur nicht einheitlich, es werden zum Teil die gleichen Begriffe mit verschiedenen Definitionen belegt. In einer informellen Taxonomie für MIMD-Systeme<sup>1</sup> definiert Karp zwei Systeme [Kar87]: Die Taxonomie klassifiziert Systeme mit einem global zugreifbaren, gemeinsamen Speicher als shared-memory-Systeme. In message-passing-Systemen verfügt laut Karp jeder Prozessor über lokal zugreifbaren Speicher, ein global zugreifbarer Speicher existiert jedoch nicht. Nach Karp gehören VSM-Systeme, die tatsächlich nur über lokalen Speicher verfügen, deren Betriebssystem jedoch die Illusion eines globalen Speichers erzeugt, zu einer Klasse von hybriden Systemen. Eine detailliertere Einordnung in den Taxonomien von Howe und Moxon [HoMo87] beziehungsweise von Johnson [Joh88] erfordert eine differenzierte Sichtweise. Beide Taxonomien definieren jeweils zwei Architekturmodelle und, orthogonal dazu, jeweils zwei Kommunikations- beziehungsweise Programmiermodelle. Ein Unterschied zwischen den beiden Taxonomien besteht in den Definitionen der Architekturmodelle: Howe und Moxon unterscheiden zwischen shared-memory-Architekturen mit von allen Prozessoren direkt zugreifbarem Speicher und private-memory-Architekturen, bei denen die Speichermodule anderer Prozessoren nicht direkt zugreifbar sind [HoMo87]. Johnson dagegen definiert global-memory-Architekturen mit einheitlicher Speicherzugriffszeit für alle Prozessoren und distributed-memory-Architekturen, die durch unterschiedliche Zugriffszeit für lokale beziehungsweise nicht-lokale Zugriffe charakterisiert sind. Aus Gründen der Eindeutigkeit bei der Begriffsbildung wird im weiteren Verlauf dieser Arbeit die Taxonomie von Johnson zugrunde gelegt, die im folgenden detailliert beschrieben und bezüglich der Einordnung von virtual-shared-memory-Systemen erweitert wird [Joh88]:

Die Einordnung des *virtual-shared-memory*-Modells mit real verteiltem, virtuell aber gemeinsamem Speicher macht eine differenzierte, zweidimensionale Sichtweise des Speichers notwendig. Es wird unterschieden zwischen der logischen Sicht des Speichers vom Standpunkt des Programmierers und der physikalischen Sicht des Speichers. Die logische Sicht entspricht der Sicht des Speichers aufgrund des Programmiermodells, die physikalische Sicht des Speichers entspricht der physikalischen Prozessor-Speicher-Anordnung.

MIMD = Multiple Instruction stream - Multiple Data stream [Fly66]

Die Einordnung von Rechnermodellen (z.B. *virtual-shared-memory*-Rechnermodell) wird aufgrund von Programmiermodell und Prozessor-Speicher-Anordnung vorgenommen. Die logische Sichtweise unterscheidet zwischen zwei Programmiermodellen, dem *shared-memory*-Programmiermodell, und dem *message-passing*-Programmiermodell.

- Beim shared-memory-Programmiermodell können alle Prozesse auf den gesamten Speicher direkt zugreifen, alle Daten sind global bekannt. Die Kommunikation und die Synchronisation erfolgen mittels gemeinsamer Daten (shared variables). Das shared-memory-Paradigma befreit den Programmierer von der Datenpartitionierung, die Transparenz der Datenallokation vereinfacht eine dynamische Lastbalancierung.

- Beim *message-passing-*Programmiermodell verfügt jeder Prozeß über einen Speicherbereich, auf den er nur selbst zugreifen kann (*private memory*); alle Daten sind jeweils nur lokal bekannt. Die Kommunikation zwischen Prozessen und die Synchronisation der Prozesse können nur mithilfe von erfolgen. Die *message-passing-*Programmierung erfordert eine explizite Datenpartitionierung sowie explizit lokale und nicht-lokale Referenzen, was in vielen Anwendungen mit erheblichem Aufwand verbunden ist.

Aus physikalischer Sicht werden zwei Prozessor-Speicher-Anordnungen unterschieden:

- Ein globaler Speicher (*global memory*) ist für alle Prozessoren gleichwertig zugreifbar; die zugrundeliegende Hardware entspricht einer UMA- (*Uniform Memory Access*) Architektur [ThCr88, You87].

- Die zweite Prozessor-Speicher-Anordnung ist der verteilte Speicher (distributed memory), bei der jedem Prozessor ein Speichermodul lokal zugeordnet ist. Die distributed-memory-Architektur kann auf zwei verschiedene Arten realisiert werden, als NORMA- (NO Remote Memory Access) oder als NUMA- (Non-Uniform Memory Access) Architektur [ThCr88, You87]. Auf einer NORMA-Architektur erfolgt die Kommunikation Message-basiert, ein direkter Zugriff auf einen Speichermodul eines anderen Prozessors ist nicht möglich. Auf einer NUMA-Architektur ist ein solcher Zugriff möglich, jedoch ist die Zugriffszeit größer als für einen Zugriff auf den eigenen Speichermodul.

Das Konzept des *global memory* führt zu Skalierungsproblemen, d.h. bestimmte leistungsrelevante Eigenschaften können mit wachsender Prozessorzahl nicht erhalten werden, sie skalieren nicht. Eine wesentliche Eigenschaft ist z.B. die Speicherunterstützung: Eine wachsende Anzahl von Prozessoren erfordert ein entsprechendes Wachsen der Datenmenge, die der Speicher pro Zeiteinheit verfügbar machen kann (Speicherbandbreite). Die Forderung nach gleichbleibend geringer Verzögerung bei der Auflösung einer Speicherreferenz (Speicherverzögerung) läßt sich bei wachsender Speicherbandbreite nicht befriedigen, d.h. bei konstanter Speicherverzögerung kann die Speicherbandbreite nicht mit der Prozessorzahl skalieren. Ein weiteres wesentliches Skalierungsproblem stellt die schnelle Koordinierung einer wachsenden Anzahl von *tasks* dar. In existierenden Systemen wird die Koordinierung von *tasks* mittels gemeinsamer Variablen (*shared variables*) geregelt. Da der Zugriff auf die gemeinsamen Register sequentiell erfolgt, steigt die gesamte Verzögerung aufgrund der Koordinierung einer Serie von *tasks* linear mit der Anzahl der *tasks*; dieser Effekt wird als *convoy*-Problem bezeichnet [SHH90].

Das Konzept des distributed memory erlaubt eine Lösung der Skalierungsprobleme. Durch die Kopplung von lokalen Speichern mit Prozessoren kann, bei konstanter Speicherbandbreite je Prozessor, die Speicherbandbreite des Gesamtsystems mit der Prozessorzahl skalieren; die Speicherverzögerung bleibt dabei auf Prozessorebene, d.h. für lokale Datenzugriffe konstant. Aus dieser Strategie ergibt sich die Forderung nach Datenlokalität, ohne die eine effiziente Programmausführung nicht gewährleistet ist. Die Forderung nach Datenlokalität stellt einen wesentlichen Nachteil aller auf distributed-memory-Rechnern implementierten Rechnermodelle dar. Die Lösung des convoy-Problems für distributed-memory-Rechner bedarf einer verteilten Koordinierung von tasks, was eine essentielle Aufgabe beim Design von Schedulern für verteilte Betriebssysteme darstellt.

Global-memory-Rechner benötigen eine aufwendigere, kompliziertere Hardware als distributed-memory-Rechner; dies bedeutet für global-memory-Rechner einen zeitlich größeren Entwicklungsaufwand. Wenn das Preisleistungsverhältnis (MFLOPS/\$) wichtiger ist als die absolute Leistung, dann ergibt sich aus dem Hardware-Aufwand ein weiterer Vorteil für distributed-memory-Rechner. Das Preisleistungsverhältnis fällt für global-memory-Rechner geringer aus, d.h. bei gegebenem Preis hat ein global-memory-Rechner eine geringere Spitzenleistung. Dabei ist jedoch zu beachten, daß die Spitzenleistung insbesondere beim Vergleich von global-memory-Rechnern mit distributed-memory-Rechnern eine weitgehend aussagelose Größe ist; auch mit besonders geeigneten Anwendungsprogrammen wird auf distributed-memory-Rechnern im allgemeinen ein weitaus geringerer Prozentsatz der Spitzenleistung erreicht als auf global-memory-Rechnern.

Tab. 1 beschreibt die zweidimensionale Kombination der logischen Sicht des Programmiermodells und der physikalischen Sicht der Prozessor-Speicher-Anordnung. Hybride Ansätze aus logischer beziehungsweise physikalischer Sicht lassen sich durch Erweiterung der Tabelle einbeziehen, sollen jedoch in diesem Zusammenhang nicht weiter betrachtet werden. Die Einordnung der Rechnermodelle *global shared memory*, distributed memory message passing und virtual port memory ist direkt und eindeutig, da innerhalb der jeweiligen Zuordnungsfelder der Tabelle keine weiteren Modelle existieren.

#### Global Shared Memory (GSM):

Die Kombination physikalisch global / logisch shared beschreibt das global-shared-memory-Modell; auf einer UMA-Hardware wird das shared-memory-

| physikalisch<br>logisch | global memory              | distributed memory                                                                               |

|-------------------------|----------------------------|--------------------------------------------------------------------------------------------------|

| shared<br>memory        | global shared memory (GSM) | distributed shared memory (DSM) virtual shared memory (VSM) compiler-bridged shared memory (CSM) |

| message<br>passing      | virtual port memory        | distributed memory message passing (DMP)                                                         |

Tab. 1. Eine Einordnung von Rechnermodellen bezüglich Programmiermodell (logisch) und Prozessor-Speicher-Anordnung (physikalisch) nach Johnson [Joh88]

Programmiermodell unterstützt. Dieses klassische Parallelrechnermodell ist z.B. in den Rechnern Cray X-MP, Cray Y-MP und IBM 3090 realisiert<sup>2</sup> [Com89].

#### Distributed memory Message Passing (DMP):

Die Kombination physikalisch distributed / logisch message passing ist in NORMA-Rechnern realisiert, die nach dem message-passing-Programmiermodell arbeiten. Das distributed-memory-message-passing-Modell stellt die einfachste Implementierung eines Programmiermodells auf einem Rechner mit physikalisch verteiltem Speicher dar und ist auf den meisten Rechnern dieses Typs implementiert (z.B. Intel Paragon [Int91] und nCUBE [Pal88]).

#### Virtual Port Memory:

Das Modell des *virtual port memory* [Joh87, Ols85] realisiert ein *message-passing*-Programmiermodell auf Rechnern mit physikalisch globalem Speicher. Das *virtual-port-memory*-Modell wird hier nicht weiter betrachtet.

Für die Kombination physikalisch distributed / logisch shared existiert eine Reihe von verwandten Ansätzen, die das shared-memory-Programmiermodell auf Rechnern mit verteiltem Speicher implementieren. Da sich die Ansätze zum Teil durch die Abbildung des shared memory auf den verteilten Speicher unterscheiden, läßt sich diesbezüglich eine weitere Aufteilung der Rechnermodelle vornehmen. Bei der Formulierung der Definitionen für die Rechnermodelle distributed shared memory (DSM), virtual shared memory (VSM) und compiler-bridged shared memory (CSM) wurde versucht, alle heute existierenden Ansätze einzubeziehen.

#### Distributed Shared Memory (DSM):

Bei diesem Modell hat jeder Prozessor direkten Zugriff auf alle Speichermodule, die Zugriffszeiten unterscheiden sich jedoch für den Zugriff auf verschiedene Module zum Teil erheblich; die zugrundeliegende Hardware entspricht der NUMA-Architektur, die z.B. mit dem Rechner BBN TC2000 kommerziell verfügbar ist [BBN90]. Beim *distributed-shared-memory*-Modell kann auf jede Referenz einzeln zugegriffen werden (feingranularer Zugriff).

#### • Virtual Shared Memory (VSM):

Das virtual-shared-memory-Modell kann auf NUMA- oder auf NORMA-Architekturen implementiert werden. Bei NUMA-Architekturen wird mittels des virtual shared memory der Zugriff auf nicht-lokale Daten im Unterschied zum distributed shared memory Seiten-orientiert (grobgranular) durchgeführt. Bei NORMA-Architekturen können die Prozessoren nur mithilfe von Messages kommunizieren; ein direkter Zugriff auf Speichermodule anderer Prozessoren ist nicht möglich. Nicht-lokale Zugriffe werden mithilfe von Messages realisiert und erfolgen ebenfalls Seiten-orientiert (grobgranular). Ein entscheidender Unterschied zwischen DSM und VSM besteht in der Datenhaltung. Im Gegensatz zum DSM, wo jedes Datum genau einmal existiert, können beim VSM zeitweise mehrere gültige Kopien

Die lokalen Speicher, d.h. die Register der Cray und die *Cache*-Speicher der IBM, werden als temporäre Zwischenspeicher benutzt und sind für diese Betrachtung irrelevant.

einer Seite existieren; in diesem Zusammenhang ist beim VSM-Modell die Kohärenz des Adreßraums ein wesentliches Problem (siehe Kapitel 3).

#### Compiler-bridged Shared Memory (CSM):

Das Programmiermodell des *compiler-bridged shared memory* basiert auf einem *shared memory*, das tatsächlich jedoch nur auf der Compiler-Ebene emuliert wird; Die Verbindung von physikalisch realem *distributed memory* und emuliertem *shared memory* wird vom Compiler erzeugt (*bridged*). Das CSM-Modell kann auf NORMA-Architekturen implementiert werden, bei denen die Prozessoren über *Messages* kommunizieren; der Compiler generiert *message-passing*-Sprachprimitive, die die Bereitstellung von nicht-lokalen Daten gewährleisten (z.B. *High Performance FORTRAN* [HPF93]).

Weder von den Konzepten global memory und distributed memory noch bei den Programmiermodellen shared memory und message passing, noch bei den beschriebenen Rechnermodellen gibt es ein Konzept beziehungsweise Modell, das in jeder Hinsicht zu favorisieren ist. Leistung und Programmierbarkeit, Preisleistungsverhältnis und Skalierbarkeit gehören zu den entscheidenden Bewertungskriterien, wobei die Rechnermodelle jeweils Kompromisse bezüglich zumindest einem dieser Kriterien eingehen. Darüber hinaus hängt die Favorisierung eines Modells aufgrund eines einzelnen Bewertungskriteriums stark von den jeweiligen Anwendungsprogrammen ab; so können z.B. die Leistung und Programmierbarkeit verschiedener Anwendungsprogramme jeweils verschiedene Modelle favorisieren.

#### 2.2. Konzepte der massiv-parallelen Programmierung

Heute existierende massiv-parallele Systeme haben einen physikalisch verteilten Speicher. Bei der Mehrzahl der Implementierungen ist das message-passing-Programmiermodell realisiert. Ein wesentlicher Nachteil des message passing liegt in der für viele Anwendungen sehr aufwendigen Programmierung. Die explizite Spezifikation der Kommunikation ist oft komplex und damit fehleranfällig. Ein weiteres Problem stellt die Untersuchung von verschiedenen Algorithmen dar. Da Zugriffe auf verteilte Datenstrukturen durch komplex verknüpfte Sequenzen von message-passing-Primitiven formuliert werden, ist die jeweilige Datenzerlegung eng mit der erzeugten Programmstruktur verbunden (hard wired algorithm). Die notwendigen Kommunikationsstrukturen sind für verschiedene Datenzerlegungen im allgemeinen völlig verschieden, was einen entscheidenden Mangel an Flexibilität für das Testen von alternativen Datenzerlegungen darstellt. Die Programmierung auf der niedrigen Ebene des message passing führt, durch die Inflexibilität beim Testen von Alternativen, paradoxerweise zu geringer Leistung sowie zu unnötiger Arbeit für den Programmierer. Ein weiterer wesentlicher Nachteil ist in vielen Anwendungen die Unbalanciertheit zwischen Kommunikations- und Rechenaufwand; dies ist der Grund für die oft nur geringe Effizienz, d.h. das Verhältnis von erzielter Leistung zur Spitzenleistung. Neben der aufwendigen, unkomfortablen Programmierung sind insbesondere die Leistungsprobleme dafür verantwortlich, daß dem message-passing-Modell und damit

den massiv-parallelen Rechnern bisher der Durchbruch gegenüber den *global-shared-memory*-Rechnern verwehrt ist.

Modelle zur Verbesserung der massiv-parallelen Programmierung orientieren sich an der Programmierbarkeit. Alle neueren Modelle basieren auf dem *shared-memory*-Programmiermodell. Neben der besseren Programmierbarkeit wird für alle Modelle die Leistung im Vergleich zu *message-passing*-Programmen entscheidend sein. Da bei diesen Modellen ein *shared memory* nur als *shared memory* mit erhöhten Zugriffszeiten für nicht-lokale Zugriffe und nicht als *global shared memory* existiert, sind für Programme mit geringer Datenlokalität erhebliche Leistungsverluste zu erwarten. Durch eine geeignete, z.B. explizit Benutzer-gesteuerte Kontrolle der Datenverteilung und der Lastbalancierung kann die Lokalität erhöht werden.

#### 2.2.1. Das DSM-Modell: Shared Memory auf einer NUMA-Architektur

Das distributed-shared-memory-Modell basiert auf einer direkten Abbildung des sharedmemory-Programmiermodells auf eine NUMA-Architektur: Der physikalisch verteilte Speicher - jeder Speichermodul ist einem Prozessor zugeordnet - ist global adressierbar, d.h. jeder Prozessor kann auf jede Speicherstelle direkt zugreifen. Im Unterschied zu Zugriffen auf den lokalen Speichermodul - der dem Prozessor zugeordnete Speichermodul - ist die Zugriffszeit für Zugriffe auf einen remote-Speichermodul - ein Speichermodul, der einem anderen Prozessor zugeordnet ist - zum Teil erheblich höher. Der Grund für die nicht einheitliche (non-uniform) Zugriffszeit ist in der Architektur zu finden: In einem BBN TC2000 Rechner zum Beispiel sind die Speichermodule über ein mehrstufiges Butterfly-Verbindungsnetzwerk mit den Prozessoren verbunden [BBN89]. Der Zugriff auf einen remote-Speichermodul erfolgt über das Netzwerk und erfordert eine erheblich höhere Zugriffszeit als ein lokaler Zugriff, der ohne das Netzwerk direkt ausgeführt wird. Um die Verzögerung aufgrund von remote-Datenzugriffen zu verringern, wird in NUMA-Rechnern wie dem BBN TC2000 oder der IBM ACE Multiprozessor-Workstation [GFF89] in jedem Prozessor ein eigener Cache-Speicher genutzt. In diesem Zusammenhang werden spezielle NUMA-Speichermanagement-Techniken verwendet [BFS89, DMK92].

Massiv-parallele DSM-Rechner sind mit dem BBN Butterfly I seit 1979 kommerziell verfügbar. Mit Nachfolgemodellen bis hin zum BBN TC2000 wurde das DSM-Modell in immer leistungsfähigeren Rechnern realisiert.

#### 2.2.2. Das CSM-Modell: Transformation von Shared-Memory-Programmen

Beim compiler-bridged-shared-memory-Modell erzeugt der Programmierer ein shared-memory-Programm. Die Grundidee besteht darin, daß der Compiler aufgrund von zusätzlichen Spezifikationen das shared-memory-Programm transformiert, so daß es auf einem Rechner mit verteiltem Speicher ausgeführt werden kann. Die zusätzlichen Spezifikationen bestehen im wesentlichen aus der Datenpartitionierung, d.h. aus der Zerlegung von Datenmengen und der Verteilung der Daten auf eine ebenfalls zu spezifizierende virtuelle oder physikalische Netzwerktopologie. Das shared-memory-Programm kann z.B. in ein message-passing-Programm transformiert werden: Dabei transformiert der

Compiler die globalen Datenzugriffe in lokale und nicht-lokale Zugriffe<sup>3</sup>; für nicht-lokale Zugriffe werden *message-passing*-Sprachprimitive generiert. Die Programmausführung erfolgt im *message-passing*-Betrieb.

Die existierenden Ansätze unterscheiden sich bezüglich der Datenzerlegung beziehungsweise -verteilung, die automatisch oder Benutzer-gesteuert sein kann. Das CSM-Modell ist seit 1987 in einer Vielzahl von Ansätzen untersucht und implementiert worden. In SUPERB [Ger89, ZBG88] ist die halbautomatische Parallelisierung von FORTRAN-Programmen für den SUPRENUM-Rechner [Gil88] implementiert worden: Aufgrund von Programmfluß- und Datenabhängigkeitsanalysen wird mit SUPERB eine interaktive Datenzerlegung durchgeführt, Daten und Schleifeniterationen werden auf die Knoten verteilt, und es wird die zur Auflösung von nicht-lokalen Referenzen notwendige Kommunikation eingefügt. Schwachpunkte dieses ersten Ansatzes eines CSM-Modells (keine automatische Datenpartitionierung, nur statische Datenverteilung) sind in nachfolgenden Ansätzen verbessert. In [KeZi89] wird ein dynamisches Schema für die Datenpartitionierung vorgeschlagen. Wie SUPERB sieht auch dieser Ansatz zunächst die Transformation von sequentiellen Programmen vor, d.h. mithilfe von Datenabhängigkeitsanalysen und automatischer Parallelisierung<sup>4</sup> werden sequentielle DO-Schleifen in Single-Program-Multiple-Data-Codesequenzen überführt [Kar87]. Die explizite Programmierung von parallelen Schleifen stellt diesbezüglich eine Erweiterung dar, die auch dann eine parallele Programmausführung ermöglichen soll, wenn für die Abhängigkeitsanalyse zur Ubersetzungszeit keine hinreichenden Informationen zur Verfügung stehen (Fortran D [Fox90], Kali [MeRo91]). Explizit parallele Schleifen können jedoch zu semantischen Problemen führen, die in den bestehenden Ansätzen noch ungelöst sind [Ger92c]. Eine mögliche Alternative zu explizit parallelen Schleifen besteht in einer Abhängigkeitsanalyse zur Laufzeit mit automatischer Parallelisierung.

In Fortran D und Vienna FORTRAN [CMZ92] werden Datenzerlegung und -verteilung durch die Möglichkeit einer relativen Datenanordnung (data alignment), d.h. der Anordnung von Datenfeldern relativ zur Verteilung eines anderen Datenfeldes, ergänzt. In FORTRAN D werden die Datenzerlegung und die Datenanordnung von der Datenverteilung getrennt. Dadurch kann das Problem-Mapping (Datenzerlegung und -anordnung) maschinenunabhängig durchgeführt werden. Maschinenabhängigkeiten können im zweiten Schritt beim Maschinen-Mapping (Datenverteilung auf die Prozessoren) getrennt behandelt werden. Sowohl die Datenverteilung als auch die Datenanordnung sind dynamisch.

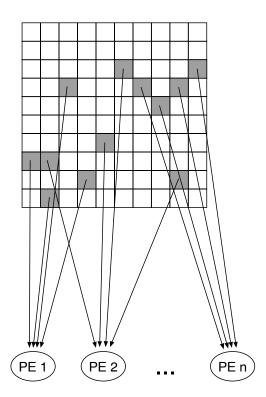

Bei einigen Ansätzen verteilt der Compiler die Iterationen von parallelen Schleifen (FORTRAN D, Kali, ARF [KMSB90]); dabei werden *message-passing-*Sprachprimitive so eingefügt, daß auch nicht-lokale Daten vor der Ausführung der entsprechenden Iterationen bereitstehen. Es werden Kommunikationstupel (in(p,q)- beziehungsweise out(p,q)-Tupel) verwendet, die angeben, welche Daten dem Prozessor p gehören und von Prozessor q benötigt werden. Aufgrund der Kommunikationstupel sendet ein Prozessor alle ihm zugeordneten *Messages*, führt die Iterationen mit ausschließlich lokalen Daten-

Dies gilt nicht für alle Realisationen.

Vergleichbare Programmierumgebungen zur automatischen Parallelisierung wurden auch für global-sharedmemory-Rechner entwickelt, z.B. im Rahmen von ParaScope [KMT91].

zugriffen aus, empfängt seine *Messages* und führt schließlich die übrigen Iterationen aus. Die Kommunikationstupel können zur Übersetzungszeit oder zur Laufzeit ermittelt werden. Zur Übersetzungszeit kann die Analyse nur dann durchgeführt werden, wenn hinreichend detaillierte Informationen bereits vorliegen (z.B. über die Verteilung der benötigten Datenstrukturen). In einigen Fällen können die Kommunikationstupel erst durch eine Laufzeit-Analyse bestimmt werden; wenn z.B. die Indizes der benötigten Feldelemente von Variablen abhängen, die erst zur Laufzeit bestimmt werden, ist die Analyse zur Übersetzungszeit nicht möglich. In solchen Fällen kann mithilfe des *inspector-/executor-*Konzepts [MSMB90] eine Bestimmung der Kommunikationstupel zur Laufzeit erfolgen. Der *inspector* führt eine modifizierte Version der parallelen Schleife aus, d.h. er erzeugt eine Liste nicht-lokaler Referenzen, aus denen die Tupel ermittelt werden. In einer anschließenden Kommunikationsphase werden die Tupel an die jeweiligen Prozessoren geschickt. Der *executor* führt nach der Kommunikationsphase die originale parallele Schleife aus.

In bestimmten Fällen können die Kommunikationstupel zur Übersetzungszeit bereits symbolisch bestimmt werden, zur Laufzeit müssen dann lediglich geschlossene Ausdrücke evaluiert werden; häufig muß jedoch aufgrund von nicht vorliegenden Informationen die gesamte Bestimmung der Tupel zur Laufzeit erfolgen.

Für die Laufzeit-Analyse ist die Effizienz bezüglich der Programmbeschleunigung aufgrund des zusätzlichen Overheads nicht a priori sichergestellt. In vielen Fällen ändern sich die Variablen bei der Ermittlung der Kommunikationstupel nur selten und können bei wiederholter Schleifenausführung wiederverwendet werden; auf diese Weise kann die Effizienz der Laufzeit-Analyse gesteigert werden [KMR90]. In der funktionalen Sprache Id Nouveau [ANP86, RoPi89] wird keine Wiederverwendung der Kommunikationstupel betrachtet, und die Laufzeit-Analyse wird als ineffizient bezeichnet.

Eine wesentliche Neuerung stellt die automatische Datenzerlegung dar (Crystal [LiCh90a], ASPAR [IFKF90]). In ASPAR generiert der Compiler automatisch die Datenzerlegung und Kommunikation für FORTRAN-Programme mit Block-Verteilung; eine automatische Parallelisierung für irreguläre Verteilungen ist jedoch nicht vorgesehen. Mit Erfahrungen aus den bisherigen Ansätzen hat sich das *High Performance FORTRAN Forum* zusammengefunden, um aufbauend auf dem FORTRAN-90-Standard Spracherweiterungen zu definieren, die einen Standard für eine datenparallele Programmierung darstellen sollen [HPF93]. Die Version 1.0 des *High Performance FORTRAN* spezifiziert viele der oben beschriebenen Techniken; darüber hinaus sind weitere Techniken Gegenstand aktueller Entwicklungen.

Im Bereich *compiler-bridged shared memory* gibt es zur Zeit eine Vielzahl an Aktivitäten. Die Entwicklung neuer Compiler-Techniken zur verbesserten Abhängigkeitsanalyse, die verbesserte Behandlung von Laufzeitabhängigkeiten in Schleifen, z.B. durch Laufzeit-Präprozessing, die Weiterentwicklung der automatischen Datenzerlegung sowie die Einbindung in interaktive Programmierumgebungen mit Leistungsvorhersagen für die Datenpartitionierung gehören zu den aktuellen Entwicklungen im Bereich *compiler-bridged shared memory*.

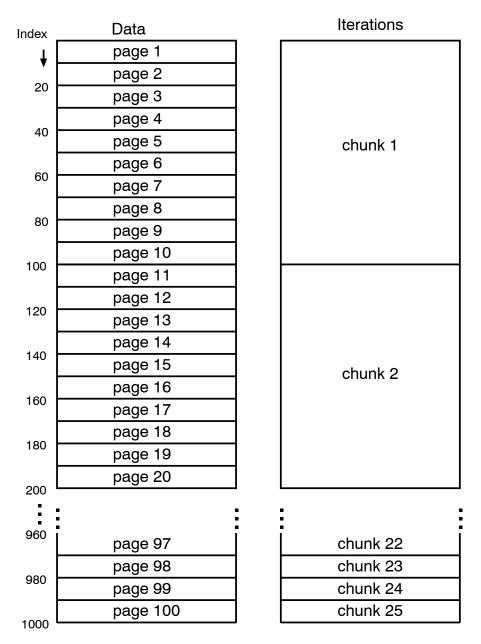

#### 2.2.3. Das VSM-Modell: Globaler Adreßraum durch Demand Paging

In einem virtual-shared-memory-System wird ein globaler Adreßraum auf die lokalen Speichermodule eines distributed-memory-Rechners abgebildet. Der lokale Speicher eines Prozessors wird als Cache-Speicher aufgefaßt, so daß sich der gesamte Speicher ausschließlich aus Cache-Speichern zusammensetzt. Die Daten werden in Gruppen oder Seiten (pages) zusammengefaßt, die auf Anfrage zwischen den lokalen Speichern der Prozessorelemente transferiert werden können (demand paging). Ähnlich wie in multicache-Systemen [Len90] können entsprechend dem Prinzip der Datenreplikation zeitweise mehrere gültige Kopien einer Seite existieren. Ein wesentliches Problem besteht darin, den virtual-shared-memory-Adreßraum kohärent zu halten: Der aus einer Leseoperation resultierende Wert muß immer mit dem jeweils zuletzt auf diese Adresse geschriebenen Wert übereinstimmen. Mögliche Lösungen zum Kohärenzproblem sowie eine ausführliche Beschreibung des VSM-Modells finden sich in Kapitel 3.

Das Modell des virtual shared memory ist in verschiedenartigen Ansätzen mit unterschiedlicher Motivation implementiert worden. Das System IVY realisiert ein virtual shared memory für ein Netzwerk von Workstations [Li86, Li88]. In Shiva wird mit den für IVY entwickelten Algorithmen ein VSM-System auf einem Intel iPSC/2 Hypercube implementiert [LiSc89a, LiSc89b]. Beide Ansätze sind auf Benutzerebene außerhalb des Betriebssystems implementiert und untersuchen alternative Algorithmen sowie die Effektivität des virtual shared memory. Mit KOAN wird der in Shiva gemachte Ansatz auf der Betriebssystemebene des iPSC/2-Systems implementiert [LaPr91]. Leistungsmessungen aufgrund von Anwendungsprogrammen zeigen die Effizienz des virtual shared memory; ein Vergleich mit Leistungsmessungen für entsprechende Anwendungsprogramme im message-passing-Betrieb auf dem gleichen Rechner führt zu ähnlichen Speedup-Werten [PrLa92] beziehungsweise zu einer Erhöhung der Speedup-Werte bei KOAN [LaPr91]<sup>3</sup>. Wie in allen Rechnern mit verteiltem Speicher ist auch in VSM-Rechnern die Lokalität der Daten von entscheidender Bedeutung für die Effizienz. Geeignete Algorithmen und Mechanismen zur Verbesserung der Datenlokalität hängen von der konkreten Struktur der Anwendungen ab. Eine Anpassung an die Struktur einer Anwendung wird in Munin und Mirage versucht [BCZ90a, FIPo89]. In Munin werden verschiedene Kohärenzmechanismen angewandt, die eine adaptive, typspezifische Kohärenz implementieren. In Mirage wird ein Tuning-Parameter verwendet, der dynamisch in Abhängigkeit vom Programmverhalten erhebliche Auswirkungen auf spezifische Anwendungen als auch auf den Systemdurchsatz haben kann.

Eine wesentliche Erweiterung bezüglich der zugrundeliegenden Hardware stellt PLATINUM dar [CoFo89]; während allen bisher genannten Ansätzen eine NORMA-Architektur zugrunde liegt, ist PLATINUM auf einer NUMA-Architektur implementiert. Die Ausnutzung des bei einer NUMA-Architektur möglichen Zugriffs auf einen nichtlokalen Speichermodul erweist sich in einigen Situationen als sinnvolle Ergänzung zum *paging*.

Mit dem Design der Data Diffusion Machine wird eine spezielle virtual-shared-memory-

Eine Erhöhung der Speedup-Werte von O(log n) auf O(n) wurde für einen Ray-Tracing-Algorithmus gemessen, für den die gleichzeitige Gewährleistung von Lastbalancierung und geeigneter Datenverteilung bei der Datenorientierten *message-passing-*Parallelisierung nicht gelöst werden konnte.

Hardware auf der Basis eines hierarchischen Bussystems vorgestellt [HaHa89].

Während die bisher betrachteten Ansätze als Forschungsprojekte entstanden sind, sollen Mach und Chorus als Grundlage für verteilte Netzwerk-Betriebssysteme dienen, zu denen auch kommerzielle Produkte zählen [You87, Roz88]. Mach ist als Kern eines verteilten Netzwerk-Betriebssystems implementiert, das den Betrieb von Einund Mehrprozessorrechnern in einem Netz mit einheitlichem Zugriff auf alle Daten erlaubt. Eine auf dem Mach-Kern aufbauende *virtual-shared-memory*-Implementierung ist z.B. PLATINUM (siehe oben). Auch MaX-SVM basiert auf Mach und ist auf der Benutzerebene implementiert [Moh93].

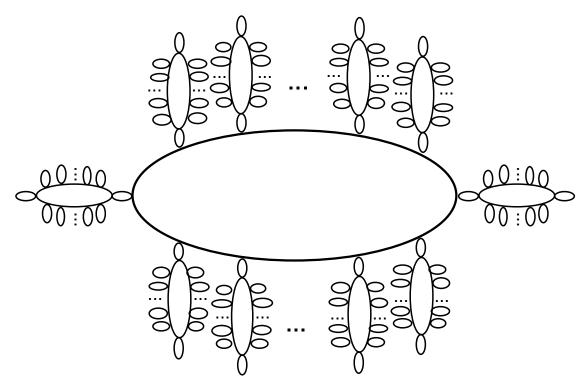

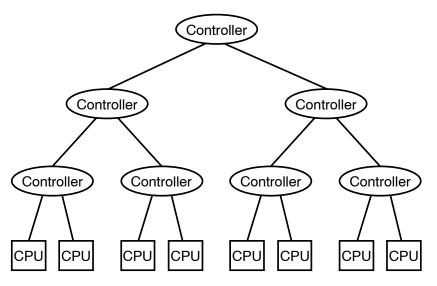

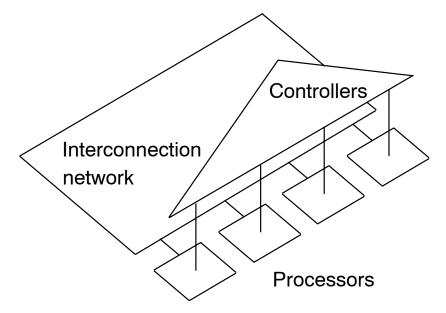

Die bisher einzig kommerziell verfügbaren *virtual-shared-memory*-Rechner wurden von den Firmen Myrias, Kendall Square und Cray entwickelt [BBZ88, Dun92, RSRM93, KeSc93, PMM93]. Der SPS-2-Rechner der Firma Myrias ist ein Mikroprozessorbasiertes System, das physikalisch in einer Baumstruktur realisiert ist. Der KSR 1 von Kendall Square nutzt RISC-Prozessoren, die über ein hierarchisches 2-Ebenen-Netzwerk von Ringen verbunden sind. Als erster massiv-paralleler Rechner der Firma Cray stellt der Cray T3D die derzeit aktuellste Realisierung in diesem Bereich dar. Die Hardware wird durch den Alpha-Prozessor der Firma DEC und eine dreidimensionale Torusstruktur für das Verbindungsnetzwerk charakterisiert, und das *virtual-shared-memory*-Modell realisiert vergleichsweise kleine Seiten und das Konzept der schwachen Kohärenz.

#### 3. Virtual Shared Memory

Das Modell des virtual shared memory (VSM) implementiert auf Rechnern mit verteiltem Speicher das komfortable Programmiermodell eines shared-memory-Rechners. Ein virtueller Adreßraum wird auf den lokalen Speicher aller Prozessoren verteilt. Die Daten werden in Gruppen oder Seiten (pages) zusammengefaßt und z.B. nach dem demand-paging-Verfahren verwaltet. In konventionellen demand-paging-Systemen werden, zur Realisation des virtuellen Speicherkonzepts, auf Anfrage Seiten zwischen Massenspeicher und Hauptspeicher transferiert. In dem hier beschriebenen VSM-Modell wird ein demand paging zwischen den lokalen Speichern der Prozessorelemente durchgeführt. Der Programmierer sieht dadurch nur einen globalen Adreßraum; so entsteht für ihn die Illusion, einen global-shared-memory-Rechner zu programmieren.

Geeignete Algorithmen zur Ablaufplanung in VSM-Rechnern hängen stark vom Speichermanagement in solchen Systemen ab. Abschnitt 3.1 gibt einen Überblick über das Speichermanagement existierender VSM-Ansätze, d.h. über Speicherzugriffsmodelle, Kohärenzstrategien und deren Implementierung, über verschiedene Strategien zum Speicher-Mapping und zur Speicher-Allokation sowie über die Seitenersetzung. Ausgewählte Mechanismen zur Prozeßverwaltung in VSM-Systemen werden in Abschnitt 3.2 vorgestellt.

#### 3.1. Speichermanagement in VSM-Systemen

In einem *virtual-shared-memory*-Adreßraum sind alle Daten von allen Prozessoren zugreifbar. Tatsächlich lokal verfügbar ist jedoch üblicherweise nur ein Teil der Daten. Das Auftreten einer Referenz auf eine lokal nicht vorhandene Adresse (inkohärente Referenz) erfordert die Auflösung dieser Referenz. Die Auflösung einer inkohärenten Referenz, die einen wesentlichen Teil der Kohärenzstrategie darstellt, unterscheidet sich bei VSM-Systemen im Vergleich zu klassischen *multicache-shared-memory*-Systemen. Ein klassisches *multicache*-System besteht meist aus einer relativ kleinen Anzahl von Prozessoren, die einen physikalisch globalen Speicher über ihren privaten *Cache* gemeinsam nutzen. In VSM-Systemen existiert kein physikalisch globaler Speicher; die als *Cache* genutzten lokalen Speicher sind relativ groß und erzeugen den gesamten VSM-Speicher.

#### 3.1.1. Speicherzugriffsmodelle

Das Speicherzugriffsmodell eines VSM-Ansatzes wird bestimmt durch die Abbildung des virtuellen Adreßraums auf den physikalischen Adreßraum (Speicher-Mapping) sowie durch den Zugriffsmechanismus. Die Einheit für das Mapping stellt dabei eine charakteristische Größe dar. Analog zum klassischen Konzept des virtuellen Speichers wird in vielen Ansätzen die Seite (page, segment, cache-line) als Einheit für das Mapping benutzt (Seiten-orientiertes Mapping [RSRM93, LaPr91, Li86]). Die Seite wird mit einem Status wie read-only oder read-write versehen, der das Zugriffsrecht spezifiziert (Seiten-orientierter Zugriff). In einigen Ansätzen wird das Mapping auf der Basis von Objekten durchgeführt (Objekt-orientiertes Mapping [BCZ90a, CoFo89, RaKh91]); der Begriff des Objekts bezeichnet logisch zusammenhängende Daten. Die Objekte werden

Virtual Shared Memory 17

in Seiten unterteilt, und das Zugriffsrecht wird wiederum auf Seitenebene spezifiziert (Seiten-orientierter Zugriff).

Als Beispiel für ein komplexes Speicherzugriffsmodell kann PLATINUM genannt werden [CoFo89]. Der PLATINUM-Ansatz ist auf einer NUMA-Architektur implementiert (BBN Butterfly Plus). Das traditionelle Konzept des virtuellen Speichers umfaßt drei Ebenen in der Speicherhierarchie: Den Cache, den einheitlich zugreifbaren Primärspeicher und den wesentlich langsameren Sekundärspeicher. Ein Charakteristikum des PLATINUM-Ansatzes besteht darin, daß aufgrund der NUMA-Architektur mit dem remote-Primärspeicher eine zusätzliche Ebene in der Speicherhierarchie existiert. Um die Anforderungen dieser zusätzlichen Ebene separat von denen des traditionellen Konzepts des virtuellen Speichers zu behandeln, wurde in PLATINUM ein 4-stufiges Speicherzugriffsmodell implementiert; das Modell besteht aus den virtuellen Adreßräumen, den Objekten, dem kohärenten Speicher und dem physikalischen Speicher. Alle Objekte innerhalb eines virtuellen Adreßraums sind shared-Objekte für alle threads in diesem Adreßraum (Objekt-orientiertes Mapping). Ein Objekt kann in mehrere virtuelle Adreßräume als zugreifbar abgebildet werden. Mit der Aufteilung der Objekte in Seiten wird ein Seiten-orientierter Zugriff realisiert. Der kohärente Speicher gewährleistet die Kohärenz des Mapping.

#### 3.1.2. Kohärenzstrategien

Ähnlich wie bei der Nutzung von Cache-Speichern in den Prozessoren von global-shared-memory-Rechnern (multicaches) wird auch beim VSM-Modell das Prinzip der mehrfachen Datenhaltung angewandt, es existieren zeitweise mehrere gültige Kopien einer Seite (Datenreplikation). Ein wesentliches Problem besteht darin, den VSM-Adreßraum zu jeder Zeit kohärent zu halten, d.h. der aus einer Leseoperation resultierende Wert muß immer mit dem jeweils zuletzt auf diese Adresse geschriebenen Wert übereinstimmen (strikte Kohärenz). Eine temporäre Einschränkung dieser Kohärenzforderung (schwache Kohärenz) erlaubt in bestimmten Situationen eine Erhöhung der Parallelität.

Die Menge der möglichen Zugriffsrechte auf eine Seite charakterisiert die Kohärenzstrategie. Im einfachsten Fall wird das Zugriffsrecht auf eine Seite mit *read-only* (Nur-Lese-Zugriff) oder *read-write* (Schreib-Lese-Zugriff) bestimmt. In komplexeren Modellen werden weitere Zugriffsrechte spezifiziert, um die Seitenverwaltung zu beschleunigen. Es wird z.B. unterschieden zwischen *read-only*-Seiten mit mehreren Kopien und *read-only*-Seiten mit nur einer Kopie [CoFo89]. Eine wesentliche Erweiterung der Zugriffsrechte wird in [RaKh91] vorgenommen: Mit *weak-read* kann eine Seite im nicht-exklusiven Zugriff gehalten werden, jedoch ohne Garantie, ob sich die Seite ändert. Auf diese Weise kann aufgrund der möglichen Zugriffsrechte die Kohärenzstrategie bestimmt werden, die strikt kohärent oder schwach kohärent sein kann.

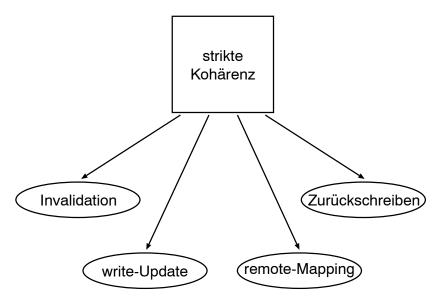

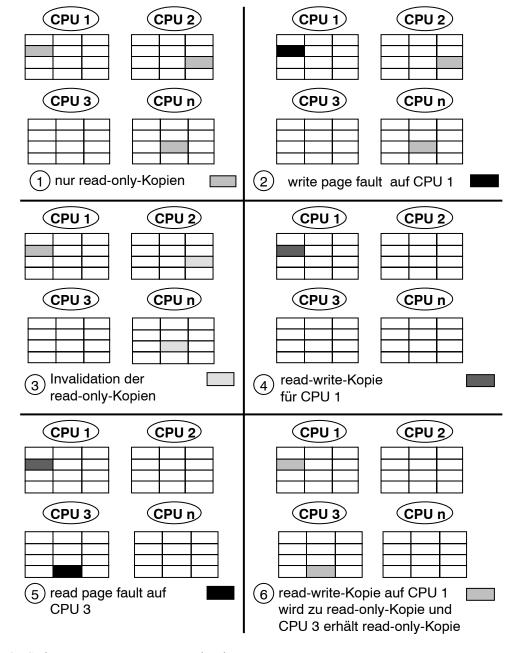

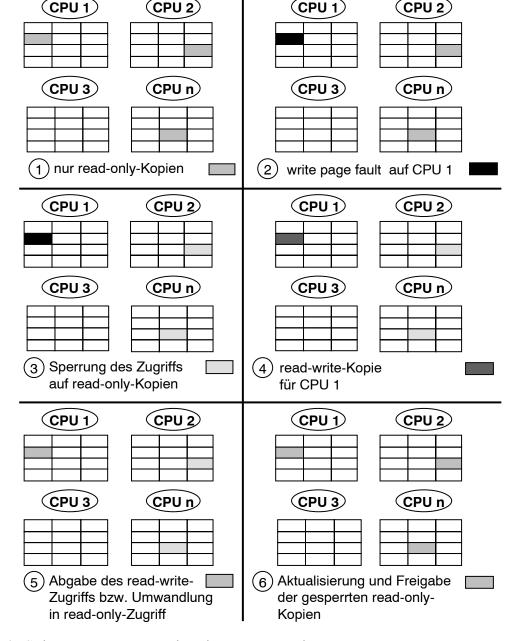

Die Strategie der strikten Kohärenz kann auf der Basis von Invalidationstechniken, durch Zurückschreiben (writeback), durch write-update und durch remote-Mapping realisiert werden (siehe Abb. 1). Beim Invalidationsansatz haben entweder mehrere Knoten read-only-Zugriff auf eine Seite, oder ein Knoten hat read-write-Zugriff. Will ein Knoten auf eine Seite zugreifen, für die er nicht das entsprechende Zugriffsrecht hat, so wird ein read

Abb. 1. Mechanismen der strikten Kohärenz

page fault oder ein write page fault ausgelöst. Bei einem write page fault werden alle Kopien der betroffenen Seite in Knoten mit read-only-Zugriff invalidiert (siehe Abb. 2). Nur der anfragende Knoten erhält eine gültige Kopie und read-write-Zugriff. Wird ein read page fault ausgelöst, dann wechselt das Zugriffsrecht des aktuell schreibberechtigten Knotens (falls existent) in read-only, und der anfragende Knoten erhält eine Kopie der Seite (Abb. 2: (5) und (6)). Die Invalidation beziehungsweise die Änderung des Zugriffsrechts für eine Seite kann mit drei unterschiedlichen Techniken erfolgen; es kann entweder ein individueller Prozessor, oder mittels multicast eine bestimmte Gruppe von Prozessoren angesprochen werden, oder es können mittels broadcast alle Prozessoren angesprochen werden. Die broadcast-Technik hat den Vorteil, daß keine Informationen über vorhandene Kopien der jeweiligen Seite (copy set) benötigt werden; für Systeme mit großer Prozessorzahl ist diese Lösung jedoch mit zuviel Overhead aufgrund der Vielzahl von Messages verbunden. Für große Systeme ist die Verwendung von copy sets in Verbindung mit der multicast-Technik effizienter.

Beim Zurückschreiben existieren nur Knoten mit *read-only-*Zugriff. Tritt ein *write page fault* auf, dann wird auf alle Kopien der Seite geschrieben. Da die beim Zurückschreiben notwendigen Aktualisierungen mit hohen Kommunikationskosten verbunden sind, erscheint dieser Ansatz ungeeignet für ein *distributed-memory-*System.

Mit der write-update-Technik (Abb. 3) wird bei einem write page fault der Zugriff auf die read-only-Kopien einer Seite nur vorübergehend gesperrt [GHSS91]. Der schreibende Prozeß gibt das read-write-Zugriffsrecht nach Beendigung aller Schreibzugriffe explizit ab (Abb. 3: (5)); danach werden die gesperrten read-only-Kopien aktualisiert und wieder für den Zugriff freigegeben. In Verbindung mit geeigneten Synchronisationsstrategien für mehrfache page faults kann mit dieser Technik der Kopier-Overhead auf Kosten von zusätzlichem message-passing-Overhead reduziert werden. Aufgrund von Untersuchungen in [GHSS91] hat sich die Invalidation in den meisten Fällen als effizienter erwiesen. Bei häufigem, feingranularem Schreibzugriff mehrerer Prozessoren auf unterschiedliche Daten auf derselben Seite treten beim Invalidationsansatz Effizienzprobleme auf; die

Virtual Shared Memory 19

Abb. 2. Strikte Kohärenz durch Invalidation

entsprechende Seite muß ständig invalidiert beziehungsweise zwischen den Prozessoren transferiert werden (page thrashing [Li86]). Mögliche Lösungsansätze sind neben der Strategie der schwachen Kohärenz (siehe unten) die Datenreorganisation und das remote-Mapping. Bei einer Reorganisation der Daten werden die von verschiedenen threads benutzten Daten auf verschiedenen Seiten angelegt; die geeignete Anordnung der Daten wird vom Benutzer oder vom Compiler spezifiziert. Das page thrashing stellt ein wesentliches Problem des VSM-Modells dar; diesbezüglich ist die geeignete, Seiten-orientierte Anordnung von Daten eine wesentliche Anforderung an Compiler für VSM-Systeme. Ein Nachteil dieser Vorgehensweise liegt in dem zusätzlich benötigten Speicherplatz, da bei einer Verteilung von kontinuierlichen Datenfeldern auf verschiedene Seiten im allgemeinen jeweils Teile der Seiten ungenutzt bleiben (Fragmentierung). Beim

Abb. 3. Strikte Kohärenz durch die write-update-Technik

CPU

CPU<sub>2</sub>

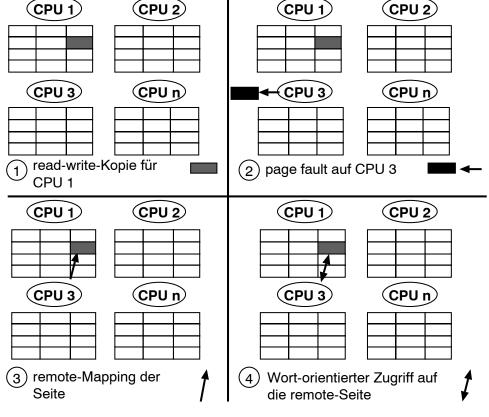

remote-Mapping (Abb. 4) wird anstatt der Replikation oder Migration einer Seite eine auf einem anderen (remote) Knoten existierende Kopie der Seite als zugreifbar abgebildet [CoFo89]; eine solche Seite entspricht einer non-cachable-Seite in multicache-sharedmemory-Systemen. Anstatt die Seite in den eigenen lokalen Speichermodul (bzw. Cache im multicache-System) zu laden und die gewünschten Daten zuzugreifen, erfolgt der Zugriff jeweils auf ein einzelnes Datum direkt im remote-Speichermodul (bzw. shared memory im multicache-System). Diese Technik ist besonders geeignet, wenn viele Prozessoren häufig feingranular schreibend auf die gleichen Daten zugreifen.

Grundsätzlich sind Kombinationen der beschriebenen Techniken zur Realisierung der Strategie der strikten Kohärenz möglich. Bei einer Kombination von Invalidation und Zurückschreiben kann in Abhängigkeit von der Anzahl existierender Kopien jeweils eine

Virtual Shared Memory 21

Abb. 4. Strikte Kohärenz durch remote-Mapping

der beiden Strategien angewandt werden. Bei der sogenannten selektiven Invalidation [CoFo89] ist eine Kombination von Invalidation und *remote*-Mapping implementiert. Dabei wird selektiv und dynamisch entschieden, welche der beiden Techniken genutzt wird. Die Invalidation und das Zurückschreiben können prinzipiell jeweils als eigenständige Implementierung eines VSM genutzt werden; die beiden Techniken *write-update* und *remote*-Mapping können nur in einer Kombination mit einer der beiden vorgenannten Techniken ein sinnvolles VSM implementieren.

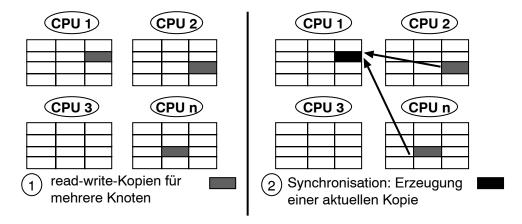

Die Idee der schwachen Kohärenz basiert auf einer temporären Einschränkung der Kohärenzforderung mit dem Ziel, die Parallelität zu erhöhen [BNR89, BoIs91, GHSS91, KVW87]. Nach der Strategie der schwachen Kohärenz arbeitet jeder Prozeß auf einer eigenen Kopie einer entsprechenden Seite; dabei kann jeder Prozeß auf Daten auf derselben Seite schreibend zugreifen, d.h. es existieren gleichzeitig mehrere *read-write-*Kopien einer Seite (Abb. 5). Die Erzeugung einer aktuellen Kopie einer solchen Seite erfolgt an Synchronisationspunkten, wo alle Kopien der Seite vereinigt werden *(merge)*.

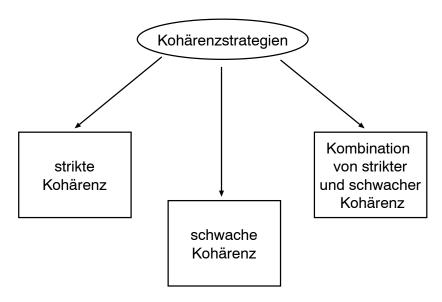

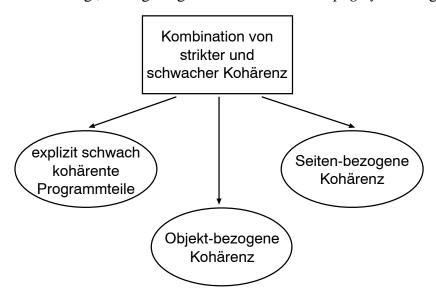

Eine Erweiterung der beiden Strategien (schwache Kohärenz und strikte Kohärenz) kann durch eine Kombination von strikt und schwach kohärenten Protokollen realisiert werden (Abb. 6, [BCZ90a, GHSS91, RaKh91]). In [GHSS91] wird dabei zunächst nach dem strikt kohärenten Protokoll verfahren; für Programmteile kann jedoch explizit das schwach kohärente Protokoll genutzt werden. Das Ende eines solchen Programmteils entspricht einem expliziten Synchronisationspunkt und veranlaßt die Vereinigung aller Kopien einer Seite und den Wiedereintritt in das strikt kohärente Protokoll.

Abb. 5. Die schwache Kohärenz

Ein komplexerer Ansatz für eine Kombination von strikt und schwach kohärenten Protokollen wird in Munin gemacht [BCZ90a]. Die implementierte typspezifische Kohärenzstrategie unterstützt verschiedene Kohärenzmechanismen (strikte und schwache Kohärenz) für verschiedene Objekttypen. Die implementierten Mechanismen sind Replikation, remote-Mapping (remote load store), Migration, verzögerte Aktualisierung (delayed update) und vorzeitige Bereitstellung von Objekten (eager object moving).

Bei der Replikation oder Vervielfältigung von Objekten (read-only und read-write) werden mehrere Kopien der Objekte in verschiedenen Knoten erzeugt. Bei der Änderung einer Kopie werden alle übrigen Kopien aktualisiert; die Aktualisierung kann mittels Invalidation oder Zurückschreiben erfolgen. Die Replikation verursacht geringe Verzögerungen für Lesezugriffe, da diese lokal erfolgen, Schreibzugriffe bedeuten jedoch große Verzögerungen aufgrund der Aktualisierung aller remote-Kopien. Beim remote-Mapping existiert nur eine remote-Kopie, so daß Schreibzugriffe nur eine Aktualisierung und damit eine relativ geringe Verzögerung verursachen. Lesezugriffe sind beim remote-Mapping dagegen relativ teuer, da jeder Lesezugriff ein remote-Zugriff ist. Für read-write-Daten

Abb. 6. Überblick über verschiedene Kohärenzstrategien

Virtual Shared Memory 23

kann in Abhängigkeit von der relativen Häufigkeit der Schreib- beziehungsweise Lesezugriffe jeweils einer der beiden Mechanismen überlegen sein. Bei der Migration wird jeweils die einzige existierende Kopie einer Seite migriert. Die verzögerte Aktualisierung ähnelt der in [GHSS91] beschriebenen Form der schwachen Kohärenz; die Aktualisierung von remote-Kopien modifizierter Datenobjekte kann verzögert werden, bis die remote-threads auf die entsprechenden Daten zugreifen wollen. Die verzögerte Aktualisierung kann z.B. bei gleichzeitigem Schreiben von zwei threads auf verschiedene Objekte auf der gleichen Seite angewendet werden. An einem geeigneten Synchronisationspunkt erfolgt die Erzeugung einer aktuellen Kopie der Seite (merge). Die vorzeitige Bereitstellung von Objekten entspricht einer Migration oder Replikation von Objekten ohne explizite Anforderung; im Idealfall stehen die Daten bereits zur Verfügung, bevor sie tatsächlich benötigt werden.

Zur Realisierung der typspezifischen Kohärenz sind 9 verschiedene Objekttypen definiert. Aufgrund von Benutzer-spezifizierten Informationen zum Objekttyp einer Datenstruktur wählt das Laufzeitsystem geeignete Kohärenzmechanismen für jedes Objekt. Geplant ist, daß diese Auswahl zur Laufzeit dynamisch erfolgt. In Tab. 2 sind die 9 Objekttypen mit dem jeweils geeigneten Kohärenzmechanismus angegeben.

Mit Clouds ist ein weiterer Ansatz einer Kombination von strikter und schwacher Kohärenz implementiert [RaKh91]. Im Unterschied zu Munin wird hier der Kohärenzmechanismus nicht auf das Objekt, sondern auf die Seite bezogen. Die beiden Zugriffsrechte read-only und read-write können in dieser Implementierung nur dann geändert werden,

| Objekttyp             | Beschreibung des Objekttyps                                                                                               | Kohärenz-<br>mechanismus                                      |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| write-once            | werden einmal geschrieben (Initialisierung) und danach nur noch gelesen                                                   | Replikation                                                   |

| private               | werden nur von einem thread zugegriffen                                                                                   | keine Kohärenz<br>erforderlich                                |

| write-many            | werden zwischen Synchronisationspunkten häufig von mehreren <i>threads</i> modifiziert                                    | Verzögerte<br>Aktualisierung                                  |

| result                | sammeln Ergebnisse, die einmal geschrieben und nur von einem <i>thread</i> gelesen werden                                 | Verzögerte<br>Aktualisierung                                  |

| synchronization       | wechselnder exklusiver Zugriff; Objekte wie z.B. <i>lock</i> und <i>monitor</i> , die zur Synchronisation benötigt werden | verteilte Synchronisation<br>mittels verteilter <i>locks</i>  |

| migratory             | werden phasenweise jeweils nur von einem <i>thread</i> zugegriffen                                                        | Migration                                                     |

| producer-<br>consumer | werden von einem <i>thread</i> geschrieben und von einer festen Gruppe von <i>threads</i> gelesen                         | Vorzeitige<br>Bereitstellung                                  |

| read-mostly           | werden signifikant öfter gelesen als geschrieben                                                                          | Replikation und remote-Mapping                                |

| general<br>read-write | alle anderen Objekte; read-write- und read-only-Zugriffe von mehreren threads                                             | Berkeley-Ownership-<br>Cache-Consistency-<br>Protocol [Kat85] |

Tab. 2. Typspezifische Kohärenz in Munin: Objekttypen und geeignete Kohärenzmechanismen

wenn der jeweils berechtigte Knoten sein Zugriffsrecht auf die Seite explizit aufgibt. Als weitere Zugriffsrechte sind *weak-read* (nicht exklusiver *read-only-*Zugriff ohne Garantie, daß sich die Seite nicht ändert) und *none* (exklusiver *read-write-*Zugriff ohne Garantie, daß die Seite nicht abgegeben werden muß) implementiert. In Abb. 7 sind die beschriebenen Möglichkeiten der Kombination von strikter und schwacher Kohärenz dargestellt.

#### 3.1.3. Implementierung von Kohärenzstrategien

Neben den konzeptionellen Unterschieden für die Kohärenzstrategien kann die Implementierung einer Kohärenzstrategie auf verschiedene Arten erfolgen und damit ein weiteres wesentliches Charakteristikum verschiedener VSM-Ansätze darstellen. Eine Kohärenzstrategie kann Software-basiert mithilfe von Handler- und Server-Techniken [BCZ90a, LaPr91, Li86, LiSc89a] oder aber Hardware-basiert implementiert werden [KSR92]. Während eine Hardware-basierte Implementierung möglicherweise physikalische Geschwindigkeitsvorteile einbringt, kann mithilfe einer Software-basierten Implementierung ein höheres Maß an Flexibilität erreicht werden. Wie in Munin können so z.B. Objekte entspechend ihrer Zugriffscharakteristik mit geeigneten Kohärenzmechanismen behandelt werden. Es kann sowohl mit variabler Seitengröße als auch mit dynamischen Entscheidungen für geeignete Kohärenzmechanismen gearbeitet werden.

Ein wesentliches Charakteristikum der Implementierung zeigt sich auch in der zugrundeliegenden Hardware-Architektur. So hat z.B. das *remote*-Mapping auf einer NUMA-Architektur (PLATINUM [CoFo89]) entscheidende Geschwindigkeitsvorteile gegenüber dem *remote*-Mapping auf einer NORMA-Architektur (Munin [BCZ90a]). Im folgenden werden Software- und Hardware-basierte Implementierungen näher untersucht.

#### 3.1.3.1 Software-Mechanismen: Page-Fault-Handler und -Server

In allen beschriebenen Speicherzugriffsmodellen wird mit Seiten-orientiertem Zugriff gearbeitet, d.h. bei der Auflösung einer inkohärenten Referenz wird die gesamte Seite, in der die Referenz liegt, verfügbar gemacht. Es wird ein *page fault* ausgelöst, was

Abb. 7. Die Kombination von strikter und schwacher Kohärenz

Virtual Shared Memory 25

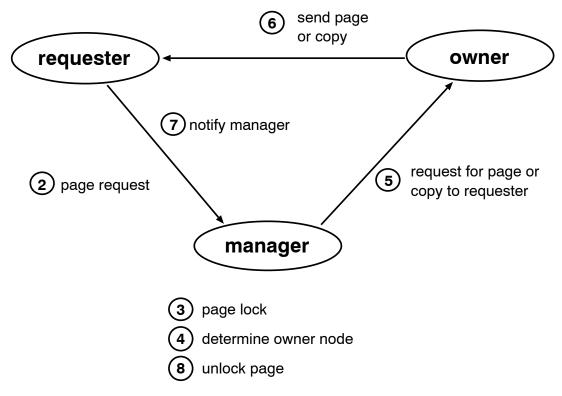

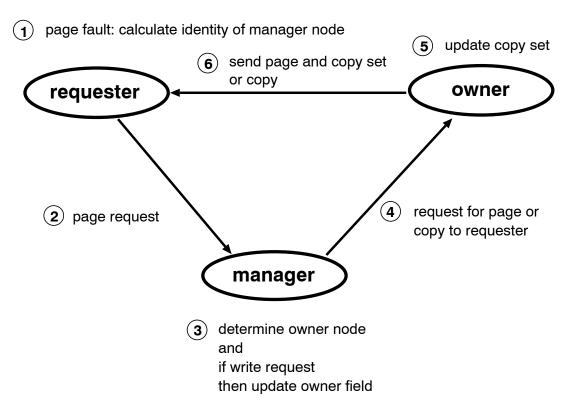

eine Unterbrechung des auslösenden Prozesses und eine Aktivierung geeigneter pagefault-Handler und -Server bewirkt. In IVY [Li86] erzeugt der Handler im Prozessor mit dem page fault eine Anfrage für einen entsprechenden Zugriff auf die Seite (readonly oder read-write), der Server im Prozessor mit der gesuchten Seite bearbeitet die Anfrage und macht die Seite verfügbar. Die Handler und Server implementieren die Kohärenzstrategie. Verschiedene Algorithmen sind in [Li86, LiHu89] untersucht worden und in zum Teil abgewandelter oder erweiterter Form auch in anderen Ansätzen implementiert [GHSS91, LaPr91, LiSc89b]. Im folgenden werden drei Algorithmen betrachtet, der zentrale-Manager-Algorithmus (centralized manager algorithm), der statischverteilte-Manager-Algorithmus (fixed distributed manager algorithm) und der dynamischverteilte-Manager-Algorithmus (dynamic distributed manager algorithm). Bei allen drei Algorithmen gibt es jeweils einen Besitzer für jede Seite, der jedoch dynamisch wechseln kann (dynamic page ownership); der Besitzer einer Seite verfügt über eine aktuelle Kopie der Seite. Eine wesentliche Aufgabe der Manager besteht in der Verwaltung der Informationen über die aktuellen Besitzer der Seiten (ownership information). Für jede Seite werden außer dem Besitzer das Zugriffsrecht, das copy set (spezifiziert alle Prozessoren mit einer gültigen read-only-Kopie der Seite) und Synchronisationsvariablen (*lock*-Variablen) gespeichert.

Beim zentralen-Manager-Algorithmus verwaltet ein zentraler Manager auf einem einzelnen Prozessor alle Informationen über die aktuellen Besitzer aller Seiten. Bei einem page fault fragt der jeweilige Prozessor den Manager nach einer Kopie der entsprechenden Seite; der Manager gibt die Anfrage an den jeweiligen Besitzer der Seite weiter. Beim statisch-verteilten-Manager-Algorithmus verwaltet jeder Prozessor eine vorbestimmte Menge von Seiten, d.h. es gibt einen Manager auf jedem Prozessor; die jeweilige Menge von Seiten wird durch eine Mapping-Funktion H bestimmt. Bei einem page fault fragt der jeweilige Prozessor den Prozessor H(p) (Manager) nach dem Besitzer der Seite, der Manager leitet die Anfrage weiter.

Beim dynamisch-verteilten-Manager-Algorithmus ist der Manager jeder Seite dynamisch verteilt: Neben den oben genannten Einträgen speichert jeder Prozessor Informationen über die Besitzer aller Seiten in seiner lokalen Seitentabelle; die Variable *probOwner* spezifiziert entweder den tatsächlichen Besitzer oder den wahrscheinlichen Besitzer einer Seite. Enthält der Eintrag nicht die Adresse des tatsächlichen Besitzers, so wird mithilfe des wahrscheinlichen Besitzers der Anfang einer Sequenz von Prozessoren gefunden, die schließlich zum tatsächlichen Besitzer führt. Bei der Initialisierung wird die Variable *probOwner* auf einen Default-Wert gesetzt, der den initialen Besitzer aller Seiten anzeigt. Zur Laufzeit wird die Variable *probOwner* einer Seite aktualisiert, wenn der Prozessor eine Invalidationsanfrage erhält, wenn der Prozessor den Besitz der Seite abgibt oder wenn der Prozessor eine *page-fault*-Anfrage weiterleitet.

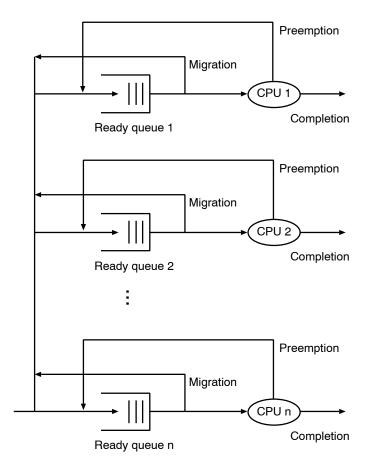

In [LiHu89] wurden die drei genannten Algorithmen bezüglich ihrer Leistung gegenübergestellt. Da der zentrale Manager beim Auftreten vieler *page faults* einen Engpaß (bottleneck) darstellt, sind die verteilten Manager für massiv-parallele Systeme besser geeignet. Der statisch-verteilte-Manager-Algorithmus benötigt zwei Messages für die Mitteilung einer Seitenanfrage an den Besitzer (Abb. 8: (2) page request und (5) request for page or copy to requester). Beim dynamisch-verteilten-Manager-Algorithmus entfällt

1 page fault: calculate identity of manager node

Abb. 8. Der statisch-verteilte-Manager-Algorithmus

im Vergleich dazu die *Message* an den Manager. Im Idealfall, d.h. wenn der Inhalt des Feldes *probOwner* den tatsächlichen Besitzer anzeigt (diese Voraussetzung wird in den Untersuchungen in [LiHu89] erfüllt), wird anstelle von zwei *Messages* nur eine *Message* für die Mitteilung der Seitenanfrage an den Besitzer benötigt. In den beschriebenen Untersuchungen ist der dynamisch-verteilte-Manager-Algorithmus dem statisch-verteilten-Manager-Algorithmus deutlich überlegen.

Weitere Software-basierte VSM-Ansätze sind ebenfalls durch Handler und Server implementiert. In Munin prüft der Server den Objekttyp und aktiviert einen dem Objekttyp entsprechenden Handler [BCZ90a]. Auf diese Weise wird mittels unterschiedlicher Handler eine adaptive Kohärenzstrategie implementiert. Das PLATINUM-System [CoFo89] implementiert den zusätzlichen Mechanismus des *remote*-Mapping (siehe Abschnitt 3.1.2): Für die *page-fault*-Handler steht eine Historie von Invalidationen für jede Seite zur Verfügung; aufgrund der Historie entscheidet der Handler z.B. bei einem *read page fault*, ob eine Replikation oder ein *remote*-Mapping vorgenommen wird.