## Reduction of skin effect losses in double-level-T-gate structure

M. Mikulics, H. Hardtdegen, Y. C. Arango, R. Adam, A. Fox, D. Grützmacher, D. Gregušová, S. Stanček, J. Novák, P. Kordoš, Z. Sofer, L. Juul, and M. Marso

Citation: Applied Physics Letters 105, 232102 (2014); doi: 10.1063/1.4903468

View online: http://dx.doi.org/10.1063/1.4903468

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/105/23?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Electrical and structural degradation of GaN high electron mobility transistors under high-power and high-temperature Direct Current stress

J. Appl. Phys. 117, 025707 (2015); 10.1063/1.4905677

Fixed interface charges between AlGaN barrier and gate stack composed of in situ grown SiN and Al2O3 in AlGaN/GaN high electron mobility transistors with normally off capability

Appl. Phys. Lett. 104, 113502 (2014); 10.1063/1.4868531

Effect of electron irradiation on AlGaN/GaN and InAlN/GaN heterojunctions

J. Vac. Sci. Technol. B 31, 022206 (2013); 10.1116/1.4795210

Effect of substrate-induced strain in the transport properties of AlGaN/GaN heterostructures

J. Appl. Phys. 108, 023707 (2010); 10.1063/1.3463150

Modeling of the reverse gate leakage in AlGaN/GaN high electron mobility transistors

J. Appl. Phys. 107, 064501 (2010); 10.1063/1.3340826

## Reduction of skin effect losses in double-level-T-gate structure

M. Mikulics, <sup>1,2,a)</sup> H. Hardtdegen, <sup>1,2</sup> Y. C. Arango, <sup>1,2</sup> R. Adam, <sup>1,2</sup> A. Fox, <sup>1,2</sup> D. Grützmacher, <sup>1,2</sup> D. Gregušová, <sup>3</sup> S. Stanček, <sup>4</sup> J. Novák, <sup>3</sup> P. Kordoš, <sup>5</sup> Z. Sofer, <sup>6</sup> L. Juul, <sup>7</sup> and M. Marso, <sup>7</sup>

<sup>1</sup>Peter Grünberg Institute (PGI-9), Forschungszentrum Jülich, D-52425 Jülich, Germany

Institute of Electrical Engineering, Slovak Academy of Sciences, SK-84104 Bratislava, Slovak Republic

(Received 23 September 2014; accepted 18 November 2014; published online 8 December 2014)

We developed a T-gate technology based on selective wet etching yielding 200 nm wide T-gate structures used for fabrication of High Electron Mobility Transistors (HEMT). Major advantages of our process are the use of only standard photolithographic process and the ability to generate T-gate stacks. A HEMT fabricated on AlGaN/GaN/sapphire with gate length  $L_g = 200 \, \text{nm}$  and double-stacked T-gates exhibits 60 GHz cutoff frequency showing ten-fold improvement compared to 6 GHz for the same device with 2  $\mu$ m gate length. HEMTs with a double-level-T-gate (DLTG) structure exhibit up to 35% improvement of  $f_{max}$  value compared to a single T-gate device. This indicates a significant reduction of skin effect losses in DLTG structure compared to its standard T-gate counterpart. These results agree with the theoretical predictions. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4903468]

During the last three decades, the fabrication and performance of transistors operating in the GHz frequency range have been showing a rapid progress by introducing new material systems (e.g., GaAs/InGaAs<sup>1-4</sup> or AlGaN/GaN heterostructures<sup>5–7</sup>), novel technological processes,<sup>6–9</sup> or new device geometries with decreasing gate dimensions. 10-12 The transistor scaling process has the drawback that the parasitic gate resistance increases linearly with decreasing gate length L<sub>g</sub>. A small gate length is crucial for the transistor speed; however, the increase of the gate resistance degrades the external device properties, especially the power gain. Therefore, the parasitic gate resistance must be kept as low as possible with decreasing L<sub>g</sub>. One solution for the contradictory requirements is to use T-shaped gates allowing fabricating gates with small  $L_{\sigma}$  (corresponding to the base of T) with a low value of R<sub>g</sub>, due to the large top of the T. The larger the head, the lower the resistance. The major research effort to provide these T-shaped gates concentrates on structures fabricated by electron beam lithography, deep UV lithography, or nano-imprint techniques. 13 Especially, the fabrication of T-shaped gates by e-beam lithography is commonly used in high frequency device technology. Nevertheless, yield and uniformity of T-gate fabrication are often affected by the extreme lithography and other technological steps required for their realization. At very high

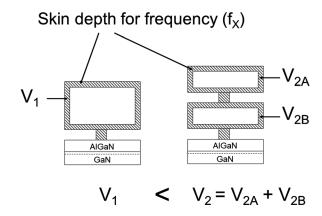

In this work, we present an alternative T-gate structure fabrication with the advantages of using only photolithography and with significantly increased electrode surface. The total cross-section of our developed double-level-T-gate (DLTG) contributing to the current transport is about 2-times higher than for a standard T-gate design (Fig. 1), resulting in halving the gate resistance.

Our DLTG layout is expected to provide significant improvement in high-frequency performance of HEMT (high electron mobility transistor) devices in comparison with conventional T-gate electrodes. Fig. 2 shows the

FIG. 1. Principle of double-level T-gate compared to conventional T-gate, showing double cross-section for current transport.

<sup>&</sup>lt;sup>2</sup>Jülich-Aachen Research Alliance, JARA, Fundamentals of Future Information Technology, D-52425 Jülich, Germany

<sup>&</sup>lt;sup>4</sup>Department of Nuclear Physic and Technique, Slovak University of Technology, SK-81219 Bratislava, Slovak Republic

<sup>&</sup>lt;sup>5</sup>Institute of Electronics and Photonics, Slovak University of Technology, SK-81219 Bratislava, Slovak Republic

<sup>&</sup>lt;sup>6</sup>Department of Inorganic Chemistry, Institute of Chemical Technology, Technická 5, Prague 6, Czech Republic

<sup>&</sup>lt;sup>7</sup>Faculté des Sciences, de la Technologie et de la Communication, Université du Luxembourg, L-1359 Luxembourg, Luxembourg

frequencies, the skin effect and the roughness of the gate metallization can further increase the gate resistance.

a) Author to whom correspondence should be addressed. Electronic mail: m.mikulics@fz-juelich.de.

FIG. 2. Calculated gate resistance as function of frequency for T-gate vs. DLTG structure.

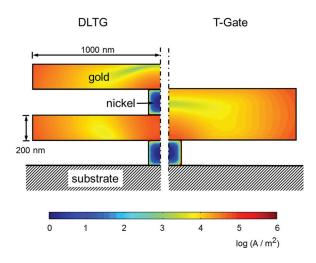

calculated frequency dependence of the resistance for both T-gate layouts. The calculations were performed with the COMSOL 4.2 Multiphysics (AC/DC module) software. The gate width was 100  $\mu m$ , with a gate length of 200 nm. The head of the conventional T-gate had a cross section of 2000 nm  $\times$  400 nm, while each level of the DLTG was 2000 nm  $\times$  200 nm. The results show a pronounced frequency dependence already below 10 GHz. From 50 GHz, the DLTG shows a decrease of the gate resistance compared to the conventional T-gate. At 200 GHz, the decrease is already 25%. The effect of surface roughness should even increase the influence of the DLTG. Figure 3 shows the current distribution of both layouts at 300 GHz. The current density in the Ni layers with high permeability is very strongly suppressed.

The exact influence of the gate resistance (and therefore of our T-gate layout) on transistor performance depends on the other intrinsic and extrinsic transistor parameters (transconductance, capacitances, etc.). In any case, our layout will reduce the skin effect related deteriorations of the transistor properties.

Our DLTG technology was applied on AlGaN/GaN based HEMTs. The HEMT-layer system consisted of a  $3-\mu$ m-thick undoped GaN layer followed by a 30-nm-thick AlGaN barrier layer with an aluminum mole fraction of

FIG. 3. Current distribution at 300 GHz. Below 1 GHz, the current density in the gold regions is uniform, with log(current density/A m<sup>-2</sup>)  $\approx$  6.

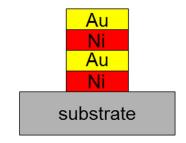

## Double T-Gate layer sequence

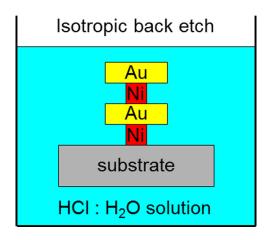

FIG. 4. Schematics of wet etching process for double-level-T-gate fabrication.

26%, grown on sapphire substrate. The transistor devices were fabricated in the conventional way. Mesa insulation was performed using Ar ion milling. Ohmic contact metallization based on Ti/Al/Ni/Au multilayer was annealed at  $850\,^{\circ}\text{C}$  for  $30\,\text{s}$  in  $N_2$  ambient. The source-drain spacing was

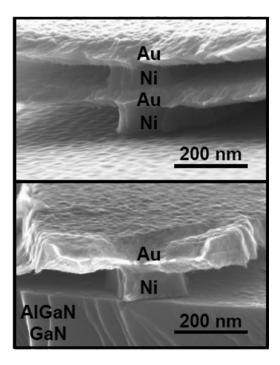

FIG. 5. Scanning electron microscope micrograph of double-level-T-gate contact (top) and T-gate (down) fabricated on AlGaN/GaN/sapphire material. Layer spacing and layer thicknesses are  $100\,\mathrm{nm}$ , respectively. Hut length is  $2\,\mu\mathrm{m}$ .

FIG. 6. Etched Ni T-gate foot after removal of the gold metallization, showing a uniform gate length.

$3~\mu m$ . The gate contacts consisted of a Ni/Au/Ni/Au stack with thicknesses of 200 nm for each layer. The designed gate length was  $2~\mu m$ . All metallizations were performed by standard photolithographic steps and liftoff processes. Our simple technological process for the fabrication of submicrometer sized T-gate structures is shown in Fig. 4.

The HEMT structures with the  $2 \mu m$  gate length electrodes were etched in HCl:H<sub>2</sub>O (1:100) solution for selective etching of the Ni films while keeping the Au layers intact (Fig. 4). Atomic force microscopy measurements reveal that the roughness of the AlGaN surface has not increased by the exposure to HCl. After etching, the samples were rinsed for 10 min in deionized water to stop the metal-interlayer recess process. The recess etching time was adjusted to fabricate gate electrodes with foot lengths down to 200 nm. Fig. 5 shows electron microscope pictures of a T-gate and a double-level-T-gate (both fabricated by recess etching).

The yield of our process was about 90%. The gold metallization was etched away on fabricated T-gates to investigate the roughness of the Ni etching (Fig. 6). The remaining Ni shows a very good uniformity and only small roughness of the sidewalls. The minimum gate length can be reduced to 100 nm and beyond, if the gate is stabilized mechanically.

The fabricated HEMT devices were first tested by DC measurements, showing nearly 2 times higher maximum drain current (0.7 A/mm) of the double-level-T-gate structures compared to the unetched counterpart with  $L_{\rm g}=2~\mu{\rm m}$  (0.4 A/mm). Similarly, the extrinsic transconductance

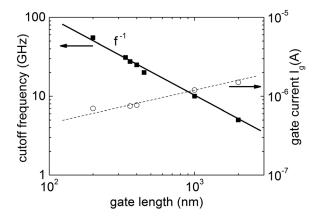

FIG. 7. Cutoff frequency and DC gate current vs. gate length of DLTG devices.

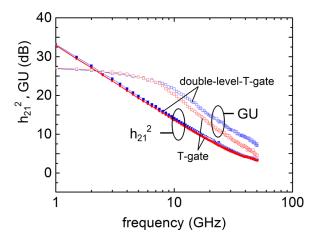

FIG. 8. Comparison of the current gain and unilateral power gain on HEMTs with T-gate structure and double-level-T-gate structure, both with 200 nm gate length. Thickness of T-gate hut is 400 nm, and thickness of DLTG hut is  $2\times200$  nm.

exhibits a value of 175 mS/mm for the 200 nm gate length device compared to 125 mS/mm for the  $2 \mu m$  gate length transistor. The reduction of the gate electrode length due to the recess etching is also demonstrated by the decrease of the threshold voltage from -3 V to -4.6 V for the 200 nm gate HEMT.

High frequency S-parameter measurements show an increase of the cutoff frequency from 6 GHz for the 2  $\mu m$  device to 60 GHz for the same device after etching the 200 nm double-level-T-gate structure. The cutoff frequency shows a 1/Lg dependence without indication of saturation for short gate lengths (Fig. 7). The same figure shows that the DC gate current  $I_g$  decreases with decreasing  $L_g$  contributing to the improvement of device performance. The behavior is similar for DLTG and T-gate devices.

Figure 8 presents a comparison of current gain and unilateral power gain (GU) of HEMTs with T-gate and double-level-T-gate structure (both with 200 nm gate width). While the performance of both transistors is identical for the current gain (the current gain is nearly independent on gate resistance), the HEMT device with DLTG electrode structure shows improved power gain at high frequencies compared to the T-gate counterpart. The  $f_{\rm max}$  value of the DLTG device is 115 GHz compared to 85 GHz for the T-gate transistor that is a 35% increase.

In conclusion, we have developed a multi-level-T-gate technique for fabrication of submicron gate lengths based on wet chemical etching that uses only standard photo-lithographical processes (no e-beam lithography). HEMT devices with 200 nm gate length showed a cutoff frequency of 60 GHz. HEMTs with a DLTG structure exhibit a 35% improvement of the  $f_{\rm max}$  value, compared to their conventional T-gate counterparts. Our technology demonstrates that application of T-gate stacks has a strong potential to decrease skin effect losses in gate structures, leading to substantial improvement of high-frequency performance of HEMTs.

This work was partially supported by Czech Science Foundation (Project No. 13-20507 S).

<sup>&</sup>lt;sup>1</sup>J. Mateos, T. Gonzalez, D. Pardo, V. Hoel, and A. Cappy, Semicond. Sci. Technol. **14**, 864–870 (1999).

- <sup>2</sup>W. C. Chang, T. C. Cheng, and K. F. Yarn, J. Optoelectron. Adv. Mater. **8**, 329–332 (2006).

- <sup>3</sup>W. E. Leitch, B. U. Henle, and E. Kohn, J. Electron. Mater. **25**, 1652–1659 (1996).

- <sup>4</sup>O. I. Saadat, J. W. Chung, E. L. Piner, and T. Palacios, IEEE Electron Device Lett. **30**, 1254–1256 (2009).

- <sup>5</sup>M. Nawaz, J. M. Miranda, P. Sakalas, S. M. Wang, Q. X. Zhao, M. Willander, and H. Zirath, Semicond. Sci. Technol. **15**, 728–735 (2000).

- <sup>6</sup>P. Kordoš, D. Gregušová, R. Stoklas, Š. Gaži, and J. Novák, Solid-State Electron. **52**, 973–979 (2008).

- <sup>7</sup>J. W. Chang, O. J. Saadat, J. M. Tirado, X. Gao, S. Guo, and T. Palacios, IEEE Electron Device Lett. **30**, 904–906 (2009).

- <sup>8</sup>Y. O. Wu, M. Xu, P. D. Ye, Z. Cheng, J. Li, J.-S. Park, J. Hydrick, J. Bai, M. Carroll, J. G. Florenza, and A. Lochtefeld, Appl. Phys. Lett. 93, 242106 (2008).

- <sup>9</sup>T. Palacios, C.-S. Suh, A. Chakraborty, S. Keller, S. P. DenBaars, and U. K. Mishra, IEEE Electron Device Lett. **27**(6), 428 (2006).

- <sup>10</sup>J.-W. Lim, H.-K. Ahn, H.-G. Ji, W.-J. Chang, J.-K. Mun, and H. Kim, Semicond. Sci. Technol. **19**, 1416–1421 (2004).

- <sup>11</sup>K. Tabatabaie-Alavi, D. M. Shaw, and P. J. Duval, IEEE Trans. Semicond. Manuf. 16, 365–369 (2003).

- <sup>12</sup>N. Sarazin, E. Morvan, M. A. di Forte Poisson, M. Oualli, C. Gaquiere, O. Jardel, O. Drisse, M. Tordjman, M. Magis, and S. L. Delage, IEEE Electron Device Lett. 31, 11 (2009).

- <sup>13</sup>L. J. Guo, J. Phys. D: Appl. Phys. **37**, R123–R141 (2004).