John von Neumann Institute for Computing (NIC)

Felix Wolf

# **Automatic Performance Analysis on Parallel Computers with SMP Nodes**

NIC Series Volume 17

ISBN 3-00-010003-2

Die Deutsche Bibliothek – CIP-Cataloguing-in-Publication-Data A catalogue record for this publication is available from Die Deutsche Bibliothek

Publisher: NIC-Directors

Distributor: NIC-Secretariat

Research Centre Jülich

52425 Jülich Germany

Internet: www.fz-juelich.de/nic

Printer: Graphische Betriebe, Forschungszentrum Jülich

#### © 2003 by John von Neumann Institute for Computing

Permission to make digital or hard copies of portions of this work for personal or classroom use is granted provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise requires prior specific permission by the publisher mentioned above.

NIC Series Volume 17

ISBN 3-00-010003-2

## **Automatic Performance Analysis on Parallel Computers with SMP Nodes**

Von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

Diplom-Informatiker

Felix Wolf

aus München

Berichter: Universitätsprofessor Dr. rer. nat. Friedel Hoßfeld Universitätsprofessor Christian H. Bischof, Ph.D.

Tag der mündlichen Prüfung: 27.11.2002

#### **Abstract**

Parallel computers with SMP nodes provide both multithreading and message passing as their modes of parallel execution. This thesis addresses the complexity of the performance problems that can arise in these systems by formally characterizing the problems in terms of execution patterns that represent situations of inefficient behavior. These patterns are specified as compound events which are input for an automatic analysis process that recognizes and quantifies the inefficient behavior in event traces. Mechanisms that hide the complex relationships within compound-event specifications allow a simple description of complex inefficient behavior on a high level of abstraction.

The analysis process automatically transforms event traces into a scalable representation of performance behavior, allowing a fast and easy identification of performance bottlenecks on varying levels of granularity along the dimensions of problem type, call graph, and process or thread. The uniform mapping of performance behavior onto the corresponding fraction of execution time enables the convenient correlation of different performance behavior using only a single integrated view. A modular analysis architecture separates the performance-problem specifications from the actual analysis process, simplifying the extension and customization of predefined performance problems to meet individual (e.g., application-specific) needs.

To demonstrate the methodology in real parallel-programming environments, it was applied to the programming interfaces MPI, OpenMP, and their combination. To show the methodology's usefulness in practice, the performance-tool prototype EXPERT was implemented and successfully tested for several real-world applications.

#### Kurzfassung

Parallelrechner mit SMP-Knoten bieten sowohl Multithreading als auch Message-Passing als parallele Programmiermodelle. Diese Dissertationsschrift behandelt die potenziellen Leistungsprobleme solcher Systeme mit Hilfe einer formalen Beschreibung von Ausführungsmustern, die Situationen ineffizienten Verhaltens repräsentieren. Die Muster werden als Verbundereignisse spezifiziert und dienen als Eingabe für einen automatischen Analyseprozess, der das ineffiziente Verhalten in Ereignisspuren nachweist und quantifiziert. Mechanismen zur Kapselung komplexer Beziehungen innerhalb der Verbundereignisspezifikationen erlauben eine einfache Beschreibung komplexen ineffizienten Verhaltens auf hohem Abstraktionsniveau.

Der Analyseprozess transformiert Ereignisspuren automatisch in eine skalierbare Repräsentation des Leistungsverhaltens, die eine schnelle und einfache Identifizierung von Leistungsengpässen auf beliebigen Granularitätsstufen entlang der Dimensionen Problemtyp, Aufrufpfad, und Prozess oder Thread erlaubt. Die einheitliche Abbildung des Leistungsverhaltens auf den entsprechenden Anteil der Ausführungszeit ermöglicht den mühelosen Vergleich unterschiedlichen Verhaltens in einer einzigen integrierten Darstellung. Eine modulare Analysearchitektur separiert die Spezifikationen der Leistungsprobleme vom eigentlichen Analyseprozess, was die Erweiterung und Anpassung vordefinierter Leistungsprobleme an individuelle (z.B. anwendungsspezifische) Bedürfnisse gestattet.

Zur Verwendung in realen parallelen Programmierumgebungen wurde dieser Ansatz auf die Programmierschnittstellen MPI, OpenMP und deren Kombination angewandt. Zum Nachweis der Praxistauglichkeit wurde das Leistungsanalysewerkzeug EXPERT prototypisch implementiert und erfolgreich anhand realer Anwendungen getestet.

#### Acknowledgments

This thesis was written at the Zentralinstitut für Angewandte Mathematik (ZAM) of Forschungszentrum Jülich. I would like to thank my advisor, Prof. Dr. Friedel Hoßfeld, who has the chair of Technical Informatics and Computer Science at Aachen University of Technology and who was director of the ZAM during my time as a PhD student, for giving me the opportunity to work in this excellent and supportive environment and for his equally generous and wise guidance throughout the course of my PhD. Also, I would like to thank Prof. Dr. Christian Bischof for serving as the second referee. In addition, I would like to acknowledge Dr. Rüdiger Esser, head of the ZAM department Programming Techniques, for his continuous support of my thesis project.

It was a great privilege to work with Dr. Bernd Mohr, and I would like to express my deep gratitude for his creative influence and his selfless support.

It was a pleasure to carry out my thesis research as a part of the IST working group APART, whose members contributed many ideas, created an inspiring atmosphere at various meetings, and are great colleagues. In particular, I would like to thank Prof. Dr. Allen Malony for carefully reviewing my thesis prior to its submission and for all his motivating comments during the last three years. I am also grateful to Prof. Dr. Michael Gerndt for his constant encouragement and his many helpful suggestions, especially during the early stages of my thesis research. I also would like to thank Dr. Luiz DeRose for creating the opportunity of a visiting research studentship at the IBM T. J. Watson Research Center.

Special thanks go to Janet Carter-Sigglow, who spent long hours polishing the language of my thesis manuscript. Thanks are also due to Dr. Bernhard Steffen and Dr. Peter Weidner, who took care of its mathematical correctness. I am indebted to Prof. Dr. Rudolf Berrendorf and Ulrich Detert, who jointly built up the ZAMpano SMP cluster, which served as the primary development platform of the prototype described in this thesis. I am grateful to Wolfgang Frings and Reiner Vogelsang for helping me conduct my experiments, to Deutsches Klima Rechenzentrum, the Institut für Chemie und Dynamik der Geosphäre IV, and the Institut für Festkörperforschung for giving me access to their applications, to Dietrich Bartel for his assistance in graphical questions, and to Arpad Kiss for providing the basic tree-browser implementation of the prototype's user interface. And finally thanks to all other colleagues who provided support and helped me complete this thesis.

I had the pleasure of writing my thesis at the ZAM in parallel with Stefan Birmanns, who shared with me all the ups and downs of being a PhD student. Finally, I feel a deep sense of gratitude to my parents and to Ilka Müller for their patience and their support during the PhD period.

Felix Wolf December 2002, Jülich, Germany

## **Contents**

| Li | st of l | t of Figures                        |     |  |

|----|---------|-------------------------------------|-----|--|

| Li | st of ' | Γables                              | vii |  |

| 1  | Intr    | oduction                            | 1   |  |

|    | 1.1     | Architectures of Parallel Computers | 1   |  |

|    | 1.2     | Coupled SMP Systems                 | 2   |  |

|    | 1.3     | Interconnection Networks            | 3   |  |

|    | 1.4     | Programming Models                  | 3   |  |

|    |         | 1.4.1 Message Passing               | 4   |  |

|    |         | 1.4.2 Shared Memory                 | 4   |  |

|    |         | 1.4.3 Hybrid Model                  | 5   |  |

|    | 1.5     | Automatic Performance Analysis      | 5   |  |

|    | 1.6     | Contribution of this Thesis         | 6   |  |

|    | 1.7     | Document Organization               | 8   |  |

| 2  | Auto    | omatic Performance Analysis         | 11  |  |

|    | 2.1     | Complexity in Parallel Systems      | 11  |  |

|    | 2.2     | Performance Indices and Bounds      | 12  |  |

|    | 2.3     | Performance Analysis Process        | 13  |  |

|    | 2.4     | Performance Data                    | 15  |  |

|    |         | 2.4.1 Profiles                      | 16  |  |

|   |      | 2.4.2     | Event Traces                        | 16 |

|---|------|-----------|-------------------------------------|----|

|   | 2.5  | Instrur   | mentation                           | 17 |

|   | 2.6  | Perform   | mance Properties                    | 19 |

|   | 2.7  | Autom     | natic Performance Analysis          | 22 |

| 3 | Spec | cificatio | n of Performance Behavior           | 27 |

|   | 3.1  | Ration    | ale                                 | 27 |

|   | 3.2  | System    | n Observation Based on Events       | 28 |

|   | 3.3  | Event-    | Model Enhancement                   | 30 |

|   |      | 3.3.1     | State Sequences                     | 31 |

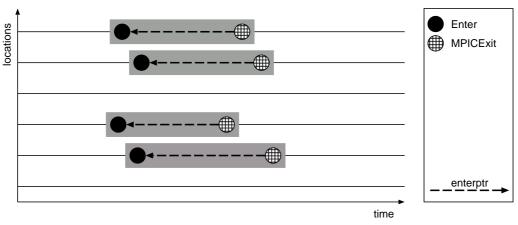

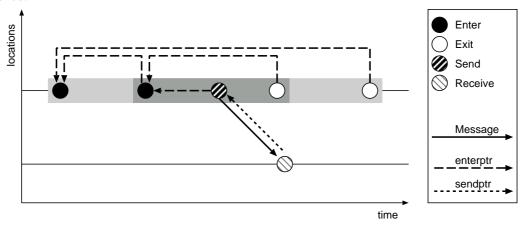

|   |      | 3.3.2     | Pointer Attributes                  | 33 |

|   |      | 3.3.3     | Implementation of an Enhanced Model | 34 |

|   | 3.4  | Model     | Enhancement: MPI                    | 35 |

|   |      | 3.4.1     | Basic Event Model                   | 35 |

|   |      | 3.4.2     | Enhancement                         | 37 |

|   |      | 3.4.3     | MPI 2                               | 42 |

|   | 3.5  | Model     | Enhancement: OpenMP                 | 43 |

|   |      | 3.5.1     | Basic Event Model                   | 43 |

|   |      | 3.5.2     | Enhancement                         | 46 |

|   | 3.6  | Model     | Enhancement: Hybrid Model           | 50 |

|   |      | 3.6.1     | MPI                                 | 53 |

|   |      | 3.6.2     | OpenMP                              | 53 |

|   |      | 3.6.3     | Dynamic Call Path                   | 55 |

|   |      | 3.6.4     | Summary                             | 59 |

|   | 3.7  | Specif    | ying Compound Events                | 62 |

|   | 3.8  | Examp     | ble Compound Events                 | 64 |

|   |      | 3.8.1     | MPI                                 | 64 |

|   |      | 3.8.2     | OpenMP                              | 69 |

|   |      | 3.8.3    | Call Paths                                   | 71  |

|---|------|----------|----------------------------------------------|-----|

|   |      | 3.8.4    | Compound-Event Instantiation and Constraints | 72  |

|   | 3.9  | Compo    | ound Events in ASL                           | 72  |

|   |      | 3.9.1    | Language Extensions                          | 74  |

|   |      | 3.9.2    | Event Types and Abstractions in ASL          | 76  |

|   |      | 3.9.3    | Pattern Matches                              | 76  |

|   |      | 3.9.4    | Example: Late Sender in ASL                  | 78  |

|   |      | 3.9.5    | Using Patterns in Property Definitions       | 79  |

|   | 3.10 | Summ     | ary                                          | 80  |

| 4 | Ana  | lysis of | Performance Behavior                         | 81  |

|   | 4.1  | Perfor   | mance Behavior of Coupled SMPs               | 81  |

|   | 4.2  | Overal   | ll Architecture                              | 82  |

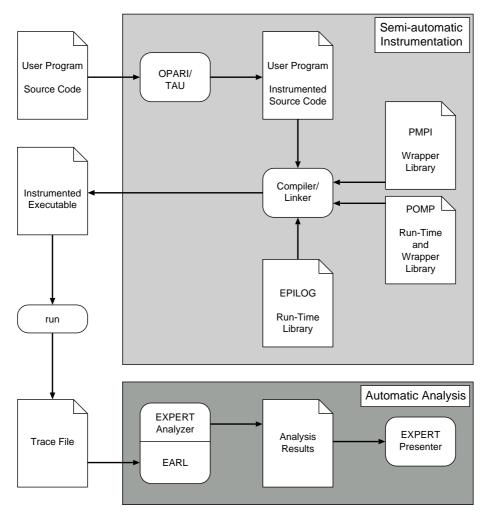

|   | 4.3  | Event-   | Trace Generation                             | 83  |

|   |      | 4.3.1    | Data Format                                  | 84  |

|   |      | 4.3.2    | Instrumentation                              | 84  |

|   |      | 4.3.3    | Clock Synchronization                        | 85  |

|   | 4.4  | Analys   | sis Process                                  | 86  |

|   |      | 4.4.1    | Representation of Performance Behavior       | 87  |

|   |      | 4.4.2    | Interval Sets                                | 88  |

|   |      | 4.4.3    | Performance Space                            | 91  |

|   |      | 4.4.4    | EARL                                         | 98  |

|   |      | 4.4.5    | Pattern Classes                              | 100 |

|   |      | 4.4.6    | Performance Properties                       | 102 |

|   |      | 4.4.7    | Extensibility Mechanism                      | 106 |

|   | 4.5  | Visual   | ization of Performance Behavior              | 107 |

|   | 4.6  | Limita   | itions                                       | 109 |

|   | 17   | Advon    | cad Tachniques                               | 100 |

| Bi | hling | raphy   |                       | 137 |

|----|-------|---------|-----------------------|-----|

| 7  | Sum   | ımary a | nd Conclusions        | 133 |

| 6  | Rela  | ated Wo | rk                    | 127 |

|    | 5.4   | SWEE    | P3D                   | 123 |

|    | 5.3   | REMO    | )                     | 121 |

|    | 5.2   | CX3D    |                       | 118 |

|    | 5.1   | TRAC    | E                     | 116 |

| 5  | Exa   | mples   |                       | 115 |

|    | 4.8   | Summ    | ary                   | 113 |

|    |       | 4.7.3   | Generic Visualization | 112 |

|    |       | 4.7.2   | Publish and Subscribe | 111 |

|    |       | 4.7.1   | Selective Tracing     | 110 |

## **List of Figures**

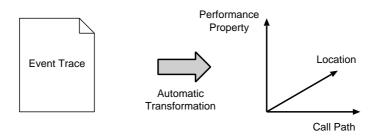

| 1.1  | Transformation into a property-oriented performance space | 7  |

|------|-----------------------------------------------------------|----|

| 2.1  | Idealized performance-analysis environment                | 15 |

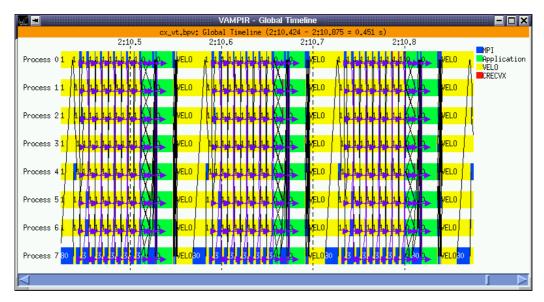

| 2.2  | Event-trace visualization using VAMPIR                    | 18 |

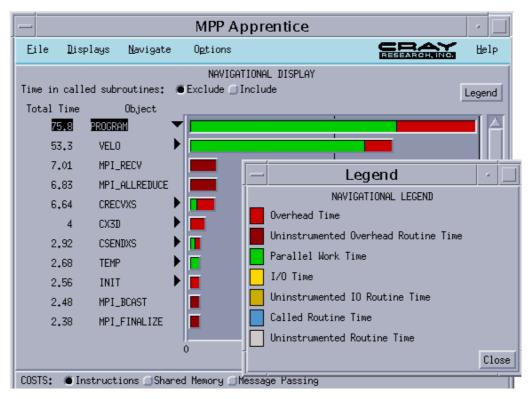

| 2.3  | Apprentice profile browser                                | 23 |

| 2.4  | Xprofiler call-graph diagram                              | 24 |

| 3.1  | Event model for MPI applications                          | 37 |

| 3.2  | An MPI collective-operation instance                      | 39 |

| 3.3  | References provided by pointer attributes                 | 42 |

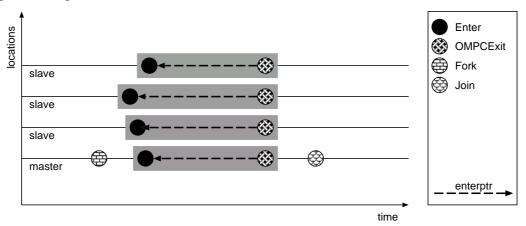

| 3.4  | Collective execution of an OpenMP parallel region         | 45 |

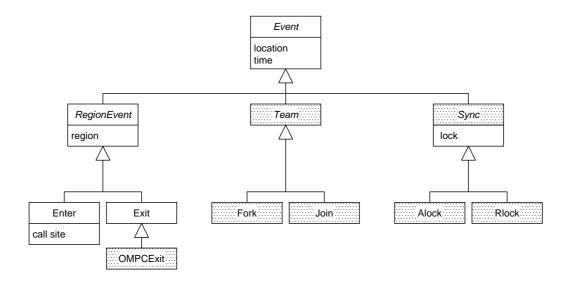

| 3.5  | Event model for OpenMP applications                       | 46 |

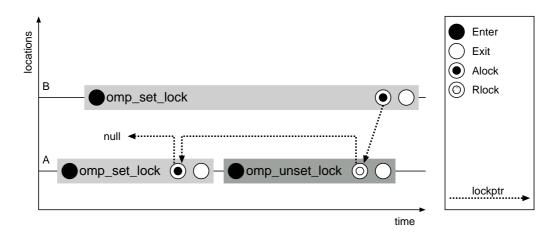

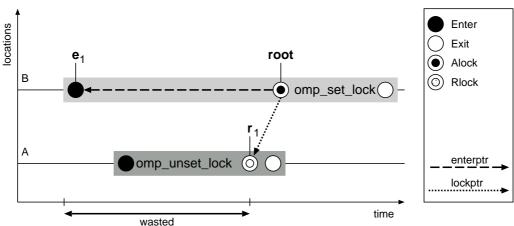

| 3.6  | The $lockptr$ attribute                                   | 50 |

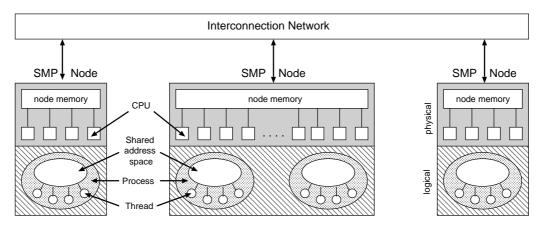

| 3.7  | The physical and logical structure of coupled SMPs        | 51 |

| 3.8  | Type hierarchy for hybrid applications                    | 60 |

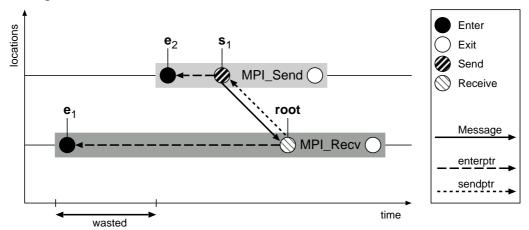

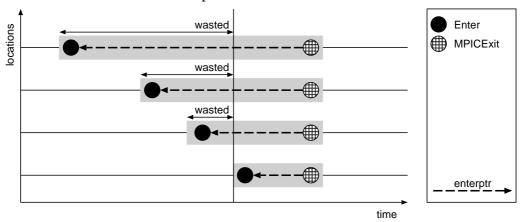

| 3.9  | Late Sender compound event                                | 65 |

| 3.10 | Late Receiver compound event                              | 67 |

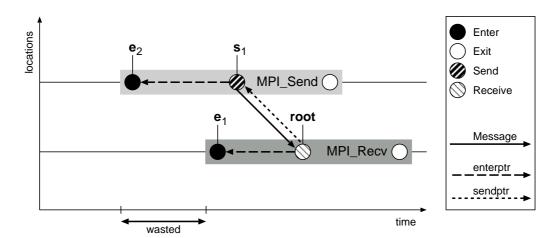

| 3.11 | Passing messages in the wrong order                       | 68 |

| 3.12 | Synchronization overhead of n-to-n collective operations  | 69 |

| 3.13 | Waiting for an OpenMP lock                                | 70 |

| 3.14 | Usage of the ASL property construct                       | 73 |

| 3.15 | ASL expression-syntax extensions                          | 74 |

| 3.16 | ASL pattern-specification syntax                                 | 75  |

|------|------------------------------------------------------------------|-----|

| 3.17 | The Rs ( ) function returning the region stack of a process      | 77  |

| 3.18 | The enterptr() function returning the <i>enterptr</i> attribute  | 77  |

| 3.19 | Late Sender pattern specification in ASL                         | 79  |

| 3.20 | Late Sender property using a pattern                             | 79  |

| 4.1  | EXPERT overall architecture                                      | 83  |

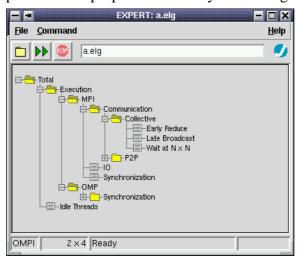

| 4.2  | GUI of the EXPERT analyzer                                       | 87  |

| 4.3  | Time model of EXPERT                                             | 89  |

| 4.4  | EXPERT's location hierarchy                                      | 94  |

| 4.5  | The layered design of the EXPERT analyzer                        | 100 |

| 4.6  | Python definition of the base class Pattern                      | 101 |

| 4.7  | Python class definition of the <i>Late Sender</i> compound event | 102 |

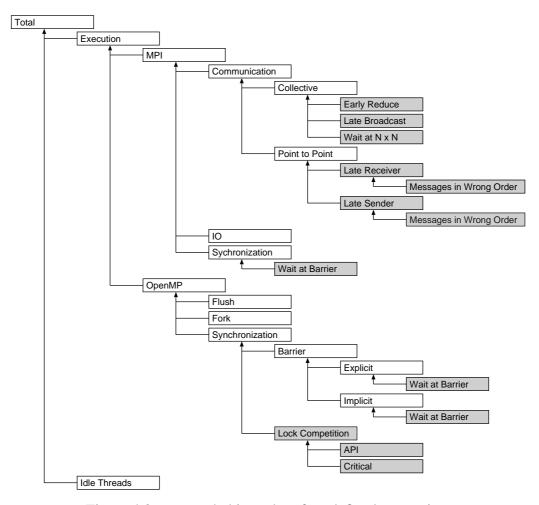

| 4.8  | EXPERT's hierarchy of predefined properties                      | 103 |

| 4.9  | Weighted tree in collapsed and expanded state                    | 107 |

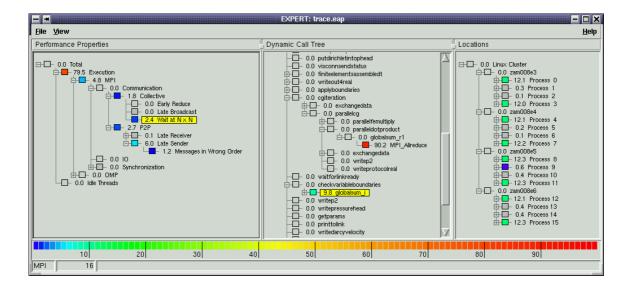

| 5.1  | EXPERT result display for TRACE                                  | 116 |

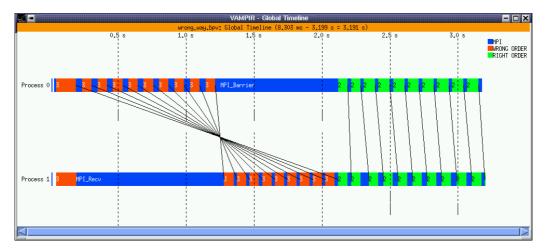

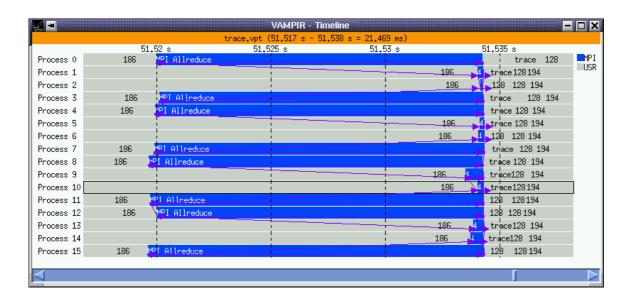

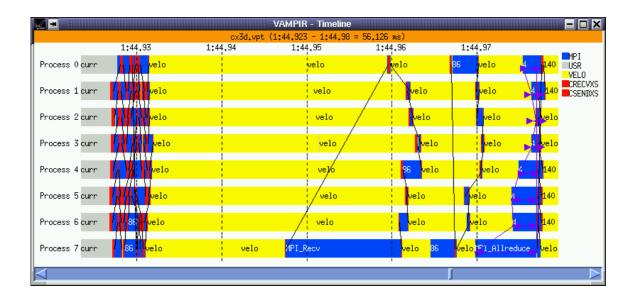

| 5.2  | VAMPIR time-line diagram of TRACE                                | 118 |

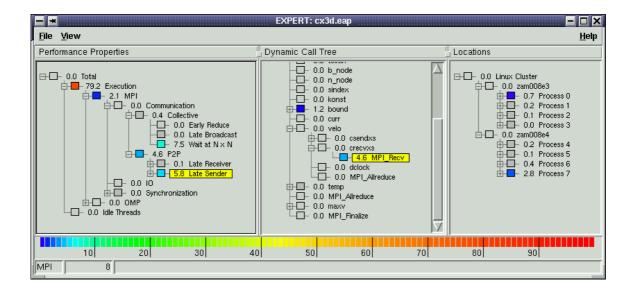

| 5.3  | EXPERT result display for CX3D                                   | 119 |

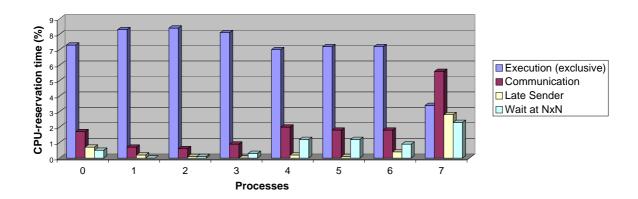

| 5.4  | Distribution of performance properties in VELO                   | 120 |

| 5.5  | VAMPIR time-line diagram of CX3D                                 | 121 |

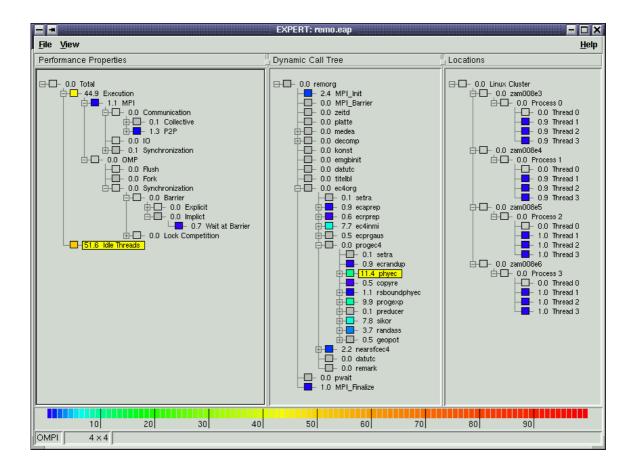

| 5.6  | EXPERT result display for REMO                                   | 122 |

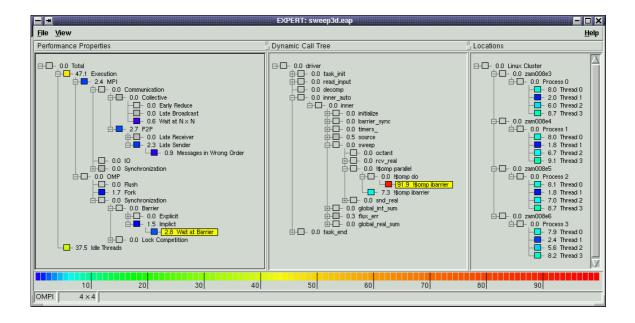

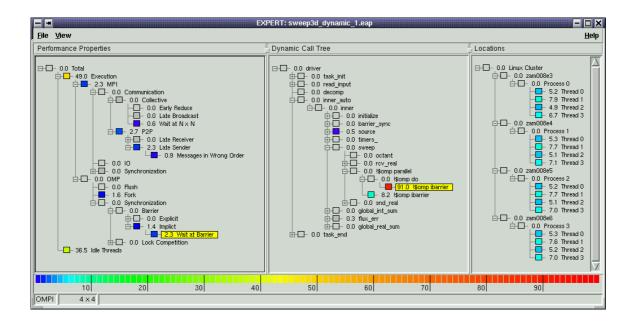

| 5.7  | EXPERT result display for SWEEP3D                                | 124 |

| 5.8  | Dynamic scheduling in SWEEP3D                                    | 125 |

## **List of Tables**

| 3.1 | Summary of event attributes             | 29  |

|-----|-----------------------------------------|-----|

| 4.1 | Severity amounts shown in tree displays | 108 |

| 5.1 | Trace-file size and overhead.           | 115 |

| 5.2 | Performance problems found in TRACE     | 117 |

| 5.3 | Performance problems found in CX3D      | 119 |

| 5.4 | Performance problems found in REMO      | 122 |

| 5.5 | Performance problems found in SWEEP3D   | 123 |

## **Chapter 1**

#### Introduction

During the last few decades parallel computing has proved to be an essential tool for the solution of complex scientific and economic problems. The numerical simulation of physical, chemical, and biological processes provides insight into phenomena that either cannot be addressed by analytical or experimental methods or that require experiments that are too expensive or dangerous. Parallel computing also plays a key role in achieving and preserving scientific and thus economic competitiveness. As more powerful computing resources become available, grand-challenge applications, such as protein-structure prediction and weather prediction, will become reality.

A parallel computer effectively multiplies the performance of single processors. Unfortunately, real applications frequently fail to sustain even a major fraction of the theoretical performance limit that is possible on a given parallel machine. The reason for this gap between peak and real performance lies in the complex interactions among the hardware, system software, programming interface, and algorithm. Understanding the effects of these interactions is crucial for optimizing parallel programs and thus for a better utilization of the available computer hardware.

#### 1.1 Architectures of Parallel Computers

Parallel computers are computers with multiple processors that are able to work jointly on one or more tasks at the same time. One common way to classify parallel computers is based on memory architecture. There are two major classes: *shared memory* and *distributed memory*.

Shared-memory machines, which are also referred to as *symmetric multiprocessors* or *shared-memory multiprocessors* (SMPs) [41], have symmetric access to one shared address

space and are controlled by one operating-system image. This makes it possible, for example, to suspend a process on one processor and to resume it on another processor without copying or moving its address space.

SMPs that share one physical memory belong to the class of UMA (*Uniform Memory Access*) computers and provide symmetric and equally fast access to all addresses of the shared address space. Examples are CRAY T90, IBM 390, SUN E10000.

SMPs that provide a shared address space based on physically distributed memory [31] have variable access times to a memory address depending on the physical distance to that address. These machines are called NUMA (Non-Uniform Memory Access) computers. ccNUMA (cache coherent Non-Uniform Memory Access) computers are similar to NUMA computers but provide a mechanism for local buffering of remote memory contents in a cache after the first access so that subsequent accesses to the same memory location can be much faster. Cache-coherence protocols ensure that modifications of cached or original data occur consistently. Examples are SGI ORIGIN 2000 and HP V-Class.

Distributed-memory parallel systems, which are often referred to as as *massively parallel processors* (MPPs) when larger numbers of processors are used, do not provide a shared address space. Each memory is local to one processor and not accessible from another processor. Message passing is used to move data between processors. However, some systems provide mechanisms to access remote memory locations on the hardware level. Examples are CRAY T3E and IBM RS/6000-SP.

#### 1.2 Coupled SMP Systems

In the past, MPP systems dominated the scientific computing market, but they claimed only a minor share of the industrial market. In contrast, SMP systems, which are frequently used as database servers, gained increasing popularity both in research and industry. For this reason, more powerful and cheaper SMP systems are likely to become available in the future. However, single SMP systems will not be able to meet the performance requirements of many large-scale applications. Coupling multiple SMP systems is one way to increase the number of processors and thus to provide sufficient computing power to handle such large-scale high-performance problems.

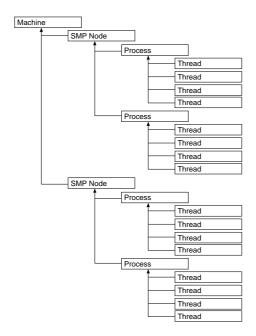

Hoßfeld et al. [40] distinguish between *parallel computers with* SMP *nodes* and *clustered* SMPs. Parallel computers with SMP nodes are tightly coupled over a dedicated network and present themselves to the user as one uniform computer system. Clustered SMPs are only loosely coupled, for example, over a local area network. Both types of architecture are called *coupled* SMP *systems*. By the nature of their memory-system architecture, coupled SMP systems are also distributed-memory systems because memory is distributed across multiple SMP nodes.

Hence, in contrast to single SMPs, coupled SMPs introduce an additional level in the memory-hardware architecture, which now forms a hierarchy of distributed shared memories. Unfortunately, this memory hierarchy further complicates the performance behavior and makes parallel programming more difficult. While the expected economic advantages argue for coupled SMP solutions to high-performance computing, the complex hardware structure of coupled SMPs creates a strong need for programming tools that provide assistance in writing efficient codes for these platforms.

However, coupled SMPs are interesting for another reason as well. This class of computers implements a very general architectural concept, which contains other architectures, such as distributed and shared memory, and, of course, simple sequential architectures, as specializations. So most of the programming tools that apply to coupled SMPs can be used for these subclasses, too.

#### 1.3 Interconnection Networks

The different nodes of a coupled SMP system communicate over an interconnection network. The network performance has a major influence on the overall performance of the system. There are a variety of network topologies that differ in node degree, network diameter, and bisection width.

The nodes of clustered SMPs are often connected with a *local-area network* (LAN) or a *wide-area network* (WAN). In this context, LAN technologies, such as Ethernet, FDDI, ATM, and HiPPI, which are described in more detail in [71], come into operation.

In principle, LAN technologies can also be used to equip parallel computers with SMP nodes, but in most cases these computers use *system-area networks* (SANs), which have been developed specifically to provide better bandwidth and latency by circumventing operating-system protocol stacks. Examples of general-purpose SANs frequently found in the PC-cluster area are Myrinet [60] and SCI (Scalable Coherent Interface) [43].

#### 1.4 Programming Models

The choice of programming models for coupled SMPs is influenced by the hierarchical memory architecture, which provides shared memory inside single nodes and distributed memory across different nodes. In principle, a shared address space across all SMP nodes is technically feasible but it usually requires sophisticated hardware or software solutions, such as reflective memory [44] or TreadMarks [2], respectively.

For this reason, the primary programming model for coupled SMPs is *message passing* because it provides a simple way to communicate across node borders. Inside single nodes, programs may alternatively use the *shared-memory* model. If both message-passing and shared-memory programming are used for a coupled-SMP program, it is commonly referred to as a *hybrid* programming model.

A distinctive feature of the shared-memory model is that it provides implicit communication over shared-memory locations, whereas message passing requires communication to be made explicit using dedicated operations. Common to both is that each processor executes different control flows, which corresponds to the *multiple-instruction stream* – *multiple-data stream* (MIMD) model in Flynn's classification [25]. Often the instructions come from the same program, in which case the whole computation is a *single-program, multiple-data* (SPMD) computation.

The following subsections give a brief introduction to all three programming models.

#### 1.4.1 Message Passing

Message passing is mainly used on distributed-memory architectures. A message-passing program runs multiple processes, where each process owns one private address space. Communication among different processes takes place only by sending and receiving messages. The messages may be sent either via a network or using shared memory locations if available. Communication between two processes occurs either two-sidedly, where both participating processes have to invoke an operation, or one-sidedly, where only one process has to invoke an operation.

The MPI (*Message Passing Interface*) communication library [52, 53] defines a de facto standard for message passing and is available on most parallel computers. The latest version, MPI 2.0, supports all traditional message-passing features, such as point-to-point communication and collective communication, advanced features, such as process topologies and one-sided communication, but also features that go beyond pure message passing, such as parallel IO.

#### 1.4.2 Shared Memory

A shared-memory program consists of a collection of *tasks*, which are assigned to asynchronously working threads. To accomplish these tasks, all threads have access to a shared address space. Synchronization utilizes specific mechanisms, such as locks and barriers, to implement coherent control of shared-memory access.

The shared-memory programming model comes in three varieties. UNIX System V supports *shared segments*, which provide a mechanism to define shared memory segments and

map them onto the virtual address space of different processes. Programs based on *threads* first create one master thread and later fork additional threads depending on the work to be distributed. In this case, all threads share the same address space and the programmer uses synchronization primitives for sharing memory. The third approach is sequential-program parallelization. Here, the programmer inserts directives or pragmas that assist the compiler in automatically parallelizing computation-intensive code sections.

OpenMP (*Open specifications for Multi Processing*) [61, 62] is a widespread programming interface for scientific shared-memory programming. It defines directives, pragmas, and library calls to control the parallelization of loops and other code sections in Fortran, C, and C++ programs. Execution of an OpenMP program starts with one master thread, which creates a team of slave threads as soon as a parallel region has been entered. After leaving this region, the team terminates and sequential execution resumes. Synchronization is accomplished either implicitly or explicitly by certain directives, pragmas, or library calls. OpenMP implementations are usually based on a low-level thread library.

#### 1.4.3 Hybrid Model

Coupled SMP systems can be programmed using a hybrid combination of message-passing and shared-memory techniques, where shared-memory is used for data sharing inside single nodes and message passing is used for communication across different nodes. Most significant in this context is the combination of MPI and OpenMP. In this case, there is usually one MPI process per SMP node, and OpenMP parallelization can occur in each process. If the application needs to call MPI routines from multiple threads belonging to the same process, a thread-safe MPI implementation is required.

#### 1.5 Automatic Performance Analysis

The process of investigating the performance behavior of an application and finding the reasons for limited performance is called *performance analysis*. It usually precedes any modification of the source code that is intended to optimize or tune the program. Both activities form a cycle that must often be repeated many times until the application delivers the desired performance.

Performance analysis includes several complicated and time-consuming tasks. The developer usually compares a hypothesis of performance, which may be based on a performance model, to objective observations of the run-time behavior. To do so requires instrumenting and monitoring the application. To draw reasonable conclusions from the collected performance data, the data may need several postprocessing steps. Finally, the developer searches through the data, tries to (dis)prove the hypothesis, and thinks about ways to improve the

application's performance behavior. Clearly, performance analysis demands a significant fraction of the overall time required for development and appropriate programming tools could both save time and improve the quality of this process.

Although during the last few decades many achievements have been made, the current situation still suffers from the lack of a software infrastructure that supports all these steps in a satisfactory, automatic manner. Powerful tools, such as VGV [38], provide valuable assistance in analyzing the performance of MPI and OpenMP programs by visualizing the run-time behavior and calculating statistics over the performance data. However, the developer is still required to filter out relevant parts from a huge amount of low-level information and map that information onto the application-program abstractions without tool support. Furthermore, many approaches, such as OPAL [30], are compiler- or language-dependent and, thus, restricted in their portability.

Automating the process of analyzing the performance means automatically delivering the information that is necessary to understand the reasons for inefficient program behavior. Thus, it aims at both reducing the amount of work that is left to the software developer and providing information that cannot be derived manually. In particular, the identification of performance problems, their classification by kind and severity, and their localization in the source code should be addressed.

#### 1.6 Contribution of this Thesis

The kind of performance data available has a great influence on the expressiveness of the performance problems that can be detected. Summary information, as collected by profiling tools, is sufficient to detect a multitude of frequently occurring performance problems. However, there are performance problems that are not visible in this kind of information. In contrast, event traces allow the reconstruction of the dynamic behavior in terms of single events and provide a more detailed view.

This thesis presents a novel approach to analyzing the performance of parallel applications based on event traces. Its strength lies in its ability to allow a deeper but more intuitive insight into performance behavior than is provided by traditional tools. This is achieved through an automatic transformation of fine-grained but low-level performance data, whose analysis is time-consuming and may require a high learning effort when based on such tools, into a more abstract and more expressive view accessible through a simple but flexible user interface.

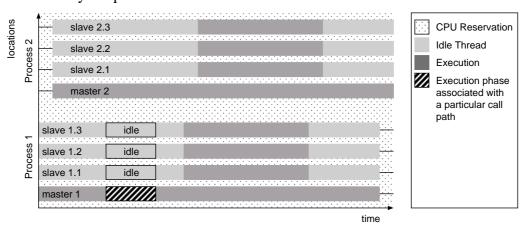

The thesis describes the automatic transformation of event traces into a three-dimensional property-oriented performance space (Figure 1.1). The approach covers event traces that are generated from MPI, OpenMP, or hybrid applications. Hence, it is especially well

suited for parallel computers with SMP nodes. The performance space presents the performance behavior along three dimensions: performance property, node within the dynamic call graph, and location on the machine, such as SMP node or process.

Figure 1.1: Transformation of event traces into a property-oriented performance space.

The performance-property dimension describes the kind of performance behavior. The call-graph dimension describes both the source-code location and the execution phase during which a performance behavior (i.e., property) occurs. Finally, the location dimension gives information on the distribution of performance across different processes or threads. Each dimension is arranged in a hierarchy, which allows the representation of performance behavior on different levels of granularity and pays attention to the hierarchical hardware and software structure of coupled SMPs. Each point in the representation is mapped onto the corresponding fraction of program execution time, allowing the convenient correlation of different behavior along multiple dimensions using only a single integrated view.

The performance properties to be analyzed mostly refer to common situations resulting from a suboptimal usage of the underlying programming model, such as a process waiting for a message from another process. Specification of performance properties is done in terms of *compound events* composed of simple events as recorded in the trace file. A layer of abstraction based on the grouping of related events makes the specifications simple and easy to extend. The resulting specifications serve as input for an automatic analysis process that is responsible for detecting the corresponding compound events in event traces.

Characterization of performance behavior is based on complex event patterns in conjunction with their location in a multi-dimensional structure. This provides both a technique of abstracting from low-level events to meaningful performance situations and a precise way of associating such situations with a place in the source code, an execution phase, and a control-flow point. Since the approach mainly refers to the programming model instead of specific hardware elements, it also provides a high degree of portability.

To accomplish this, the thesis defines a framework for formally specifying compound events that characterize performance behavior on a very high level of abstraction. By looking for such compound events in an event trace, it is possible to prove that particular performance problems are present in an application.

The framework identifies two categories of abstractions whose instances provide a basis for easily specifying compound events. The abstractions represent entities of the different programming models, such as MPI collective operations or OpenMP parallel constructs, and are useful for measuring their influence on performance behavior. The resulting specifications can be easily transformed into an appropriate detection algorithm. Examples are shown of how the approach applies to MPI, OpenMP, and the hybrid combination of both the most relevant programming models for coupled SMPs.

The implementation of the automatic performance tool EXPERT for MPI, OpenMP, and hybrid applications proves the feasibility of this approach. The comprehensive behavioral classification incorporated in EXPERT explains a multitude of problems in terms of previously specified compound events. Extensibility mechanisms open the classification up to adding new behavior classes, if the predefined ones are not sufficient. EXPERT also offers a display technique based on multiple tree browsers, allowing the user to conveniently navigate through the performance space. Colors assist in identifying performance problems and bottlenecks, and help in investigating them on the most appropriate level of detail. The trees are interconnected so that the user can view one dimension with respect to a selection in another dimension.

Most of the ideas contributed by this thesis apply to coupled SMPs in general. Unfortunately, event tracing is rarely applicable to clustered SMPs because it requires a level of clock synchronization that cannot usually be provided by this class of computing environments. For this reason, parallel computers with SMP nodes are the primary target of the approach taken in this thesis.

#### 1.7 Document Organization

The thesis is structured in two parts. The first part is more theoretical and concentrates on the notion of compound events as a means to describe situations of inefficient behavior. The second part is more practical and deals with the design of a real tool based on the compound-event method.

Chapter 2 provides an overview of the performance analysis of parallel applications. After discussing the drawbacks of traditional methods, an introduction to the problem of automating this task is given. Chapter 3 describes the method of using compound events to automatically detect inefficient behavior in event traces and how the method is applied to MPI, OpenMP, and hybrid applications. The design of an automatic performance-tool prototype based on the compound-event method is presented in Chapter 4. Here, issues such as event-trace generation, abstraction mechanisms, visualization of performance behavior, and extension mechanisms are discussed. Particular emphasis is put on the representation of performance behavior in a multidimensional data structure. To demonstrate that the performance problems addressed here are of practical relevance and that they can be easily

9

located using the present approach, the prototype is applied to four real-world test cases in Chapter 5. To draw a larger picture of research in the field and to distinguish the approach presented here from others, Chapter 6 contains a survey of related work. Finally, Chapter 7 summarizes the thesis research and comments on future work in automatic performance analysis.

## Chapter 2

## **Automatic Performance Analysis**

This chapter gives an introduction to the performance analysis of parallel applications and to the problem of automating this task. Reasons for the existence of complex performance behavior in parallel systems are reviewed. The performance indices and bounds used to quantify performance behavior are defined. A general model of the performance analysis process is then presented along with a survey of different kinds of performance data used in this process. Finally, the concept of a property-oriented performance space is introduced as the foundation of an automated analysis process that can overcome some of the current limitations in performance-analysis methods.

#### 2.1 Complexity in Parallel Systems

The complexity in current parallel systems is a result of the interfaces and interactions between different functional layers:

- Application

- Parallel programming interface

- Operating system

- Hardware

The hardware of today's modern parallel architectures combines sophisticated processor architectures together with multi-layered memory hierarchies and advanced network technologies. The operating system makes the hardware resources accessible to applications through mechanisms, such as process management, memory management, and IO. The parallel programming interface defines the way parallelism is presented to the programmer

and how parallelism is enabled in the system. It comprises compilers, run-time systems, and parallel libraries including those that encapsulate complicated communication mechanisms among the different processors. Finally, the application itself maps structures of the application domain to constructs of the programming language and the parallel programming interface. For this reason, it may need intricate data distribution strategies and associated communication patterns. Often, the understanding of these mutual relations may be further complicated as a result of compiler optimizations that create a distorted picture of the application's source code.

In addition to the complexity within single layers of a parallel system, there is a complexity in the interactions among different layers. For example, an action in one layer may trigger an action in a lower layer or may be a reaction on behalf of an event occurring in a lower layer. For this reason, there are long and interrelated sequences of actions and their (side) effects in parallel systems.

The complexity of single layers as well as the causal connections between different layers of parallel systems are the reason for complex performance behavior and the limited ability of application developers to understand inefficiency in their programs.

#### 2.2 Performance Indices and Bounds

Assessment of a system's performance requires an appropriate measure for drawing a comparison among different systems. Malony [51] identifies three quantitative performance indices for evaluating computer systems: *productivity* (i.e. throughput), *responsiveness* (i.e., turnaround or response time), and *utilization*. In the context of analyzing a parallel application's performance, responsiveness is the index of choice. Whenever an application's performance is classified as good, it has a satisfactory response time. For the non-interactive applications considered here response time is equivalent to execution time.

Speedup expresses the performance of a parallel application in terms of the time necessary for its sequential execution. The speedup for a given number of processors n is defined as the quotient of sequential and parallel execution time:

$$speedup(n) := \frac{T_{sequential}}{T_{parallel}(n)}$$

In general, the speedup can never grow more than linearly and exceed the *ideal speedup* of n unless there are side effects of parallel execution. For example, modern parallel architectures with cache-based memory hierarchies can achieve superlinear speedup as a result of memory allocation effects. The parallel *efficiency* provides a measure of the actual degree of speedup in relation to the ideal speedup:

$$efficiency(n) := \frac{speedup(n)}{n}$$

Amdahl [1, 41] formulates an upper limit of *speedup* based on the sequential part of a program, that is, the fraction of workload  $\alpha$  that cannot be divided and distributed across multiple processors:

$$speedup(n) = \frac{n}{1 + (n-1)\alpha}$$

This is known as *Amdahl's law*. It implies that the best speedup that can be expected is upper bounded by  $\alpha$ . Amdahl's law is a fundamental relationship in parallel-performance analysis because it points to the central issue of *scalability*, which characterizes the dependence of performance on the number of processors and the degree of problem parallelism. One metric that has been proposed to quantify scalability as the size of the problem changes is *scaled speedup* [34].

Paying attention to hardware utilization is sometimes more appropriate to highlight performance losses. Riley and Gurd [67] derive their notion of performance bounds from the hardware's peak performance as the upper limit. In their view performance of an application can be judged "in terms of the resource utilization it achieves ... while performing useful computation (that which is strictly necessary to solve the application problem at hand)." Note that the restriction to useful computation ties hardware utilization to the speedup criterion.

#### 2.3 Performance Analysis Process

Once a parallel application is free of computational errors, its code usually needs to be optimized. This requires knowledge of which parts of the program are responsible for what kind of inefficient behavior. Performance analysis is the process of identifying those parts, exploring the reasons for their unsatisfactory performance, and quantifying their influence on the overall performance. The information gained through this process should suggest measures that could be taken to tune the application.

Performance analysis and tuning form a cycle that frequently has to be repeated many times until the performance reaches a satisfactory level. After that, the application is ready to run in production mode. Pancake [63] presents a conceptual framework that describes this cycle from the application developer's perspective in the form of five questions that must be answered to accomplish performance improvement:

- 1. *Identification*: Is there a performance problem? What are the symptoms?

- 2. *Localization*: At what point in execution is performance going wrong? What is causing the problem to occur?

- 3. *Repair*: What about the application must be changed to fix the problem? [Perform the repair.]

- 4. *Verification*: Did the "fix" improve the performance? [If not, optionally undo the repair, then go back to (2).]

- 5. Validation: Is there still a performance problem? [If so, return to (1).]

Note that the question of when the tuning cycle should end is nontrivial. How is the application developer able to determine whether the performance is satisfactory? Should the cycle continue until the performance comes close to theoretical bounds, such as ideal speedup or optimal hardware utilization? In practice, the cycle ends when the application developer either runs out of time or out of ideas. Sometimes, tradeoffs between different execution parameters impose further constraints on the decision about satisfactory performance.

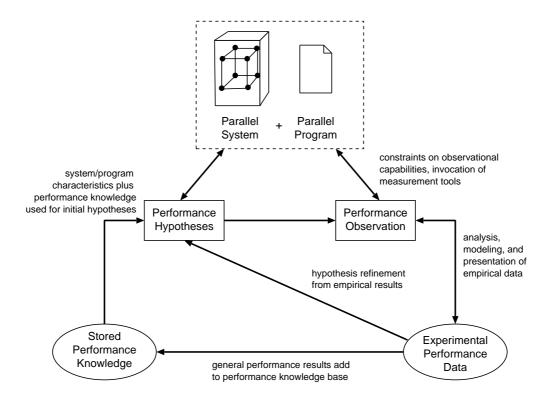

Malony [51] emphasizes the importance of the scientific method of "systematic testing of hypotheses through controlled measurement of observable phenomena, analysis of collected data, and modeling of empirical results" to the process of performance analysis and describes it in the context of experimental computer science. He delineates an idealized model of a parallel-performance—evaluation environment (Figure 2.1), which highlights the process of successive refinement of a hypothesis about performance behavior based on observation and accumulation of knowledge. This model is used here as a foundation for the following discussion of the performance analysis process, which corresponds to question 1 and 2 above.

Performance analysis starts with an initial *performance hypothesis* (e.g., too much time used for communication) based on system and program characteristics, which may include the results of any kind of static analysis. The hypothesis may be further supported by performance prediction based on runs under a different configuration, simulation, or a performance model of the application. Performance models play an important role especially in scalability analysis.

In response to the hypothesis, the experimental performance observation (e.g., monitoring communication) follows. The observation is constrained by certain observational capabilities and is usually performed with the support of programming tools. Since the run-time behavior of an application may be influenced by several different parameters, such as the number of allocated CPUs or the selected input-data set, the hypothesis also may refer to the performance as a function of one or more of these parameters. In this case, the observation may include a whole series of experiments. In addition, it may be feedback driven, that is, the performance data are analyzed online and influence the way the experiment is conducted.

The resulting *empirical performance data* are now subject to postprocessing, which may include matching them with a performance model and making them accessible through presentation. In this way, the data can be used to refine (or disprove) the initial hypothesis or contribute to the *stored performance knowledge* to be used in later hypotheses. Of course, hypothesis refinement includes both a more specialized identification (question

Figure 2.1: Idealized performance-analysis environment from [51].

1) and a more specialized localization (question 2). Depending on the results, the cycle of hypothesis creation and observation may begin again. The process ends when further hypothesis refinement becomes impossible due to a lack of new performance data.

#### 2.4 Performance Data

Performance data associate program entities with performance-related behavioral characteristics. Program entities are either static or dynamic. For example, source-code regions are static entities, whereas instances of those regions or paths within the dynamic call graph are dynamic entities. The characteristics are either qualitative or quantitative. Qualitative characterization refers to the occurrence or the order of certain events, whereas quantitative characterization is usually achieved by relating the number of certain event occurrences to intervals of program execution that represent certain program entities.

Performance data may differ in the level of abstraction they provide both with respect to the behavioral characteristics and with respect to the program entities they refer to. Characterization may occur, for example, either in terms of simple events, such as clock cycles, or in terms of more complex behavior, such as lock competition. Program entities may represent either simple pieces of source code or entities of the application domain. Observational performance data are usually generated on a low abstraction level and in a later step may be mapped to a higher abstraction level. Unmapped performance data are called *raw* performance data. The most common types of raw observational performance data are *profiles* and *event traces*.

Each type of performance data provides a certain view of the performance behavior. Usually the behavior is described along several dimensions, such as time and location. For this reason, the view defined by a certain type of performance data will be called a *performance space*.

#### 2.4.1 Profiles

Profiles map accumulated performance metrics (e.g., number of clock cycles, number of function calls, or number of cache misses) onto program entities. For example, a profile may contain the fraction of execution time spent in different functions of the program. Typical methods for profile generation are *sampling* and *instrumentation*.

Sampling is a statistical approach of periodically observing the program execution under the control of an interval timer and deriving performance metrics for program parts based on these observations. For instance, the GNU profiler gprof [24] determines the time fraction spent in different functions of the program based on sampling. Besides plain execution times, gprof estimates the execution time of a function when called from a distinct caller only. However, since the estimation is based on the number of calls from this caller, it can introduce significant inaccuracies in cases where the execution time is highly dependent on the call site.

In contrast to sampling, instrumentation inserts code directly into the program so that the program itself is able to trigger actions upon occurrences of certain program-level events (e.g., function calls). For instance, the TAU performance-measurement framework [69, 70] provides the ability to create execution-time and hardware-counter profiles based on routine-, basic-block-, and statement-level instrumentation.

Profiles are useful to generate a rough overview of an application's performance characteristics while introducing only limited perturbation of run-time behavior and requiring only moderate storage.

#### 2.4.2 Event Traces

Event traces are collections of individual run-time events recorded during program execution. The information recorded for an event includes at least a time stamp, the location

(e.g., the process or node) where the event happened, and the event type. Depending on the type, additional information may be supplied, such as the function name for function-call events. Message-event records typically contain details about the current message (e.g., the source or destination location and the message tag). In order to keep instrumentation simple, the information included in such an event record is usually restricted to the data available at the location where and at the moment when the event occurs.

Events are recorded at the point of their occurrence. For this reason, an application needs instrumentation to intercept and store away the desired events; that is, additional code needs to be inserted at program locations where their occurrence can be detected. To keep intrusion low, the event records are initially written into a memory buffer. Upon buffer overflow or program termination, the events are written to a file. Event traces generated independently for each location must be merged and sorted according to their time stamps. Systems that rely only on local clocks have to adjust the time stamps with respect to chronological displacements and clock drifts.

Limitations of event tracing may result from both the huge amount of data being produced and the perturbation of the program execution. This is true in particular when the density of recorded events is high. Because it is difficult to predict when this will occur, instrumentation has to be carried out very carefully and should be selective; that is, it should record only a small subset of all possible events.

The advantages of event traces result from the spatial and temporal relationships among individual events. This allows the reconstruction of an application's run-time behavior and thus can provide more detailed evidence of performance problems. In particular, the ability to visualize program execution using event-trace browsers have made tracing a widely accepted technique especially for message-passing programs.

For instance, VAMPIR [3] (Figure 2.2) provides a flexible display for event traces of message-passing programs. The VAMPIR event model defines event types for entering and leaving a region, for sending and receiving a message, and for executing a collective communication operation. VGV [38], the next-generation of VAMPIR, is based on an extended VAMPIR event model that supports hybrid applications as well.

## 2.5 Instrumentation

Instrumentation is the process of inserting extra code into a program to observe its execution or performance. Often instrumentation is used to make measurements for these purposes. Shende [69] distinguishes three dimensions of classifying instrumentation and measurement:

1. *How* are performance measurements defined and instrumentation alternatives chosen?

Figure 2.2: Event-trace visualization using VAMPIR.

- 2. *When* is performance instrumentation added and/or enabled (precompile time, compile time, link time, run time)?

- 3. *Where* in the program performance measurements are made (granularity and location)?

The first question addresses the selection of phenomena to be observed. It includes, for example, the choice among different metrics (e.g., time or cache misses).

The second question deals with the maintenance of the user's level of abstraction. Running a program requires moving it through several transformation steps: preprocessing, compilation, linkage, and execution or interpretation. Each transformation corresponds to a different level of representing a program's contents: source code, object code or library, executable or byte code, and run-time image. Although each level offers the opportunity to add instrumentation to the program, each level provides different information to be measured. In particular, the user's abstractions may be represented differently on each level. For example, the source code allows access to language-specific abstractions, which may be hidden in the binary representation. However, binary instrumentation of the runtime image allows instrumentation to be carried out at run time (sometimes referred to as dynamic instrumentation) and thus to be controlled by feed-back, which provides an excellent way of reducing intrusion. Note that both approaches may impose restrictions on the portability either across different languages or across different machines.

Programs exhibit a hierarchical structure consisting of different, often nested, elements, such as modules, functions, and statements. The third question classifies instrumentation according to the level within the program at which the instrumentation takes place, such as function entry and exit, statement, or instruction. The decision on the best places for

adding instrumentation is governed by the tradeoff between the demand for expressive performance data and the desire to avoid program perturbation.

As an example, the OPARI [57, 58] source-to-source translator instruments OpenMP constructs on the source-code level to capture performance-relevant events, such as entering a parallel region. Since OpenMP defines only the semantics of directives, not their implementation, there is no equally portable way of capturing those events on a different level. However, because OPARI supports all languages for which OpenMP is defined, it is still independent of a specific programming language. As a performance interface, OPARI defines only the types of events to be observed, the selection of information to be measured upon their occurrence is left to the user.

In contrast, Dyninst [11] is a C++ class library for instrumenting the run-time image of multiple processes running on the same machine. It allows the insertion of code snippets, including calls to dynamically loaded modules, at function entries and exits as well as before and after function calls. Because Dyninst requires neither recompiling nor restarting the application, it is well suited for feedback-driven online instrumentation. DPCL [16] is a dynamic instrumentation system based on Dyninst that is integrated with a parallel environment to provide simplified instrumentation of parallel applications.

The TAU [69, 70] performance-measurement framework overcomes the restrictions imposed by single-level instrumentation by allowing instrumentation at multiple levels. An instrumentation API allows the manual insertion of instrumented annotations in the source code. TAU also provides automatic preprocessor-level instrumentation by replacing calls to library routines with instrumented ones. In addition, TAU is able to automatically instrument the source code of C, C++, and Fortran programs using a preprocessor based on the PDT [50] toolkit. Besides compiler-level instrumentation based on a specific optimizing compiler, TAU supports the interception of MPI-specific events, such as message dispatch and receipt, using an interposition wrapper, which is linked between the application and the original MPI library. Finally, instrumentation using Dyninst allows the insertion of extra code at run time.

# 2.6 Performance Properties

Parallel applications may exhibit a large variety of different performance behaviors. For this reason, a general approach to performance analysis requires a terminology that can be used to refer to performance behavior independent of its specific characteristics.

Fahringer et al. [21] propose the notion of *performance properties* (e.g., load imbalance, communication, cache misses, redundant computations, etc.), which characterize a specific performance behavior of a program and can be checked by a set of conditions. Conditions

are associated with a *confidence* value (between 0 and 1) indicating the reliability in proving the existence of a performance property. In addition, for every performance property a *severity* measure is provided, whose magnitude specifies the importance of the property in relation to other properties. Note that a performance property does not necessarily denote negative, that is, inefficient behavior.

Fahringer et al. further define a *performance problem* as a performance property whose severity exceeds a user- or tool-defined threshold. The unique *performance bottleneck* is defined as the most severe performance property. If the bottleneck is not a performance problem, then the program's performance is considered to be acceptable and does not require any further tuning.

On the one hand, the concept of severity helps to distinguish between important and negligible performance problems during the performance tuning process. The purpose of the severity is to map arbitrarily complex behavior onto a general but simple metric, which provides the ability to draw comparisons with respect to the presence of very different performance properties in an application. For this reason, the notion of performance properties is a useful key concept for performance-analysis frameworks.

On the other hand, severity offers only a simplified view of the performance behavior. The severity arranges all performance properties in a linear order with the most severe (i.e., the bottleneck) on top. However, it does not take into account the various relationships, such as specialization and generalization, that may exist among different properties. If performance analysis were to pursue the goal of identifying the most worthwhile candidate property for optimization, it might be insufficient to sort performance properties only by one criterion while ignoring inter-property relationships.

For example, suppose a program has two and only two similar properties (e.g., overhead and synchronization overhead), of which one is more general (i.e., overhead) than the other one (i.e., synchronization overhead). Suppose also the general property's severity is higher, that is, it is the bottleneck. Note that the latter assumption is natural because the more general property includes the other one's behavior as a subset. Although the more general property has a higher severity because the total overhead is bigger than the overhead caused only by synchronization, in view of the inclusion relationship, the more specific property might be more interesting because it reveals more about its causes. Therefore, an application developer might pay more attention to this less general property, in particular, if synchronization overhead represents a major fraction of the total overhead.

Another criticism targets the definition of performance problems in terms of a threshold because the application or tool developer does not necessarily have an idea of a precise and useful threshold. Sometimes the developer just wants to spend a certain amount of time on optimization and tries to make the best achievements possible in that time. This might be another reason to look for more specific performance properties because their causes are more obvious compared to more general ones.

Finally, as already anticipated by Fahringer et al., the performance behavior is actually multi-dimensional. Fahringer and et al. express this in their parameterization of performance properties, which allows the consideration of a property with respect to only a specific source-code region or function call. Regarding these parameters as further dimensions leads to a very general representation of performance behavior.

A property-oriented performance space is defined as a multi-dimensional space with the performance property as its first dimension. The other dimensions represent static or dynamic entities related to an aspect of program execution a performance property may refer to. The definition of the remaining dimensions is very general and may include parts of the source code, dynamic run-time objects, or intervals of the execution time. The performance behavior in such a space is represented by data indicating the extent (i.e., severity) to which a certain performance property is present with respect to entities of the other dimensions. For example, a program may spend five percent of the overall execution time on a property synchronization overhead in function foo on process zero. Here, property synchronization overhead, function foo, and process zero are coordinates of a point in a property-oriented performance space, and the severity of that point is given as five percent. Similar to mapping single points onto a severity, it is possible to map sets of points onto a severity. For example, instead of considering the synchronization time for function foo, it should be possible to consider the synchronization time for the whole program. Thus, the severity is a mapping that maps a subset of the performance space onto a numeric value that makes it comparable to other subsets. The advantage of a property-oriented performance space is that it provides the ability to represent performance behavior along multiple dimensions in a data structure that is independent of the semantics of specific performance properties. In addition, the mapping of whole subsets instead of single points onto a severity value allows performance analysis on varying levels of detail.

In this manner, *performance problems* and *performance bottlenecks* can be considered as subsets of the performance space that are mapped onto a high severity and a very high severity, respectively. Of course, they are typically associated with a negative performance property, that is, one that denotes inefficient behavior.

Note that this characterization of both terms clearly refers not only to a class of behavior but also to the program entities that behavior is associated with. In the example above, the synchronization time in function *foo* and process *zero* might be considered as a performance problem. In addition, this characterization is very flexible because it allows inter-property relationships to be taken into account and a problem to be analyzed in the context of a more general problem.

## 2.7 Automatic Performance Analysis

Automating the process of performance analysis requires a model of the expected results of that process. In general, automation of performance analysis may cover all activities involved in that process. Riley and Gurd [67] roughly divide these into two categories:

- Gathering of data

- Search process

They describe the search process based on the notion of performance properties as a "systematic examination of performance data gathered for an application in order to identify performance properties in relation to regions of the application source code." The search process requires the performance properties to be defined in terms of conditions referring to performance data and includes query formulation and execution. The gathering of the necessary data requires experiment planning and execution management of instrumented runs of the program.

Justification for the above distinction can be found in the difference between raw (i.e., low-level) performance data and high-level performance data that present the performance behavior on a higher level of abstraction. The nature of raw performance data is determined by the nature of common monitoring techniques, which usually gather data in the form of profiles or event traces. Traditional performance tools support the search process mainly by providing low-level views of these performance data types. These views typically include textual or graphical - often interactive - displays, such as tables or bar charts of profiling information, time-line diagrams of event traces, and statistical analyses. The following tools exemplify common techniques of presenting profiles and event traces to the user.

The Apprentice [14] performance tool visualizes execution-time profiles of message-passing programs on the CRAY T3E in the form of bar-chart views (Figure 2.3). Apprentice shows time profiles on the program, routine, and basic-block level. Each bar is divided into sections by the use of a different color indicating a different type of activity, such as parallel processing, communication overhead, or IO. Starting from an arbitrary activity bar, the user can navigate through the call graph in both directions of a calling relationship to obtain profile information on subroutines as well as call sites.

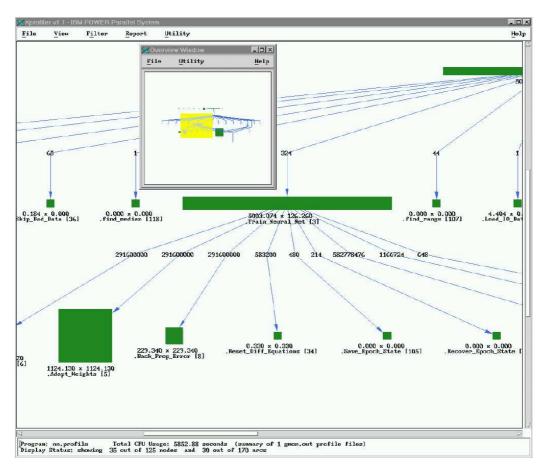

Xprofiler [42] is graphical front end for the GNU gprof profiler [24] with the ability to present gprof output as a call-graph diagram (Figure 2.4). Each node is displayed as rectangle, whose width and height represent the execution time including and excluding called routines, respectively. The arcs are labeled with the number of times a node was visited. In addition to the call-graph view, an annotated source-code view displays profiles for individual source lines.

VAMPIR [3] visualizes event traces of message-passing programs by showing a time line for each process (Figure 2.2) indicating its current execution state by color. Arrows point-

Figure 2.3: Apprentice profile browser.

ing from one time line to another time line represent point-to-point messages sent between processes, whereas connected lines covering multiple processes indicate collective communication. VAMPIR's zooming capability allows the user to examine the run-time behavior on an arbitrary level of temporal granularity. In addition to clicking on single items in the representation to obtain more detailed information, the user can look at statistics for the interval displayed.

The drawbacks of these low-level views are manifold. First, the user is confronted with a potentially large amount of data, which has to be searched manually for the presence of performance properties. This often includes manual comparison of different aspects of program behavior displayed in different unrelated views. Second, the views provided by current tools usually present program behavior in terms of low-level metrics that do not help the user in deciding whether performance improvement is possible, how performance can be improved, and whether an optimization effort would be worth the investment. Third, as a result of the multitude of different view options offered by some tools, a lot of training may be necessary before a tool can provide valuable assistance in performance analysis.

The search process as specified by Riley and Gurd describes a transformation of raw performance data into a two-dimensional performance space of performance property by source-code region. The difference between this performance space and low-level views is the characterization of performance behavior in terms of abstract performance properties that

Figure 2.4: Xprofiler call-graph diagram.

explain misbehavior on a higher level of abstraction.

However, there is no logical reason to restrict the performance space to only two dimensions. For example, the performance of a function might be poor only when called from a distinct caller or at a distinct location (e.g., process or node); or a performance property may evolve over time as the application moves among different execution phases. Therefore, it might be reasonable to consider the dynamic call graph or the execution phase as additional dimensions. In general, the search process can be regarded as the transformation of raw performance data into a general multi-dimensional high-level performance space that may be made up of various dimensions depending on the purpose of the analysis. Note that if raw performance data is thought of as being represented in a low-level performance space, the search process can be regarded as a transformation from a low-level space into a high-level space.

This thesis regards the automatic search process as an automatic transformation of low-level performance data into a multi-dimensional property-oriented performance space. The benefit of this viewpoint is a more general model of performance behavior that is able to

25

take into account the state of the program at the time a specific performance property is present. This may provide a better understanding of the preconditions that lead to a certain kind of behavior.

# **Chapter 3**

# **Specification of Performance Behavior**

This chapter presents a novel approach to analyzing performance properties of parallel applications based on event traces. It defines a framework for formally specifying compound events that characterize performance-relevant behavior. The framework allows the creation of abstract building blocks that represent concepts of the underlying programming model and therefore provide an easy means to specify complex compound events representing inefficient behavior. Using these specifications, it is possible to automatically locate inefficiencies in parallel applications by looking for occurrences of the corresponding compound events in event traces. This will be demonstrated for MPI, OpenMP, and their combination. Finally, to show that the approach is also suitable for existing performance-analysis frameworks, extensions are proposed to integrate it into ASL (APART Specification Language), a language for the formal specification of general performance properties.

### 3.1 Rationale

Effective automatic performance analysis requires formal methods for specifying performance properties that characterize a specific performance behavior. The strength of specifying inefficient behavior in terms of compound events stems from its ability to describe the behavior on a high level of abstraction directly related to the programming model. The resulting specifications can then serve as a basis for performance tools that are able to prove the presence of complex performance properties in a parallel application without user intervention.

The kind of performance data available has a great influence on the expressiveness of the performance properties that can be defined. Summary information, as collected by profiling tools, is sufficient to describe a multitude of frequently occurring performance properties. However, there are performance properties that are not visible in this kind of information. A more detailed view of a parallel application's behavior can be gained by using event traces because event traces preserve the spatial and temporal relationships among individual events, allowing the reconstruction of an application's dynamic behavior. By looking for compound events in an event trace, it is possible to prove that particular performance properties are present in an application.

A *compound event* representing a performance property is a set of primitive events, which are called its *constituents*. Compound events that relate to the programming model expose complex relationships among their constituents reflecting their model-relevant actions. For instance, sending a message and receiving it are interconnected by a relationship derived from the message-passing programming model. Because programming models differ in their operational semantics, it is difficult to devise a general formal representation of compound events that is powerful enough to express the complex compound events across all programming models.

To overcome this problem, the thesis identifies two categories of abstractions that can be used to provide programming-model–specific building blocks, on top of which a general specification of compound events is possible. The abstractions represent entities of the different programming models, such as MPI collective operations or OpenMP parallel-region constructs, and are useful for measuring their influence on performance behavior. The resulting specifications can be easily transformed into an appropriate detection algorithm.

# 3.2 System Observation Based on Events

Because a computer changes its state in discrete intervals (i.e., clock cycles), it is possible to model the dynamic behavior of any program execution as a sequence of atomic actions. The finest temporal granularity of actions happening in a computer system is a clock cycle. However, in practice, measuring the time of each action by software requires several clock cycles. Thus, the temporal resolution of atomic actions that can be observed is much lower.

An event characterizes an atomic action happening at a distinct location and at a distinct point in time. It is the smallest entity that can constitute the dynamic view of a parallel application. However, performance analysis is frequently interested in non-atomic activities (e.g., sending a message), which require a set of events to characterize them. Often a non-atomic activity is described in terms of its start or end events, which can usually be associated with a distinct point in time. The location of an event is determined by the location of the control flow causing the associated change in the state. The location of an event may be logical or physical (e.g., a process or a CPU, respectively).

Event tracing regards the execution of a program as a sequence of events representing actions relevant to the purpose of the observation. Therefore, the selection of event types to be observed defines the view of program execution an event trace can provide. An *event*

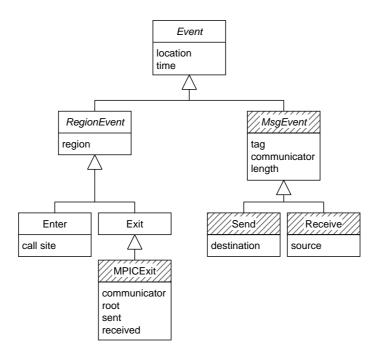

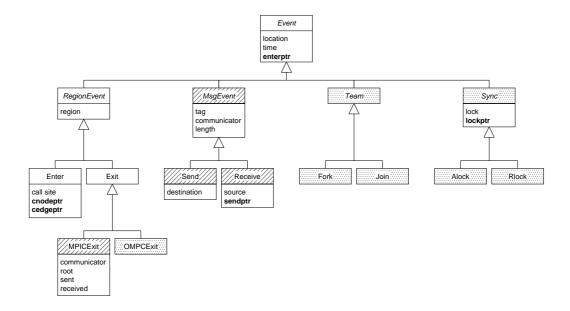

*model* defines the formal properties of that view. It comprises a set of event types with an associated set of attributes and constraints defining correct event ordering.