## Amorphous lanthanum lutetium oxide thin films as an alternative high- $\kappa$ gate dielectric

J. M. J. Lopes, <sup>a)</sup> M. Roeckerath, T. Heeg, E. Rije, J. Schubert, and S. Mantl *Institute for Bio- and Nanosystems (IBNI-IT), Research Center Jülich, D-52425 Jülich, Germany and Center of Nanoelectronic Systems for Information Technology, Research Center Jülich, D-52425 Jülich, Germany*

## V. V. Afanas'ev, S. Shamuilia, and A. Stesmans

Department of Physics, University of Leuven, Celestijnenlaan 200D, B-3001 Leuven, Belgium

## Y. Jia and D. G. Schlom

Department of Materials Science and Engineering, Pennsylvania State University, University Park, Pennsylvania 16802-5005

(Received 17 August 2006; accepted 8 October 2006; published online 27 November 2006)

Lanthanum lutetium oxide thin films were grown on (100) Si by pulsed laser deposition. Rutherford backscattering spectrometry, atomic force microscopy, x-ray diffraction, and x-ray reflectometry were employed to investigate the samples. The results indicate the growth of stoichiometric and smooth LaLuO<sub>3</sub> films that remain amorphous up to  $1000\,^{\circ}$ C. Internal photoemission and photoconductivity measurements show a band gap width of  $5.2\pm0.1\,$  eV and symmetrical conduction and valence band offsets of  $2.1\,$  eV. Capacitance and leakage current measurements reveal C-V curves with a small hysteresis, a dielectric constant of  $\approx$ 32, and low leakage current density levels. ©  $2006\,$  American Institute of Physics. [DOI: 10.1063/1.2393156]

The study of ultrathin gate dielectrics has recently gained great attention due to the technological need to replace SiO<sub>2</sub> films in metal-oxide-semiconductor field-effect transistors (MOSFETs). The scaling has led to MOSFETs with ultrashort physical gate lengths (<50 nm) and insulating SiO<sub>2</sub>-based films with thickness less than 1 nm. At such a thickness, these films suffer from excessively high leakage of charge carriers and poor reliability with respect to dielectric breakdown. Therefore, to overcome these limitations new gate dielectric materials with a higher dielectric constant must be developed to replace the SiO2. According to the International Technology Roadmap for Semiconductors,<sup>2</sup> the implementation of high- $\kappa$  gate dielectrics with a dielectric constant  $\kappa$  between 10 and 20 will be required by 2008, which will later be replaced by materials having a  $\kappa$  larger than 20, in order to meet both low leakage current density and performance requirements.

Ternary rare earth oxides (e.g., DyScO<sub>3</sub> and GdScO<sub>3</sub>) are emerging as promising candidates for high- $\kappa$  applications. As shown by Schlom and Haeni, single crystals of these oxides show  $\kappa$  values of 20-35 which were also observed for amorphous LaScO<sub>3</sub>, GdScO<sub>3</sub>, and DyScO<sub>3</sub> films deposited on silicon ( $\kappa$ =22–23).<sup>4,5</sup> In addition, these materials fulfill the requirements for large optical band gaps (5.6 eV) and band offsets (2-2.5 eV), while their amorphous phase is stable up to 1000 °C (for GdScO<sub>3</sub> and DyScO<sub>3</sub>).<sup>4,5</sup> Lanthanum lutetium oxide (LaLuO<sub>3</sub>), as a member of this class of ternary oxides, is predicted to have similar properties.<sup>3,7</sup> Experimental data related to high- $\kappa$  gate applications of amorphous LaLuO3 films are, however, still not available. In this letter, we present the results of a systematic study on the microstructural and electrical properties of amorphous LaLuO<sub>3</sub> thin films, deposited on silicon substrates by means of pulsed laser deposition (PLD).

LaLuO<sub>3</sub> films were deposited by PLD using a stoichiometric ceramic target. The target was made by milling a stoichiometric mixture of Lu<sub>2</sub>O<sub>3</sub> (Alfa Aesar, 99.99%) and La<sub>2</sub>O<sub>3</sub> (Alfa Aesar, 99.999%) powders with a molar ratio of 1:1. The ground powder was dried and then fired at 1300 °C in air for 12 h. After regrinding, the powder was pressed with a uniaxial press (3 tons). The pellets were then sintered at 1500 °C in air for 10 h. To increase the density of the target material it was subsequently sintered at 1600 °C in air for 12 h.

RCA cleaned p- and n-type (100) Si wafers cut in 1  $\times$  1 cm<sup>2</sup> pieces were used as substrates. Here it is important to remark that after RCA cleaning a 1-1.5 nm thick SiO<sub>2</sub> layer is expected on the Si surface. The deposition process took place at a temperature of 450 °C in a  $2 \times 10^{-3}$  mbar O<sub>2</sub> ambient. Layers with thicknesses varying from 6 to 60 nm were grown, as determined by x-ray reflectometry (XRR). After deposition, the films were investigated with respect to their composition, surface morphology, and thermal stability by means of Rutherford backscattering spectrometry (RBS), atomic force microscopy (AFM), and x-ray diffraction (XRD). A combination of internal photoemission (IPE) and photoconductivity (PC) measurements was employed to determine the band gap width of the oxide and the conduction and valence band (CB, VB) offsets at the Si/high- $\kappa$ interface.6

For the electrical characterization of the films, capacitor stacks were prepared. 70 nm thick Pt top contacts with an area of  $245 \times 245~\mu\text{m}^2$  were deposited by electron beam evaporation through a shadow mask. The Ohmic backside contact was made by deposition of 120 nm Al followed by a forming gas annealing (90% N<sub>2</sub>+10% H<sub>2</sub>) at 450 °C for 10 min. This treatment improved the backside Al contact and the interface between the high- $\kappa$  oxide and the silicon. The capacitor stacks were investigated using an impedance ana-

a) Electronic mail: j.m.lopes@fz-juelich.de

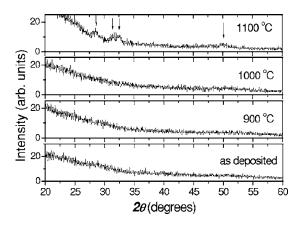

FIG. 1. XRD patterns of an 11 nm thick LaLuO $_3$  film deposited on (100) Si after annealing in 1 atm of  $N_2$  at different temperatures for 10 s.

lyzer (HP 4192A) for capacitance-voltage (*C-V*) curves and a semiconductor parameter analyzer (HP 4155B) for current-voltage (*I-V*) measurements.

The RBS measurements (not shown) reveal a stoichiometry close to the nominal composition of LaLuO<sub>3</sub>, presenting a La:Lu ratio of about 1:1.1. From the correlation between the RBS (atomic coverage per unit area) and the XRR data (physical thickness), a density of the films of  $\approx$ 88% of the single crystalline density is deduced.

Additionally, the LaLuO<sub>3</sub> films exhibit a smooth surface morphology, as determined by AFM over a  $2 \times 2 \ \mu m^2$  scan area (not shown). Films with thicknesses up to 12 nm show a root mean square surface roughness  $\leq$ 0.2 nm and a peak-to-valley roughness of about 1.5 nm. The roughness of even thicker layers (from 20 to 60 nm) does not exceed 0.4 and 2.5 nm, respectively.

In order to study the thermal stability of the LaLuO<sub>3</sub>, rapid thermal annealing in ultrapure N<sub>2</sub> (99.999%) was performed at atmospheric pressure and temperatures between 700 and 1200 °C for 10 s. Figure 1 shows the XRD patterns for 11 nm thick films as a function of temperature. The LaLuO<sub>3</sub> remains amorphous up to 1000 °C. At 1100 °C crystallization is observed as indicated by the arrows. The peaks seen in the spectrum do not fit to the available data for crystalline La<sub>2</sub>O<sub>3</sub>, Lu<sub>2</sub>O<sub>3</sub>, LaLuO<sub>3</sub>, or related silicates <sup>10</sup> and therefore more investigation is needed to identify the crystalline phases present after annealing at 1100 °C. The crystallization temperature is comparable to that observed for rare earth scandate (GdScO<sub>3</sub> and DyScO<sub>3</sub>) films, also grown by the PLD technique, however, significantly higher than that observed for HfO<sub>2</sub> films. <sup>11</sup>

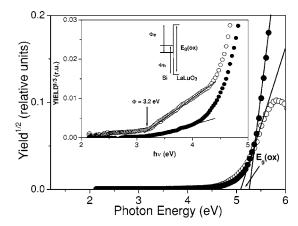

IPE and PC experiments were performed using MOS capacitors fabricated by evaporation of semitransparent (15 nm thick) Au electrodes of 0.5 mm<sup>2</sup> area using an experimental arrangement described earlier. The quantum yield of IPE or PC was defined as the photocurrent, normalized to the incident photon flux. The square root of this quantum yield is shown in Fig. 2 as a function of photon energy  $h\nu$ . The open/closed symbols correspond to data taken under positive or negative bias on the metal, respectively, with the average strength of the electric field in the oxide being about 2 MV/cm. High values of the yield are observed at high photon energies ( $h\nu > 5.5$  eV) for both bias polarities, suggesting excitation of intrinsic PC of the oxide. To determine the PC threshold energy, corresponding to the insulator band gap  $E_g(ox)$ , the data were plotted in  $Y^{1/2}$ - $h\nu$  coordinates, as

FIG. 2. Determination of the spectral thresholds using the  $Y^{1/2}$ - $h\nu$  plots of PC current measured on Si MOS capacitors with 22 nm thick LaLuO<sub>3</sub> insulator. Open and closed symbols correspond to positive and negative biases on the electrode, respectively, with the average strength of the electric field in the oxide being 2 MV/cm. The inset illustrates determination of IPE thresholds from the  $Y^{1/3}$ - $h\nu$  plot (Ref. 12) and the interface band alignment scheme where the arrows indicate the spectral threshold energies found. Lines guide the eyes.

shown in Fig. 2. By extrapolating the yield to zero, the PC threshold of  $E_o(ox) = 5.2 + 0.1$  eV is found. There is also a 0.7 eV wide "tail" of subthreshold PC consistent with earlier observations for rare earth scandate insulators. The IPE of electrons from the VB of Si into the oxide CB is observed under positive metal bias. The threshold  $\Phi_a$  was determined using the  $Y^{1/3}$ - $h\nu$  plot<sup>12</sup> as illustrated in the inset in Fig. 2. Extrapolation to zero yield results in the threshold value of  $\Phi_e = 3.2 \pm 0.1$  eV. Assignment of the spectral threshold observed in the curve measured with the metal biased negatively at  $\Phi$ =3.2±0.1 eV is not straightforward because the photocurrent might arise both from hole IPE from the CB of Si into the oxide VB and from electron IPE from the Au electrode. Nevertheless, the hole IPE interpretation seems to be the feasible one because the oxide band gap width calculated using the measured IPE barrier values as  $E_{\rho}(ox) = \Phi_{\rho}$  $+\Phi_h - E_g(\text{Si}) = 5.3 \text{ eV}$  (see inset in Fig. 2) coincides, within the measurement accuracy of  $\pm 0.1$  eV, with the earlier indicated PC result  $E_g(ox) = 5.2$  eV. Should this interpretation be correct, both the CB and VB offsets at the (100)Si/LaLuO<sub>3</sub> interface are equal to 2.1 eV, i.e., both are sufficiently high to prevent the injection of holes and electrons into the oxide.

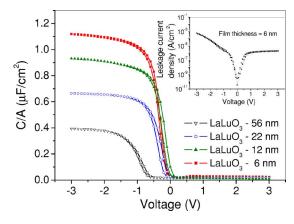

FIG. 3. (Color online) C-V curves for the Pt/LaLuO $_3$ /p-Si capacitor stacks measured at a frequency of 100 kHz. The inset shows the I-V curve of a p  $E_g$ (ox), the data were plotted in  $Y^{1/2}$ - $h\nu$  coordinates, as Downloaded 21 Dec 2006 to 134.94.122.39. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

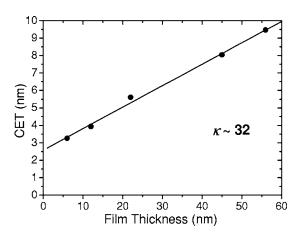

FIG. 4. CET plotted as a function of the film thickness. The  $\kappa$  value was calculated from the slope of the linear fit.

Figure 3 shows the C-V measurements for LaLuO<sub>3</sub> films with different thicknesses deposited on p-type silicon. The curves were recorded under forward and reverse bias sweeps at a frequency of 100 kHz and a hold time of 3 s for each measuring point. Curves with small hysteresis and free of humps and irregularities were achieved. Also observed is a flatband voltage shift reduction with decreasing LaLuO<sub>3</sub> thickness, which can be related to the lower number of charge traps expected for thinner films. The inset in Fig. 3 shows an I-V curve recorded for the Pt/LaLuO<sub>3</sub>/p-Si capacitor stack containing a 6 nm thick LaLuO<sub>3</sub> film. A hold time of 20 s was chosen for each measuring point in order to eliminate all relaxation processes within this time period. A low leakage current density of  $6 \times 10^{-5}$  A/cm<sup>2</sup> was achieved at a voltage of -2 V. For thicker films (not shown), this value ranges between 10<sup>-8</sup> and 10<sup>-10</sup> A/cm<sup>2</sup>, which is close to the detection limit of the measuring system for the contact pad size used.

Figure 4 shows the capacitance equivalent thickness (CET) plotted as a function of the physical thickness determined by XRR measurements. The CET values were calculated from the capacitance in the accumulation regime at a voltage of -2 V. In contrast to the equivalent oxide thickness, the CET does not take quantum mechanical effects into account. From the slope of the linear fit, it is possible to calculate the dielectric constant ( $\kappa$ ) of the films excluding the contribution of a lower- $\kappa$  interfacial layer. The  $\kappa$  value obtained for the LaLuO<sub>3</sub> films is  $\approx$ 32, which is higher than those obtained for other amorphous rare earth oxide films <sup>4,5</sup> and amorphous HfO<sub>2</sub> films <sup>13</sup> exhibiting  $\kappa$ =22–23. The inter-

section between the CET axis and the linear fit at 2.6 nm indicates the existence of a lower- $\kappa$  interfacial layer between the LaLuO<sub>3</sub> film and the Si substrate. A detailed investigation on the formation of such a layer and its reduction in thickness is currently in progress.

In summary, we have demonstrated that amorphous lanthanum lutetium oxide is a promising alternative high- $\kappa$  gate dielectric candidate. Thin films deposited on Si substrates present a high thermal stability up to  $1000\,^{\circ}$ C, which fulfills the requirement for complementary MOS processing. Additionally, a large band gap width  $(5.2\pm0.1~\text{eV})$  and symmetrical band offsets (2.1~eV) were observed for this material. The electrical characterization reveals good C-V behavior, a low leakage current density, and a  $\kappa$  value of about 32, which is larger than those previously determined for other alternative high- $\kappa$  amorphous oxides  $(\kappa=22-23)$ .

One of the authors (J.M.J.L.) gratefully acknowledges the Alexander von Humboldt Foundation for a research fellowship. The authors thank P. Meuffels for postannealing the target material.

<sup>1</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **89**, 5243 (2001).

<sup>2</sup>International Technology Roadmap for Semiconductors: 2005 (Semiconductor Industry Association, San Jose, CA, 2005).

<sup>3</sup>D. G. Schlom and J. H. Haeni, MRS Bull. **27**, 198 (2002).

<sup>4</sup>M. Wagner, T. Heeg, J. Schubert, St. Lenk, S. Mantl, C. Zhao, M. Caymax, and S. De Gent, Appl. Phys. Lett. **88**, 172901 (2006).

<sup>5</sup>C. Zhao, T. Witters, B. Brijs, H. Bender, O. Richard, M. Caymax, T. Heeg, J. Schubert, V. V. Afanas'ev, A. Stesmans, and D. G. Schlom, Appl. Phys. Lett. 86, 132903 (2005).

<sup>6</sup>V. V. Afanas'ev, A. Stesmans, C. Zhao, M. Caymax, T. Heeg, J. Schubert, Y. Jia, D. G. Schlom, and G. Lucovsky, Appl. Phys. Lett. **85**, 5917 (2004).

<sup>7</sup>D. G. Schlom, C. A. Billman, J. H. Haeni, J. Lettieri, P. H. Tan, R. R. M. Held, S. Völk, and K. J. Hubbard, in *Thin Films and Heterostructures for Oxide Electronics*, 1st ed., edited by S. B. Ogale (Springer, New York, 2006), p. 31.

<sup>8</sup>International Centre for Diffraction Data, Powder Diffraction File Database Sets 1-45, Data Nos. 05-0602, 22-0369, 22-0641, 33-0716, 40-1279, 40-1281, and 12-0728 (unpublished).

<sup>9</sup>K. L. Ovanesyan, A. G. Petrosyan, G. O. Shirinyan, C. Pedrini, and L. Zhang, Opt. Mater. 10, 291 (1998).

<sup>10</sup>Inorganic Crystal Structure Database, available at http://icsdweb.fiz-karlsruhe.de

<sup>11</sup>K. Hyoungsub, P. C. McIntyre, and K. C. Saraswat, Appl. Phys. Lett. 82, 106 (2003).

<sup>12</sup>R. J. Powell, J. Appl. Phys. **41**, 2424 (1970).

<sup>13</sup>Y.-S. Lin, R. Puthenkovilakam, and J. P. Chang, Appl. Phys. Lett. 81, 2041 (2002).

L. F. Edge, D. G. Schlom, P. Sivasubramani, R. M. Wallace, B. Holländer, and J. Schubert, Appl. Phys. Lett. 88, 112907 (2006).