### FORSCHUNGSZENTRUM JÜLICH GmbH

Zentralinstitut für Angewandte Mathematik D-52425 Jülich, Tel. (02461) 61-6402

### Interner Bericht

# Einsatz von FPGAs für molekulardynamische Rechnungen

Annika Schiller

FZJ-ZAM-IB-2007-06

März 2007

(letzte Änderung: 27.03.2007)

# Inhaltsverzeichnis

| 1 | Einl | eitung      |                                                  | 1  |

|---|------|-------------|--------------------------------------------------|----|

| 2 | Gru  | ndlagen     | n der Molekulardynamik                           | 3  |

|   | 2.1  | Physik      | alische und mathematische Grundlagen             | 3  |

|   | 2.2  | System      | n- und Teilchenmodelle                           | 5  |

|   |      | 2.2.1       | Periodische und nicht-periodische Systeme        | 5  |

|   |      | 2.2.2       | Wechselwirkungspotentiale                        | 6  |

|   | 2.3  | Nachba      | arschaftslisten                                  | 8  |

|   | 2.4  | MD-Si       | imulation                                        | 10 |

|   |      | 2.4.1       | Vorteile der Computersimulation                  | 11 |

|   |      | 2.4.2       | Durchführung einer MD-Simulation                 | 11 |

|   |      | 2.4.3       | Grenzen der Computersimulation                   | 13 |

|   |      | 2.4.4       | Methoden zur Beschleunigung einer MD-Simulation  | 14 |

| 3 | FPG  | <b>A</b>    |                                                  | 15 |

| _ | 3.1  |             | ndungsgebiete                                    | 15 |

|   | 3.2  |             | neine Architektur von FPGAs                      | 17 |

|   |      | 3.2.1       | FPGAs der Virtex-Serie                           | 18 |

|   |      | 3.2.2       | Konfigurierbare Logikblöcke (CLBs)               | 18 |

|   | 3.3  |             | mmierung von FPGAs                               | 19 |

|   |      | 3.3.1       | Unterschied Hardware- und Softwareprogrammierung | 20 |

|   |      | 3.3.2       | Hardwareentwicklungsablauf                       | 21 |

|   | 3.4  | Rekon       | figurierbare Koprozessoren                       | 23 |

|   |      | 3.4.1       | PROGRAPE-4                                       | 24 |

|   |      | 3.4.2       | Entwicklung eines FPGA-basierten Rechners        | 26 |

| 4 | PGF  | <b>&gt;</b> |                                                  | 28 |

| • | 4.1  |             | -Programmierung mit PGR                          | 29 |

|   | 7.1  | 4.1.1       | Entwicklungsablauf in PGR                        | 29 |

|   |      | 4.1.2       | Parametrisierte arithmetische Module             | 30 |

|   | 4.2  |             | eschreibungssprache PGDL                         | 31 |

|   | 7.2  | 4.2.1       | Das API-Modell                                   | 32 |

|   |      | 4.2.2       | Programmstruktur                                 | 32 |

|   |      | 7,2,2       | 1 Togrammstruktur                                | 32 |

| 5 |      | _           | n zum Einsatz von FPGAs                          | 35 |

|   | 5.1  |             | ation                                            | 36 |

|   | 5.2  |             | rd-Jones-FPGA-Design                             | 36 |

|   |      | 5.2.1       | Kraftberechnung in Fortran                       | 37 |

|   |      | 5.2.2       | FPGA-Implementierung                             | 38 |

|              |        | 5.2.3   | Ergebnisse                                          | 40 |

|--------------|--------|---------|-----------------------------------------------------|----|

| 6            | Link   | ed-Cell | l-List-FPGA-Design                                  | 45 |

|              | 6.1    | Der Li  | nked-Cell-List-Algorithmus                          | 45 |

|              |        | 6.1.1   | Vor- und Nachteile des Linked-Cell-List-Algorithmus | 47 |

|              | 6.2    |         | matik                                               | 48 |

|              | 6.3    | Konze   | pt                                                  | 48 |

|              | 6.4    | -       | nentierung                                          | 49 |

|              |        | 6.4.1   | Hardwaredesign                                      | 50 |

|              |        | 6.4.2   | Softwaredesign                                      | 52 |

|              | 6.5    | Ergebn  | nisse                                               | 54 |

|              |        | 6.5.1   | Ausblick                                            | 55 |

|              | 6.6    |         |                                                     | 56 |

| 7            | Zusa   | ımmenf  | fassung und Ausblick                                | 57 |

| Gl           | ossar  |         |                                                     | 59 |

| Li           | teratu | rverzei | ichnis                                              | 65 |

| Ar           | nhang  |         |                                                     | 65 |

|              | Α      | Parame  | etrisierte Arithmetische Module                     | 66 |

| B Quelltexte |        | Quellte | exte                                                | 68 |

|              |        | B.1     | PGDL-Code zum Gravitationspotential                 | 68 |

|              |        | B.2     | PGDL-Code zum Lennard-Jones-Potential               | 69 |

|              |        | B.3     | PGDL-Code zum Linked-Cell-List-Algorithmus          | 70 |

|              |        |         |                                                     |    |

|              |        | B.4     | Fortran-Quelltext zum Linked-Cell-List-FPGA-Design  | 72 |

# Abbildungsverzeichnis

| 2.1 | Wechselwirkungen in einem System mit offenen Randern                      | 3  |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | System mit periodischen Randbedingungen                                   | 6  |

| 2.3 | Wechselwirkungen nach der Minimum Image Convention                        | 6  |

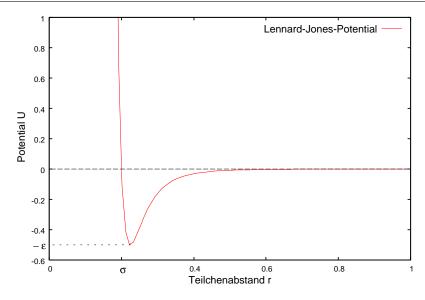

| 2.4 | Lennard-Jones-Potential                                                   | 7  |

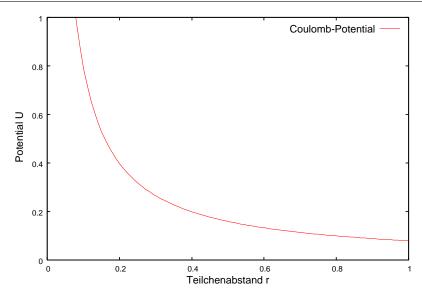

| 2.5 | Coulomb-Potential                                                         | 8  |

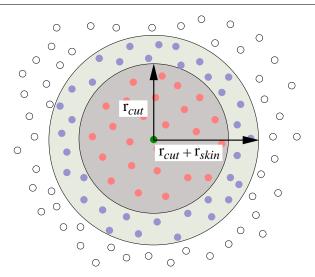

| 2.6 | Prinzip der Verlet-Listen                                                 | ç  |

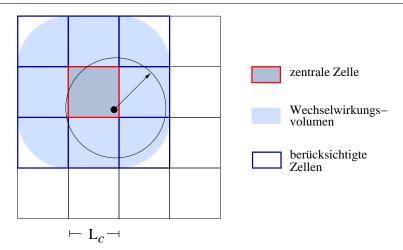

| 2.7 | Prinzip der Linked-Cell-Listen                                            | 10 |

| 3.1 | Foto eines FPGAs                                                          | 17 |

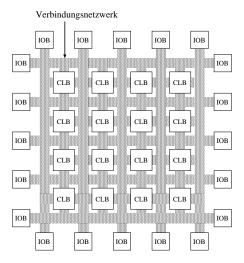

| 3.2 | Architektur eines FPGAs                                                   | 17 |

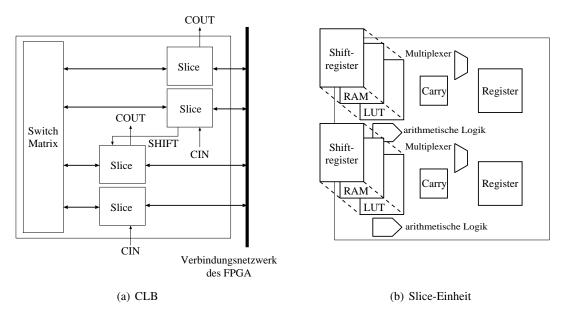

| 3.3 | Struktur eines CLBs                                                       | 19 |

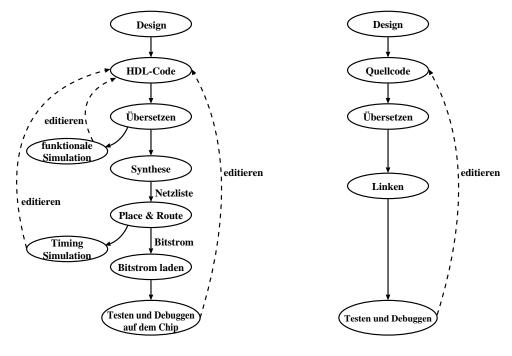

| 3.4 | Ablauf von Hardware- und Softwareentwicklung                              | 20 |

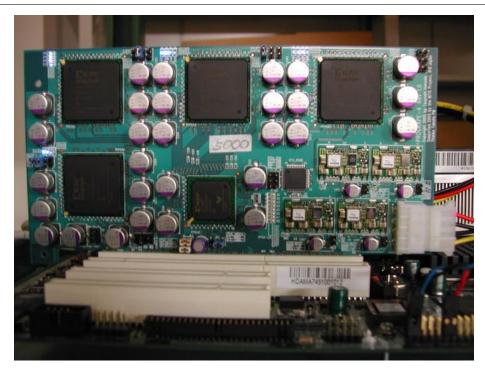

| 3.5 | Foto des PROGRAPE-4-Boards                                                | 24 |

| 3.6 | Architektur des PROGRAPE-4-Boards                                         | 25 |

| 3.7 | Entwicklungsablauf eines FPGA-basierten Rechners                          | 26 |

| 4.1 | Entwicklungsablauf eines FPGA-basierten Rechners mit PGR                  | 29 |

| 4.2 | Blockdiagramm eines Pipelineprozessors                                    | 31 |

| 4.3 | Blockdiagramm zu Formel 4.2                                               | 34 |

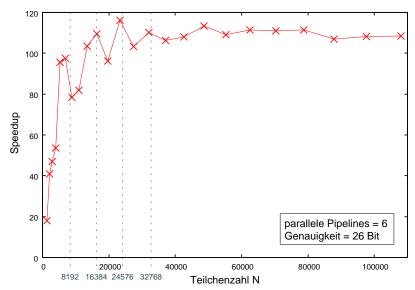

| 5.1 | Speedup des Lennard-Jones-Potentials in Abhängigkeit von der Teilchenzahl | 42 |

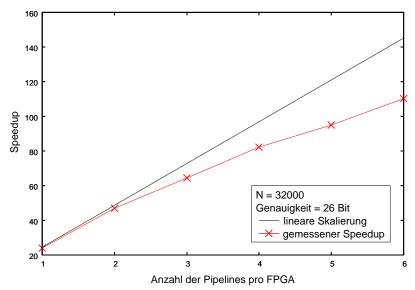

| 5.2 | Speedup des Lennard-Jones-Potentials in Abhängigkeit von der Pipelinezahl | 43 |

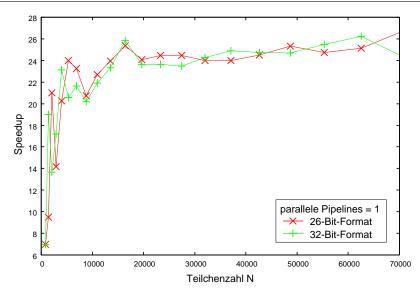

| 5.3 | Speedup des Lennard-Jones-Potentials für verschiedene Bitbreiten          | 44 |

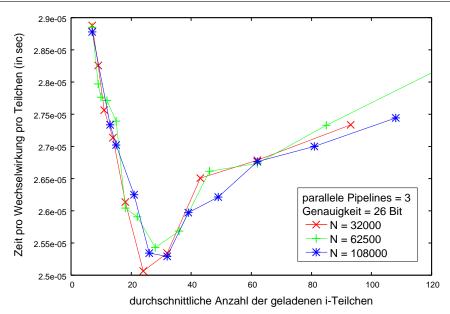

| 6 1 | Zeit pro Wechselwirkung beim Linked-Cell-List-FPGA-Design                 | 55 |

### **Abstract**

### Einsatz von FPGAs für molekulardynamische Rechnungen

Die Simulation komplexer Vielteilchensysteme in vielen Bereichen der Wissenschaft wird immer wichtiger bei der Vorhersage und Analyse physikalischer Phänomene. Um möglichst große Systeme über einen längeren Zeitraum hinweg simulieren zu können, werden neben der Entwicklung spezieller Algorithmen verstärkt auch spezialisierte Computerarchitekturen eingesetzt. Mittels solcher Architekturen lassen sich bestimmte Operationen extrem schnell berechnen. Durch ihre fest codierte Hardware sind sie jedoch nicht für jede Problemklasse effizient einsetzbar. Eine Alternative bieten FPGA-basierte Computerarchitekturen. Diese lassen sich jederzeit umkonfigurieren und können somit auf verschiedene Problemklassen optimiert werden

In Rahmen dieser Diplomarbeit wird das FPGA-Board PROGRAPE-4 für molekulardynamische Berechnungen eingesetzt. Zur Konfigurierung des Boards wird die Software PGR verwendet. Es wird zunächst ein FPGA-Design zur Kräfteberechnung mittels des Lennard-Jones-Potentials entwickelt und auf ein offenes System angewendet. Dadurch lässt sich ein erheblicher Leistungsgewinn erzielen. Dieses Problem hat eine Komplexität von  $O(N^2)$ , da für die Berechnung der Kräfte alle Teilchen des Systems mit einbezogen werden. Der Linked-Cell-List-Algorithmus optimiert die Wechselwirkungsberechnung für das kurzreichweitige Lennard-Jones-Potential auf eine Komplexität von O(N). Um zu untersuchen, ob sich das PROGRAPE-4-Board auch für diesen Algorithmus effizient einsetzen lässt, wird hierzu ein passendes FPGA-Design entwickelt.

### **Use of FPGAs for Molecular Dynamics Calculations**

The simulation of complex many-body systems becomes increasingly important for the prognosis and analysis of physical phenomena in many fields of science. Further to the development of special algorithms, the use of specialized computer architectures to simulate larger systems over a longer period of time gained momentum. Using such specialized computer architectures, certain operations can be computed extremly fast. However, they are not usable for all classes of problems equally efficient, because of their hard coded logic. FPGA based computer architectures are an alternative to these highly specialized systems. They can be reconfigured at any time and optimized for different classes of problems.

In this diploma thesis, the FPGA board PROGRAPE-4 is used for molecular dynamics calculations. To configure the board, the software PGR is used. At first, an FPGA design is developed to calculate the forces in an open system via a Lennard-Jones potential. Thereby the performance can be increased significantly. Due to the fact that for the calculation of the forces all particles in the system have to be considered, this problem has a complexity of  $O(N^2)$ . The Linked-Cell-List algorithm optimizes the calculation of the forces for the short ranged Lennard-Jones potential to a complexity of O(N). To determine if the PROGRAPE-4 board can be used for this algorithm with similar efficiency, a suitable FPGA design is developed.

# **Kapitel 1**

# **Einleitung**

Die Simulation komplexer Vielteilchensysteme in vielen Bereichen der Wissenschaft wird immer wichtiger bei der Vorhersage und Analyse physikalischer Phänomene. Computersimulationen benötigen jedoch einen enormen Bedarf an Rechenleistung. Um möglichst große Systeme über einen längeren Zeitraum hinweg simulieren zu können, ist die effiziente Implementierung der Programme, sowie die Entwicklung spezieller Algorithmen von entscheidender Bedeutung.

Der Einsatz leistungsfähiger Computersysteme, wie z. B. Supercomputer, trägt ebenfalls zur Beschleunigung der Computersimulation bei. In diesem Zusammenhang werden verstärkt auch spezialisierte Computerarchitekturen benutzt. Mittels solcher Architekturen lassen sich bestimmte Operationen extrem schnell berechnen. Sie rechnen zudem massiv parallel. Durch ihre fest codierte Hardware sind sie jedoch nicht auf jede Problemklasse optimiert.

Eine Alternative zu spezialisierten Computerarchitekturen bietet der Einsatz rekonfigurierbarer Hardware, wie FPGAs (*Field Programmable Gate Array*). Ein FPGA besteht aus einzelnen Funktionsblöcken, die in einer Matrix angeordnet sind und über ein Verbindungsnetzwerk miteinander verbunden sind. Durch Programmierung der Funktionsblöcke lässt sich mit einem FPGA, im Rahmen der verfügbaren Logik, eine große Menge digitalelektronischer Schaltungen realisieren. FPGAbasierte Computerarchitekturen lassen sich jederzeit umkonfigurieren und können somit auf unterschiedliche Probleme optimiert werden.

Im Rahmen dieser Arbeit sollen molekulardynamische Rechnungen auf FPGAs durchgeführt werden. Als Motivation dazu dient eine Projektarbeit, in der ein FPGA-Board zur Berechnung von Gravitationskräften eingesetzt wurde. Die Berechnung konnte um einen Faktor 35 beschleunigt werden. Das Gravitationspotential ist ein langreichweitiges Potential. Es soll untersucht werden, ob sich das FPGA-Board auch für kurzreichweitige Wechselwirkungspotentiale, wie dem Lennard-Jones-Potential, einsetzen lässt. Ein besonderes Augenmerk wird dabei auf den Linked-Cell-List-Algorithmus gelegt. Mit diesem Algorithmus wird mittels Nachbarschaftslisten die Komplexität der Kräfteberechnung von  $O(N^2)$  auf O(N) reduziert.

Für den Linked-Cell-List-Algorithmus soll ein FPGA-Design entwickelt werden. Als Hardware steht dazu das PROGRAPE-4-Board am Astronomischen Recheninstitut (ARI) in Heidelberg zur Verfügung. Das Board wird mit der Software PGR (*Processors Generator for Reconfigurable Systems*) programmiert. Zur Entwicklung eines solchen FPGA-Designs muss ein Hardwaredesign entworfen werden und die Softwareimplementierung des Linked-Cell-List-Algorithmus dementsprechend umgeschrieben werden.

Im folgenden Kapitel werden zunächst einige Grundlagen zu den Methoden der Molekulardynamik (MD) und zur Vorgehensweise einer MD-Simulation erläutert. Kapitel 3 liefert eine Einführung in die Thematik der rekonfigurierbaren Hardware. Hierzu wird auf die Architektur von FPGAs und deren Programmierung eingegangen. Als ein spezielles FPGA-Board wird das PROGRAPE-4-Board und dessen Architektur vorgestellt. In Kapitel 4 wird die Software PGR und die dazugehörige Beschreibungssprache PGDL zur Programmierung des PROGRAPE-4-Boards beschrieben.

Die Kapitel 5 und 6 beschäftigen sich mit der Implementierung des FPGA-Designs. Als Vorarbeit wird zunächst ein einfaches Lennard-Jones-Potential zur Kräfteberechnung implementiert. Ein einfaches Testprogramm untersucht die Genauigkeit und bestimmt den Speedup des  $O(N^2)$ -Problems. Schließlich wird das Hardwaredesign zum Linked-Cell-List-Algorithmus entwickelt und die Softwareimplementierung angepasst. Abschließend werden Zeitmessungen durchgeführt und die Ergebnisse diskutiert.

# **Kapitel 2**

# Grundlagen der Molekulardynamik

Die klassische Molekulardynamik beschäftigt sich mit der Berechnung von Wechselwirkungen zwischen verschiedenen Teilchen und mit der Integration der klassischen Bewegungsgleichungen. Diese Teilchen können unterschiedliche Formen und Eigenschaften haben. Es können beispielsweise Moleküle und Atome, aber auch Schüttgüter in Silos, wie z. B. Getreide oder Gestein, das aus einzelnen Kieseln zusammengesetzt ist, betrachtet werden. Dabei ist man an verschiedenen Faktoren interessiert, wie z. B. der Größe der Energie im simulierten System oder an den Kräften, die auf die einzelnen Teilchen wirken.

Die Methoden der Molekulardynamik sind vielseitig einsetzbar. Sie finden Anwendung in der physikalischen Chemie, Physik, Biophysik und Astrophysik. Mit Hilfe der Molekulardynamik lassen sich beispielsweise Eigenschaften von Flüssigkeiten, Rissbildung und Verformung von Festkörpern oder Reibung simulieren [24]. Aber auch bei der DNA-Analyse oder der Berechnung der Dynamik von Galaxien spielen die Methoden der Molekulardynamik eine Rolle [19].

Dieses Kapitel liefert eine kurze Einführung in die Methoden der Molekulardynamik. Es werden zunächst die wichtigsten physikalischen und mathematischen Grundlagen beschrieben und einige Teilchenmodelle vorgestellt. Anschließend folgt ein kurzer Einblick in Listen-Techniken zur effizienteren Berechnung von kurzreichweitigen Wechselwirkungen. Des Weiteren wird der Aufbau einer MD-Simulation erläutert. Neben den Vorteilen einer Simulation werden auch die Probleme diskutiert. Abschließend werden Methoden zur Beschleunigung einer MD-Simulation vorgestellt, wobei FPGAs als Hardwarebeschleuniger eine Möglichkeit sein werden.

### 2.1 Physikalische und mathematische Grundlagen

Die Grundlage für die Modellierung eines physikalischen Vielteilchensystems im Sinne der klassischen Molekulardynamik bilden die klassischen Bewegungsgleichungen (zumeist auch Newtonsche Bewegungsgleichungen genannt, weil sie sich zum überwiegenden Teil aus den drei Newtonschen Axiomen ableiten). Sie beschreiben die Bewegung der Teilchen unter der Einwirkung der Kräfte, die auf jedes Teilchen ausgeübt werden. Diese Kräfte entstehen beispielsweise durch Wechselwirkungen mit anderen Teilchen, durch die Wände des Systems oder durch äußere Felder, wie etwa das Gravitationsfeld oder elektromagnetische Felder. Durch die Bewegungsgleichungen sind,

bei Angabe von Anfangsbedingungen, die Bahnen der Teilchen genau bestimmt. In der Molekulardynamik ist es üblich, statt der klassischen Bewegungsgleichungen die äquivalente Hamiltonsche Formulierung der Bewegungsgleichungen zu verwenden:

$$\dot{\vec{r}}_i = \frac{d\mathcal{H}}{d\vec{p}_i} \quad , \quad \dot{\vec{p}}_i = -\frac{d\mathcal{H}}{d\vec{r}_i} \qquad i = 1, ..., N$$

(2.1)

$\vec{r}_i$ : Koordinaten des Teilchens i im Raum

$\vec{p}_i$ : Impuls des Teilchens i

N: Anzahl der Teilchen im System

$\mathcal{H}$ : Hamilton-Funktion

Die Hamiltonschen Bewegungsgleichungen stammen aus der *Hamiltonschen Mechanik*. Sie bilden ein System von Differentialgleichungen erster Ordnung. Die Hamilton-Funktion  $\mathcal{H}$ , auch Hamiltonian genannt, beschreibt dabei die gesamte mechanische Energie im System:

$$\mathcal{H} = \underbrace{\frac{1}{2} \sum_{i=1}^{N} \frac{\vec{p}_i^2}{m_i}}_{\text{kinetische Energie}} + \underbrace{\sum_{i=1}^{N-1} \sum_{j>i}^{N} U_{ij}(r_{ij})}_{\text{potentielle Energie}} + U_{ext}$$

(2.2)

N : Anzahl der Teilchen im System

$\vec{p}_i$ : Impuls des Teilchens i $m_i$ : Masse des Teilchens i

$U_{ij}$ : Wechselwirkungspotential zwischen zwei Teilchen i und j

$r_{ij}$ : Abstand zwischen Teilchen i und j ( $\|\vec{r}_i - \vec{r}_i\|_2$ )

$U_{ext}$ : Einfluss externer Potentiale

$U_{ext}$  bezeichnet hier den Einfluss externer Kräfte. Solche Kräfte existieren bei nichtabgeschlossenen Teilchensystemen, d. h. bei Systemen, denen während der Simulation von außen Energie zugeführt wird. Für abgeschlossene Systeme gilt:  $U_{ext} = 0$ .

Um nun ein physikalisches Teilchensystem simulieren zu können, muss das durch Gleichung 2.1 festgelegte Differentialgleichungssystem gelöst werden. Dies ist jedoch für ein System von drei und mehr Teilchen nicht mehr exakt lösbar. Deshalb muss die Lösung durch ein geeignetes numerisches Verfahren angenähert werden. Ein solches Verfahren wird auch als Integrator bezeichnet. Ein Integrator ist also ein numerisches, auf dem Rechner implementierbares Verfahren, das Systeme von Differentialgleichungen näherungsweise lösen kann [21]. Dabei sollte ein Integrator gewählt werden, der das System möglichst genau löst, denn die Qualität einer Simulation basiert im Wesentlichen auf der Effizienz und Genauigkeit der verwendeten Methode. In der Molekulardynamik berechnet der Integrator die Veränderung der Position und Geschwindigkeit eines Teilchens, die sich in einem Zeitschritt ergibt. Die Grundlage der Berechnung bilden die Position, Geschwindigkeit und Kraft dieses Teilchens zum aktuellen Zeitpunkt. Beispiele für Integratoren sind der Eulerund der Verlet-Algorithmus [11].

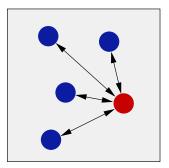

Abbildung 2.1: Wechselwirkungen in einem System mit offenen Rändern

### 2.2 System- und Teilchenmodelle

Durch den Einsatz der Molekulardynamik für die unterschiedlichsten Probleme ergeben sich verschiedene Modelle. Es ist leicht einzusehen, dass die Sterne einer Galaxie nicht mit dem gleichen Modell simuliert werden können, wie die Atome in einem Salzkristall. Bei der Simulation einer Galaxie sind die Wechselwirkungen mit Sternen einer anderen Galaxie meist so klein, dass man sie vernachlässigen kann. Es genügt also, nur die Sterne der eigenen Galaxie zu betrachten und weitere Einflüsse höchstens durch einen Korrekturterm zu berücksichtigen. Die Atome in einem Salzkristall dagegen sind gitterförmig angeordnet. Hierbei ist es ausreichend, lediglich einen Ausschnitt des Kristalls zu betrachten und diesen periodisch in alle Richtungen fortzusetzen [19].

### 2.2.1 Periodische und nicht-periodische Systeme

Aus dem oben beschriebenen Beispiel ergibt sich direkt eine erste grobe Einteilung der Modelle in periodische und nicht-periodische Systeme. Im Fall der Simulation von Sternen einer Galaxie ist es sinnvoll diese durch ein offenes, nicht-periodisches System zu simulieren. Der Salzkristall dagegen lässt sich durch ein periodisch fortgesetztes System darstellen.

Abbildung 2.1 zeigt schematisch die Wechselwirkungen in einem offenen System. Das simulierte System wird hier durch eine quadratische Box markiert und im folgenden Simulationsbox genannt. Bei einem offenen System werden zur Berechnung der Kraft, die auf ein Teilchen einwirkt, die Einflüsse aller anderen im System vorhandenen Teilchen mit einbezogen.

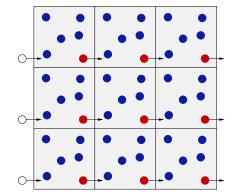

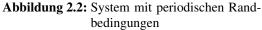

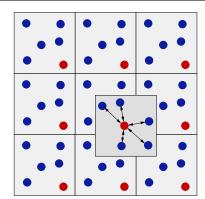

Bei Systemen mit periodischen Randbedingungen betrachtet man ebenfalls eine Simulationsbox, in der die Simulation stattfindet. Um Randeffekte zu vermeiden (Teilchen am Rand eines Körpers oder Stoffes verhalten sich anders als Teilchen innerhalb) und unendlich große Systeme simulieren zu können, werden Bildboxen um die eigentliche Simulationsbox gelegt. Im zweidimensionalen Fall wären es acht Bildboxen, im dreidimensionalen Fall entsprechend 26. Diese Bildboxen sind exakte Kopien der Originalbox. Dadurch bleibt die Anzahl der Teilchen im simulierten System konstant, denn tritt ein Teilchen während der Simulation aus der Originalbox aus, erscheint auf der anderen Seite der Box sofort dessen Bildteilchen (siehe Abbildung 2.2). Zur Berechnung der Kraft, die auf ein Teilchen einwirkt, werden nur die Einflüsse der nächsten Nachbarn berücksichtigt. Nächste Nachbarn eines Teilchens können in einem periodischen System aber auch Teilchen aus den Bildboxen sein. Deshalb wird eine gedachte Box mit der Kantenlänge der Simulationsbox um das Teilchen gelegt (siehe Abbildung 2.3). Nun lässt man alle Teilchen innerhalb dieser gedachten Box mit diesem Teilchen wechselwirken. Dieses Prinzip wird auch *Minimum Image Convention* genannt [24].

**Abbildung 2.3:** Wechselwirkungen in einem System mit periodischen Randbedingungen nach der *Minimum Image Convention*

Es können jedoch auch Mischformen von periodischen und offenen Systemen auftreten. Dies ist beispielsweise bei der Simulation eines Stoffes in einer Röhre sinnvoll. Dabei wird das Teilchensystem in eine Koordinatenrichtung periodisch fortgesetzt und in den anderen beiden Richtungen begrenzt.

### 2.2.2 Wechselwirkungspotentiale

Wie schon erwähnt werden zur Beschreibung der Interaktionen zwischen den Teilchen eines Systems so genannte Wechselwirkungspotentiale verwendet. Interagierende Teilchen können dabei verschiedene Objekte sein, wie Atome und Moleküle, aber auch Sterne oder Galaxien. In der klassischen Simulation werden sie als punktförmige Massen beschrieben. Sie können paarweise oder zu mehreren miteinander wechselwirken, oder aber aus Anteilen von mehreren Atomen bestehen (z. B. bei Winkel- oder Torsionspotentialen). In dieser Arbeit werden jedoch nur paarweise Wechselwirkungspotentiale betrachtet.

Neben der Anzahl der wechselwirkenden Teilchen unterscheidet man auch zwischen der Reichweite von Potentialen. Dabei unterteilt man diese in kurzreichweitige und langreichweitige Wechselwirkungspotentiale. Fällt das Potential mit steigendem Teilchenabstand r schneller als  $r^{-d}$  gegen Null ab, wobei d die Dimension des Systems ist, so ist das Potential kurzreichweitig, anderenfalls langreichweitig. Betrachtet man das folgende Integral, wird klar, dass diese Regel sinnvoll ist:

$$I = \int \frac{1}{r^n} dr^d = \begin{cases} \infty : n \le d & \text{(langreichweitig)} \\ endlich : n > d & \text{(kurzreichweitig)} \end{cases}$$

(2.3)

r: Abstand zwischen zwei Teilchen

d: Dimension des Systems

Gilt also  $n \le d$ , so berechnet sich die potentielle Energie eines Teilchens unter Berücksichtigung aller anderen Teilchen des Universums. Gilt dagegen n > d, sind die Einflüsse der anderen Teilchen im wesentlichen auf eine Region begrenzt. Für weiter außen liegende Teilchen kann dann ein Korrekturterm berücksichtigt werden [25].

Abbildung 2.4: Lennard-Jones-Potential

### Kurzreichweitige Wechselwirkungen

Kurzreichweitige Wechselwirkungen treten z. B. bei atomaren Abstoßungen auf. Sie ermöglichen es, bei der Berechnung der auf ein Teilchen einwirkenden Kraft lediglich benachbarte Teilchen bis zu einer bestimmten Entfernung zu berücksichtigen. Der Grund dafür ist, dass kurzreichweitige Potentiale mit wachsendem Teilchenabstand sehr schnell gegen Null konvergieren und deshalb weit entfernte Teilchen kaum mehr ins Gewicht fallen. Das Abschneiden des Potentials wird durch die Einführung eines so genannten Cutoff-Radius realisiert. Teilchen, die sich jenseits dieses Radius befinden, werden nicht mehr berücksichtigt, d. h. für alle Abstände  $r > r_{cut}$  gilt: U(r) = 0. Durch das Abschneiden des Potentials entsteht jedoch eine Diskontinuität an der Kante, d. h. die Kraft wird an dieser Stelle unendlich groß. Für die MD-Simulation stellt dies ein Problem dar, da die Energieerhaltung nicht mehr erfüllt ist. Aus diesem Grund verwendet man in der Molekulardynamik das so genannte Shifted-force Potential (Gleichung 2.4), wodurch sowohl das Potential als auch die Kraft stetig über den Cutoff-Radius auf Null abfällt [24].

$$U(r) = \begin{cases} U(r) - U(r_{cut}) - \frac{dU}{dr}(r - r_{cut}), & r \le r_{cut} \\ 0, & r > r_{cut} \end{cases}$$

(2.4)

Ein Beispiel für ein kurzreichweitiges Wechselwirkungspotential ist das Lennard-Jones-Potential:

$$U_{LJ}(r) = 4\varepsilon \left( \left( \frac{\sigma}{r} \right)^{12} - \left( \frac{\sigma}{r} \right)^{6} \right) \tag{2.5}$$

r: Abstand zwischen zwei Teilchen

$\varepsilon$ : Energiekonstante

$\sigma$ : Durchmesser eines Teilchens

Abbildung 2.5: Coulomb-Potential für Teilchen mit gleicher Ladung

### Langreichweitige Wechselwirkungen

Langreichweitige Wechselwirkungen treten beispielsweise bei elektrostatischen Interaktionen zwischen Punktladungen oder Dipolen und bei Gravitation auf. Bei der Berechnung solcher Wechselwirkungen ist es nicht mehr möglich, weit entfernte Teilchen zu vernachlässigen. Für die genaue Bestimmung der Kräfte müssen die Einwirkungen aller Teilchen im simulierten System berücksichtigt werden. Im Simulationsprogramm wird dies durch eine Doppelschleife über alle N Teilchen realisiert. Die Komplexität des Problems ist deshalb  $O(N^2)$ , was besonders bei großen Teilchenzahlen die Rechenzeit dramatisch verlängert. Durch geeignete Algorithmen, wie z. B. Baum-Algorithmen lässt sich die Komplexität jedoch auf  $O(N \log N)$  oder sogar O(N) verbessern.

Ein Beispiel für ein langreichweitiges Wechselwirkungspotential ist das Coulomb-Potential:

$$U_{Coulomb}(r) = \frac{q_1 q_2}{4 \pi \varepsilon_0 r} \tag{2.6}$$

r : Abstand zwischen zwei Teilchen

$q_1, q_2$ : Ladungen der zwei betrachteten Teilchen  $\varepsilon_0$ : Dielektrizitätskonstante des Vakuums

Durch die Festlegung des Potentials und dessen Parameter lässt sich die komplette Energie des simulierten Systems berechnen. Durch Ableiten der Potentialfunktion, also  $\vec{F} = -\nabla U$ , erhält man außerdem die Kraft, die auf jedes Teilchen im System einwirkt.

### 2.3 Nachbarschaftslisten

Von besonderem Interesse für diese Arbeit sind die kurzreichweitigen Wechselwirkungen. Wie schon erwähnt werden hierbei nur lokale Informationen benötigt. Lokale Teilchen sind dabei diejenigen, die sich innerhalb des Cutoff-Radius des betrachteten Teilchens befinden. Das Simulationsprogramm weiß nun aber nicht, welche Teilchen *j* lokal zu einem Teilchen *i* sind. Es muss für jedes

Abbildung 2.6: Prinzip der Verlet-Listen

Teilchen j überprüft werden, ob dessen Abstand zu Teilchen i kleiner oder gleich dem Cutoff-Radius ist. Dies wird durch eine Doppelschleife realisiert, womit die Komplexität der Kräfteberechnung immer noch bei  $O(N^2)$  liegt.

Die Lösung für dieses Problem sind Nachbarschaftslisten. In diesen Listen werden für jedes Teilchen die Nachbarteilchen abgespeichert, die sich innerhalb des Cutoff-Radius befinden. Man unterscheidet dabei zwischen zwei Varianten: Verlet-Listen und Linked-Cell-Listen.

#### Verlet-Listen

Bei der Verlet-Listen-Technik werden Listen angelegt, in denen für alle N Teilchen des Systems die Teilchen gespeichert werden, deren Abstand kleiner oder gleich dem Cutoff-Radius  $r_{cut}$  ist. Außerdem wird für jedes Teilchen ein "Reservoir" angelegt. Dieses Reservoir ist eine Kugelschale mit der Dicke  $r_{skin}$  und dem Innenradius  $r_{cut}$  (siehe Abbildung 2.6). Es enthält alle Teilchen, deren Abstand zum aktuellen Teilchen zwischen  $r_{cut}$  und  $r_{cut} + r_{skin}$  liegt. Es sorgt dafür, dass keine Teilchen "unbemerkt" Nachbarn werden können. Die im Reservoir befindlichen Teilchen können im aktuellen Simulationsschritt nicht mit dem entsprechenden Teilchen wechselwirken und werden bei der Berechnung nicht berücksichtigt. Sie können sich jedoch im nächsten Simulationsschritt innerhalb des Cutoff-Radius befinden. Die Verlet-Liste wird immer dann vollständig aktualisiert, wenn ein Teilchen eine größere Distanz als  $r_{skin}$  zurücklegt. Die Größe von  $r_{skin}$  bestimmt dabei, wie oft die Liste aktualisiert wird. Für kleines  $r_{skin}$  wird die Liste häufig aktualisiert. Es sind jedoch nur wenige Abfragen in der Kraftroutine nötig, da sich wenige Teilchen im Reservoir befinden. Bei größerem  $r_{skin}$ steigt die Anzahl der Abfragen, die Liste muss jedoch seltener aktualisiert werden. Es gilt also ein  $r_{skin}$  zu finden, das die Listen-Updates und Abfragen optimiert [27]. Die Aktualisierung der kompletten Liste ist aufwändig, denn um die Wechselwirkungspartner zu identifizieren und in die Listen für alle Teilchen einzusortieren, müssen jedes Mal N(N-1)/2 Abfragen gemacht werden [17]. Zudem steigt der Speicheraufwand für die Verlet-Liste beinahe wie  $O(N^2)$ . Die Verlet-Listen-Technik ist deshalb für große Teilchenzahlen ungeeignet.

Abbildung 2.7: Prinzip der Linked-Cell-Listen

#### Linked-Cell-Listen

Bei der Linked-Cell-Listen-Technik wird die Simulationsbox in kubische Zellen eingeteilt. Die Teilchen werden anhand ihrer Positionen den einzelnen Zellen zugeordnet und in einer Liste je Zelle abgespeichert. In der einfachsten Art der Implementierung wird die Kantenlänge  $L_c$  der Zellen so gewählt, dass sie mindestens  $r_{cut}$  beträgt. Damit befinden sich alle Teilchen mit einem Abstand kleiner oder gleich dem Cutoff-Radius in der eigenen oder in einer der Nachbarzellen. Bei der Kraftberechnung werden dann nur die Teilchen berücksichtigt, die sich in der eigenen Zelle oder in einer der Nachbarzellen befinden. Der Vorteil dieser Methode ist, dass die Listen nicht aufwändig angelegt werden und nur lokale Operationen notwendig sind. Im Gegensatz zur Verlet-Listen-Technik brauchen hier nämlich nicht alle Teilchen des Systems betrachtet werden, sondern jeweils nur die Teilchen aus den entsprechenden Zellen. Sie kann auch für große Teilchenzahlen verwendet werden, da sie mit O(N) skaliert [27].

#### **Kombination von Verlet und Linked-Cell**

Um die Effizienz der Verlet-Listen und die Lokalität der Linked-Cell-Listen auszunutzen, verwendet man häufig auch eine Kombination beider Methoden [26]. Die Berechnung der Wechselwirkungen geschieht dabei mit Hilfe der Verlet-Listen. Um das Problem der quadratischen Komplexität der Aktualisierung der Listen zu lösen, werden diese mittels Linked-Cell-Listen erneuert. Die Komplexität einer solchen Mischform ist wieder O(N).

### 2.4 MD-Simulation

Die Computersimulation von Vielteilchensystemen hat in den letzten Jahren erheblich an Bedeutung gewonnen. Die theoretische Beschreibung komplexer Systeme und die experimentellen Techniken für detaillierte mikroskopische Informationen sind sehr weit entwickelt. Dennoch lassen sich bestimmte Aspekte solcher Systeme nur mittels Simulation in den gewünschten Einzelheiten betrachten [25].

2.4. MD-SIMULATION 11

Die traditionellen Simulationsmethoden für komplexe Vielteilchensysteme lassen sich grob in zwei Gebiete unterteilen: Molekulardynamik und "Monte Carlo". Die Molekulardynamik basiert auf der Lösung der klassischen Bewegungsgleichungen aus der Mechanik, weshalb sie auch häufig klassische Molekulardynamik genannt wird. Bei dieser Methode werden ausschließlich Teilchensysteme betrachtet, deren Teilchen über ein gegebenes Potential miteinander wechselwirken. Dabei gewinnt man Informationen über die zeitliche Entwicklung des Systems. Die "Monte Carlo"-Methode dagegen beschäftigt sich mit der Bestimmung von Eigenschaften komplexer Systeme mit Hilfe von Zufallszahlen. Sie wird deshalb auch als Methode der statistischen Versuche bezeichnet. Die Zufallszahl-Experimente werden dabei als eine mögliche Realisierung des Systems interpretiert. Dazu müssen Kriterien definiert werden, mit denen unrealistische oder unsinnige Ergebnisse ausgeschlossen werden. Die Experimente werden hinreichend oft wiederholt und anschließend die Ergebnisse mit statistischen Methoden ausgewertet. Die "Monte Carlo"-Methode liefert keine expliziten Zeitinformationen, da sie stochastische Veränderungen der Teilchenpositionen im Konfigurationsraum erzeugt. Teilweise werden stochastisch erzeugte Trajektorien zeitlich interpretiert, wobei allerdings keine Zeitskala existiert.

Die Grundlage beider Simulationsmethoden ist immer das physikalische Modell, welches die Wechselwirkung zwischen den einzelnen Systemkomponenten beschreibt. Ein Teilchensystem, das simuliert werden soll, benötigt also eine möglichst vollständige physikalische Beschreibung. Die Computersimulation ist demnach nur insoweit korrekt, wie das physikalische Modell stimmt [21].

Dieser Arbeit liegen ausschließlich die Methoden der Molekulardynamik zugrunde. Deshalb sei die "Monte Carlo"-Methode an dieser Stelle nur der Vollständigkeit halber erwähnt. Alle weiteren Betrachtungen beziehen sich auf die Molekulardynamik.

### 2.4.1 Vorteile der Computersimulation

Die Computersimulation ermöglicht nicht nur eine detailliertere Betrachtung der Ergebnisse eines Experimentes. Sie bietet Möglichkeiten, die weit über die rein experimentelle Betrachtung hinaus gehen. So können mittels Computersimulation Experimente vollzogen werden, die in der Realität gar nicht oder nur sehr schwierig durchführbar sind. Dies ist beispielsweise der Fall, wenn das zu untersuchende Material mit dem Behälter reagiert oder während des Experimentes extrem hohe Temperaturen auftreten. Des Weiteren könnte es zu aufwändig oder zu teuer sein, die passende Umgebung für die Durchführung eines bestimmten Experimentes herzustellen [21]. Neben dem Kostenfaktor spielt aber auch die Sicherheit eine Rolle. So ist es sinnvoll, Experimente, deren Ausgang ungewiss ist, zunächst zu simulieren. Dadurch können mögliche Gefahrenquellen ausgemacht und Risiken abgeschätzt werden.

### 2.4.2 Durchführung einer MD-Simulation

Der Ablauf einer MD-Simulation ist dem eines realen Experimentes sehr ähnlich. Bei einem Experiment wird zunächst eine Probe des zu untersuchenden Stoffes vorbereitet. An diese Probe werden Messinstrumente, z. B. Thermometer, *Manometer* oder *Viskosimeter* angeschlossen und die entsprechende Größe über einen bestimmten Zeitraum hinweg gemessen. Da Messinstrumente üblicherweise nicht exakt messen, ergeben sich Messfehler. Damit diese Messfehler das Ergebnis des Experimentes nicht verfälschen, werden mehrere Messungen durchgeführt und anschließend die Mittelwerte der Resultate gebildet [10].

Nach dieser Vorgehensweise richtet sich auch ein typisches MD-Programm. Der Aufbau eines MD-Programms und damit der Ablauf einer MD-Simulation wird im Folgenden beschrieben:

- 1. Parameter einlesen: Zunächst werden die Parameter festgelegt und eingelesen, die das zu simulierende System spezifizieren. Dies sind Größen wie die Anzahl der Teilchen im System und deren Massen, Dichten, Dimensionen und Anfangstemperaturen oder auch die Anzahl und Größe der durchzuführenden Zeitschritte. Für eine MD-Simulation benötigt man darüberhinaus noch ein Wechselwirkungspotential, das beschreibt, wie die einzelnen Teilchen miteinander wechselwirken (siehe Kapitel 2.2.2), und einen Integrator, um die Bewegung der Teilchen im *Phasenraum* zu simulieren (siehe Kapitel 2.1).

- 2. Initialisierung: Um eine Simulation zu starten, benötigen die einzelnen Teilchen Anfangspositionen und -geschwindigkeiten. Die Positionen sollten entsprechend den Eigenschaften des simulierten Systems gewählt werden. Dabei ist darauf zu achten, dass die Teilchen sich nicht überschneiden. Bei der Initialisierung der Positionen gibt es verschiedene Möglichkeiten. Zum einen können Eingabedaten verwendet werden, die aus Experimenten stammen. Diese sind jedoch nicht immer vorhanden und es kann nicht ohne weiteres zu beliebigen anderen Teilchenzahlen übergegangen werden. Eine andere Möglichkeit ist, die Teilchen über einen Zufallszahlengenerator zu positionieren. Hierbei ist jedoch nicht sichergestellt, dass keine Teilchen überlappen. Die Teilchen werden deshalb häufig auf einem regelmäßigen Gitter angeordnet, z. B. einem Rechteckgitter oder einem fcc-Gitter (face-centered-cube-Gitter). Ein ähnliches Problem ergibt sich bei den Anfangsgeschwindigkeiten. Die Lösung hier sind Gauss-verteilte Zufallszahlen.

Dieser konstruierte Anfangszustand ist zumeist nicht typisch für das simulierte System. Deshalb ist es notwendig das System zu equilibrieren. Dabei wird die Eigenschaft ausgenutzt, dass sich ein gestörtes System nach einiger Zeit wieder im thermodynamischen Gleichgewicht befindet. Im Simulationsprogramm wird die Equilibrierung realisiert, indem die zentrale Schleife zunächst einige Male durchlaufen wird, ohne dabei die physikalischen Eigenschaften des Systems zu messen. In der Regel werden einige tausend Zeitschritte ausgeführt, so dass nur noch statistische Fluktuationen um thermodynamische Mittelwerte erfolgen.

3. **Kräfteberechnung:** Die Kräfteberechnung geschieht mit Hilfe des Wechselwirkungspotentials. Sie ist der zeitintensivste Teil einer MD-Simulation, da sie in der Regel ca. 95% der gesamten Laufzeit benötigt. Im einfachsten Fall muss zur Berechnung der Einzelkräfte, die auf ein Teilchen i wirken, dieses einmal mit allen anderen Teilchen j des Systems wechselwirken. Im Programm wird dies durch eine Doppelschleife realisiert. Das bedeutet, dass die Berechnung der Kräfte für ein System mit N Teilchen mit  $O(N^2)$  skaliert. Für eine sehr große Teilchenanzahl N bedeutet dies einen unrealisierbar großen Rechenaufwand. Deshalb ist die Kräfteberechnung der Ansatzpunkt für viele Algorithmen, die Laufzeit einer MD-Simulation zu verkürzen. Mittlerweile gibt es Algorithmen mit denen die Kräfteberechnung mit O(N) statt mit  $O(N^2)$  skaliert. Auf dieses Problem wird in Kapitel 2.4.4 noch genauer eingegangen.

Nach der Berechnung der Einzelkräfte wird außerdem noch die Gesamtkraft und die potentielle Energie im System ermittelt.

4. **Integration der klassischen Bewegungsgleichungen:** Nachdem die Einzelkräfte berechnet wurden, können nun die klassischen Bewegungsgleichungen integriert werden. Dieses Problem ist für Drei- und Mehrteilchensysteme nicht mehr exakt lösbar und wird deshalb durch ein numerisches Verfahren angenähert, wobei die klassischen Bewegungsgleichungen numerisch integriert werden. Ausgehend von der gegebenen Position, Geschwindigkeit und Kraft

eines Teilchens zu einem bestimmten Zeitpunkt berechnet der Integrator die Veränderung der Position und Geschwindigkeit dieses Teilchens, die sich in einem Zeitschritt ergibt. Diese Berechnung wird für alle Teilchen des Systems durchgeführt. Anschließend werden mit den veränderten Positionen und Geschwindigkeiten erneut die Kräfte berechnet. Die Kräfteberechnung und die Integration der Bewegungsgleichungen bilden den Kern einer MD-Simulation. Die beiden Schritte werden solange wiederholt, bis die gewünschte Simulationslänge erreicht ist.

5. **Auswertung:** Neben der potentiellen Energie und den Positionen und Geschwindigkeiten der Teilchen, müssen auch die Größen, über die eine Simulation Aufschluss geben soll, berechnet werden. Solche Größen sind beispielsweise die Temperatur, der Druck oder verschiedene Arten von Korrelationsfunktionen. Es ist sinnvoll, solche Berechnungen oder auch Mittelungen von wichtigen Systemgrößen während der laufenden Simulation durchzuführen und auszugeben. Anderenfalls müsste die gesamte Entwicklung des 6*N*-dimensionalen Phasenraums abgespeichert werden.

Wie bei einem realen Experiment können auch bei einer Simulation Fehler auftreten, die zu falschen Ergebnissen führen. Ein typischer Fehler ist, dass das System nicht korrekt vorbereitet wurde, bzw. die Parameter im Simulationsprogramm nicht korrekt sind. Des Weiteren kann der Mess- bzw. Simulationszeitraum zu kurz gewählt sein oder es wird in Wirklichkeit nicht das gemessen, was man glaubt zu messen. Bei der MD-Simulation wie bei Experimenten ist also immer Achtsamkeit und Sorgfalt geboten [10].

### 2.4.3 Grenzen der Computersimulation

Trotz der Vorteile die eine Computersimulation bietet, bedeutet das nicht, dass reale Experimente nicht mehr nötig sind. Bei der Beschreibung von Wechselwirkungen muss man davon ausgehen, dass jedes Objekt im Universum mit jedem anderen Objekt wechselwirkt [19]. Eine Simulation des gesamten Universums ist jedoch nicht realisierbar, da der Rechenaufwand unendlich groß werden würde. Außerdem sind meist nicht alle Faktoren, die in ein Experiment einfließen, bekannt. Eine Computersimulation kann also lediglich Ausschnitte der Realität approximieren. Daher ist es immer notwendig, die aus der Simulation gewonnenen Ergebnisse mit den theoretischen und experimentellen Ergebnissen zu vergleichen. Weichen die simulierten Ergebnisse zu stark von der Realität ab, muss das Modell entsprechend korrigiert werden. Simulation, Theorie und Realität gehen also immer Hand in Hand [21].

Durch die beschränkte Rechenleistung werden der Computersimulation weitere Grenzen gesetzt. Insbesondere wird die Anzahl der zu simulierenden Teilchen durch die Geschwindigkeit der Rechenoperationen limitiert. Im Vergleich zu den ersten molekulardynamischen Simulationen vor ca. 50 Jahren können heute aufgrund der enorm schnell gewachsenen Rechenleistung wesentlich mehr Teilchen simuliert werden. Dennoch ist man versucht, die maximal mögliche Teilchenzahl weiter zu erhöhen.

Alder und Wainwright waren die Ersten, die im Jahre 1957 die Methode der Computersimulation für ihre Studien benutzten. Sie simulierten ein System von harten Kugeln auf einer *IBM 704*. Bei einem System von harten Kugeln wird die Größe eines Zeitschritts durch die Zeit bis zur nächsten auftretenden Kollision zweier Kugeln bestimmt. Mit der IBM 704 konnten bei einer Gesamtzahl von

500 Teilchen 500 Kollisionen pro Stunde gerechnet werden. Für einen sinnvollen Simulationslauf von 200.000 Kollisionen benötigte der Rechner also mehr als zwei Wochen [25].

A. Rahman war 1964 der Erste, der ein System simulierte, bei dem die Teilchen durch ein kontinuierliches Potential miteinander wechselwirkten. Die Simulation wurde auf einer *CDC 3600* durchgeführt. Für die Wechselwirkungsberechnung der insgesamt 864 Teilchen benötigte die Maschine 45 Sekunden pro Zeitschritt (die Zeitschritte eines solchen Systems sind konstant). Eine Berechnung von 50.000 Zeitschritten dauerte also mehr als drei Wochen. Ein Standard-PC benötigt heutzutage für diese Rechnung höchstens eine Stunde [25].

Durch die Entwicklung schnellerer, größerer und auch paralleler Rechnerarchitekturen konnten die zu simulierende Zeitspanne und Systemgröße erheblich vergrößert werden. Im Jahre 1999 simulierte J. Roth auf der *Cray T3E-1200* in Jülich ein System mit  $5 \cdot 10^9$  Teilchen. Dies wurde durch IMD ermöglicht, ein MD-Programm, das die 512 Knoten der Cray mit jeweils 256 MB Speicher sehr effizient ausnutzte. Allerdings würde eine Simulation von 10.000 Zeitschritten unter Ausnutzung der gesamten Ressourcen der Maschine etwa ein Vierteljahr dauern [25].

### 2.4.4 Methoden zur Beschleunigung einer MD-Simulation

Das Ziel ist es, die Laufzeit einer Simulation weiter zu verkürzen, um größere Systeme simulieren zu können. Dies erreicht man zum einen durch optimierte Algorithmen und zum anderen durch schnellere Rechnerarchitekturen. Mit der Optimierung setzt man dabei hauptsächlich bei der Berechnung der Wechselwirkungen an.

Durch die Optimierung der Algorithmen wurde in den letzten Jahren eine höhere Beschleunigung der Laufzeit erreicht, als durch den Einsatz schnellerer Rechner. Die Berechnung von kurzreichweitigen Wechselwirkungen lässt sich mit Hilfe von Listen-Techniken (siehe Kapitel 2.3) auf ein Problem der Komplexität O(N) zurückführen. Auch langreichweitige Wechselwirkungen lassen sich entsprechend optimieren. Mittels gitterbasierter Ewald-Summationen und Baum-Algorithmen lässt sich die Komplexität auf  $O(N \log N)$  reduzieren. Multipol-, Mehrgitter- und Waveletverfahren erreichen sogar eine Komplexität von O(N). Besonderes Augenmerk wird außerdem auf die Parallelisierung der MD-Algorithmen gelegt.

Auf der anderen Seite werden verstärkt spezialisierte Computerarchitekturen eingesetzt um größere Systeme simulieren zu können. Für die Berechnung der Wechselwirkungen wird meist nur ein begrenzter Umfang an Operationen benötigt. Deshalb verwendet man für die Kräfteberechnung Computerarchitekturen, die diese Operationen extrem schnell durchführen können. Beispiele hierfür sind APE- und GRAPE-Rechner (siehe Kapitel 3.4.1), die im Bereich der Quantenchromodynamik und der Astrophysik eingesetzt werden. Diese Rechner besitzen jedoch eine fest codierte Logik und können somit nur für eine spezielle Problemklasse eingesetzt werden. Eine flexiblere Alternative bietet der Einsatz rekonfigurierbarer Logik, wie den FPGAs. Sie können umkonfiguriert und somit für verschiedene Algorithmen verwendet werden. Mit diesem Ansatz zur Beschleunigung molekulardynamischer Berechnungen beschäftigen sich die folgenden Kapitel dieser Arbeit.

# Kapitel 3

## **FPGA**

Die Entwicklung rekonfigurierbarer Hardware, der so genannten PLDs (*Programmable Logic Device*), ist ein wichtiger Meilenstein in der Halbleiterindustrie. Wurde zuvor die anwendungsspezifische Funktion einer Schaltung entweder durch die Auswahl geeigneter Standardbauteile und deren Verdrahtung auf einer Platine oder durch die Herstellung einer speziellen integrierten Schaltung erreicht, so kann nun der Anwender die Verschaltung selbst programmieren und jederzeit ändern.

Als eine spezielle Bauart für PLDs wurden Mitte der 80er Jahre die ersten FPGAs auf den Markt gebracht. Mit weniger als 1.000 Gatteräquivalenten waren die Möglichkeiten der FPGAs damals jedoch noch sehr beschränkt. Aufgrund ihrer geringen Logikdichte und Geschwindigkeit und ihrer hohen Anschaffungskosten boten sie zunächst keine echte Alternative zu fest codierter Logik, wie z. B. den ASICs. Mittlerweile jedoch sind FPGAs mit einer Million Gatteräquivalenten verfügbar. Zudem wächst die Verarbeitungsgeschwindigkeit ständig an, wogegen die Preise sinken. FPGAs bieten heute nicht nur Alternativen zu herkömmlichen Lösungen, sondern ermöglichen auch völlig neue Anwendungen. Damit stellt die programmierbare Logik einen wesentlichen Beitrag zur Technologie der Zukunft dar [29].

In diesem Kapitel werden zunächst einige Beispiele für die verschiedensten Anwendungsgebiete für FPGAs gegeben. Anschließend wird am Beispiel der Xilinx-FPGAs die grundlegende Architektur eines FPGAs beschrieben. Dies führt zur Programmierung von FPGAs. Dazu werden zunächst die Unterschiede zwischen Hardware- und Softwareprogrammierung verdeutlicht. Abschließend wird auf den Einsatz von FPGAs als Koprozessoren und die Programmierung solcher Koprozessoren eingegangen. In diesem Zusammenhang wird die Architektur des PROGRAPE-4-Boards erläutert, welches als Hardwarebeschleuniger in dieser Arbeit eingesetzt wurde.

### 3.1 Anwendungsgebiete

Durch ihre Rekonfigurierbarkeit bieten FPGAs weitreichende Einsatzmöglichkeiten für verschiedenste Bereiche und Anwendungen. Dazu trägt unter anderem die immer einfacher werdende Programmierung bei. Diese Vereinfachung wird nicht nur durch hochentwickelte Programmiersprachen erreicht, sondern auch durch vorgefertigte Designs, die in Form von IP-Cores zum Quelltext hinzugebunden werden können. Besonders in Bereichen, in denen Algorithmen oder Protokolle schnell

16 KAPITEL 3. FPGA

weiterentwickelt werden, ist die Verwendung rekonfigurierbarer FPGAs vorteilhaft. Produkte können so schneller auf den Markt gebracht und an neue Entwicklungen angepasst werden. Außerdem können durch die Rekonfigurierbarkeit Entwicklungsfehler nachträglich behoben werden.

Im Folgenden werden einige Beispiele für den Einsatz von FPGAs genannt [30].

- Luft- und Raumfahrt/militärische Anwendungen: In diesem Bereich werden hauptsächlich FPGAs mit strahlungsfestem Gehäuse eingesetzt. Sie werden vor allem für die Steuerung und Kopplung mehrerer Bildsignalquellen und für die Signalverarbeitung unter Echtzeitbedingungen verwendet.

- Automobilindustrie: In der Automobilindustrie werden FPGAs für die schnelle und einfache Implementierung von Designs für die Automobilelektronik verwendet. Hierbei sorgen FPGAs für den effizienten Transport von Datenströmen, der für eine Vernetzung mehrerer Peripheriefunktionen im Auto, wie Navigation, Entertainment oder Fahrerinformationssystemen, nötig ist.

- Rundfunk und Medienbranche: Das Senden und Empfangen von Kurz-, Mittel- und Langwellen-Signalen spielt in der Rundfunk- und Medienbranche eine große Rolle. Für die Signalverarbeitung und die Decodierung von Musik, Sprache und Datendiensten werden FPGAs eingesetzt.

- Verbraucher: Auch für Verbraucheranwendungen bieten FPGAs kostengünstige Lösungen.

Sie werden beispielsweise für digitale Flachbildschirme, die Vernetzung daheim oder Digitalempfänger verwendet.

- Industrie/Wirtschaft/Medizin: In den Bereichen Industrie, Wirtschaft und Medizin werden FPGAs vor allem für die Automatisierung, zur Motorkontrolle und für die Bildverarbeitung verwendet.

- **Speicher und Server:** FPGAs eignen sich für die Realisierung sehr schneller Speicher- und Schnittstellensysteme. Sie werden unter anderem in *NAS* und *SAN*-Systemen verwendet.

- **Kommunikation:** FPGAs sind sowohl in der drahtlosen, als auch in der drahtgebundenen Kommunikation einsetzbar. Sie werden beispielsweise bei der Protokoll-Abarbeitung für verschiedene Übertragungsstandards, wie *GPRS* oder Ethernet-MAC-Layer verwendet.

- Anwendung als Prototypen: Bei der Herstellung von Schaltungen kann eine Simulation in vielen Fällen nicht mehr effizient durchgeführt werden. Zur Verifikation werden deshalb FPGA-basierte Prototypen eingesetzt und erst danach wird die Schaltung auf den Chip gebracht.

- Beschleunigung von Algorithmen: Mit dieser Art der Anwendung von FPGAs beschäftigt sich diese Diplomarbeit. Die rekonfigurierbare Hardware fungiert dabei als Koprozessor. Rechenintensive Teile eines Algorithmus werden nicht mehr auf der CPU, sondern auf einem oder mehreren FPGAs ausgeführt. In Kapitel 3.4 wird auf die Funktion von FPGAs als Koprozessoren genauer eingegangen.

**Abbildung 3.1:** Foto eines FPGAs

**Abbildung 3.2:** Architektur eines FPGAs

### 3.2 Allgemeine Architektur von FPGAs

Ein FPGA ist ein Siliziumchip, wie er in Abbildung 3.1 dargestellt ist. Die Abkürzung FPGA steht für *Field Programmable Gate Array*. Der Name weist auf die allen FPGAs gemeinsame Struktur und Eigenschaft hin, denn ein FPGA besteht im Wesentlichen aus einer Matrix programmierbarer Logikelemente [20].

Grundsätzlich besteht ein FPGA aus drei Komponenten: Logikzellen , I/O-Zellen und einem elektrischen Verbindungsnetzwerk. FPGAs gibt es in unterschiedlichen Bauformen und von verschiedenen Herstellern. Neben den führenden Herstellern Xilinx und Altera haben sich auch Firmen wie Actel, Lucent, Lattice und Atmel in der Herstellung von FPGAs etabliert [3, 22]. Abbildung 3.2 stellt den Aufbau eines FPGAs schematisch dar.

Die Logikzellen, oder auch Logikblöcke (CLBs) genannt, sind die wichtigsten rekonfigurierbaren Elemente eines FPGAs. Sie sind in einer quadratischen Matrix angeordnet. Ihnen kann im Rahmen der verfügbaren Ressourcen ein beliebiges digitalelektronisches Verhalten zugewiesen werden. Die I/O-Zellen oder I/O-Blöcke (IOBs) bilden die Schnittstellen zwischen der FPGA-internen Schaltungslogik und der Außenwelt. Sie können für verschiedene elektrische Verbindungsstandards konfiguriert werden, so dass FPGAs in einer Vielzahl von digitalelektronischen Umgebungen eingesetzt werden können. Sämtliche Logik- und I/O-Zellen sind am elektrischen Verbindungsnetzwerk angeschlossen. Durch Programmierung können einzelne Verbindungen von Logikzellen geschaltet oder unterbrochen werden. Auf diese Weise kann eine nahezu beliebige Verbindung der Zellen untereinander erreicht werden, die jedoch durch die Anzahl der verfügbaren Leitungen begrenzt ist. Innerhalb des Verbindungsnetzwerkes gibt es meist noch speziellere Leitungen für die Verwendung eines globalen Taktsignals. Durch ihren Aufbau kommt das Signal an jeder Logikzelle nahezu zeitgleich an [22].

Je nach Hersteller und Bauform befinden sich neben den drei Grundelementen noch zusätzliche Module auf dem FPGA. Bei den Virtex-II FPGAs von Xilinx sind das Block-RAMs und Multiplizier-Elemente [20].

18 KAPITEL 3. FPGA

In Rahmen dieser Diplomarbeit wurde ausschließlich mit FPGAs von Xilinx gearbeitet, deshalb wird im Folgenden speziell auf die Architektur der Xilinx-FPGAs eingegangen. Die FPGAs anderer Hersteller können von dieser Grundarchitektur abweichen, z.B. durch die Verwendung unterschiedlicher Logikblöcke oder Speichereinheiten. Die oben beschriebene Grundstruktur ist jedoch auch bei ihnen wiederzufinden.

### 3.2.1 FPGAs der Virtex-Serie

Neben den oben genannten Grundelementen besitzen die FPGAs der Virtex-Serie zusätzlich noch DCMs (*Digital Clock Manager*), Block-RAM- und Multiplizier-Elemente.

Durch die unterschiedlich langen Verbindungen erreicht ein Taktsignal die einzelnen CLBs nicht gleichzeitig. Für Pipelines z.B. ist es jedoch wichtig, dass sie synchron getaktet sind, da sonst undefinierte Werte zustande kommen können. Mit Hilfe von Verzögerungsregistern sorgen die DCMs deshalb dafür, dass der Takt alle CLBs gleichzeitig erreicht. Die Block-RAM-Elemente sind SRAM-Elemente, deren Eigenschaften, wie z.B. Bitbreite und Speichertiefe, konfiguriert werden können. Je nach Größe besitzt ein FPGA vier bis 168 solcher Block-RAM-Elemente mit jeweils 18 kBit Speicherkapazität. Sie bieten damit lokale Speicherressourcen, die weit über die Speicherfähigkeit der CLBs hinausgehen. Die Multiplizier-Elemente können 18-Bit-Integer-Zahlen multiplizieren. Sie sind durch fest verdrahtete Logik aufgebaut. Damit ist ihr Flächenbedarf auf dem Chip weitaus geringer als bei gleichartigen Multiplizierern, die durch Verwendung von CLBs implementiert werden [20].

Detailliertere Informationen zu den Virtex FPGAs können den Datenblättern [31, 32] entnommen werden.

### 3.2.2 Konfigurierbare Logikblöcke (CLBs)

Die konfigurierbaren Logikblöcke eines FPGAs werden auch als CLBs (*Configurable Logic Blocks*) bezeichnet. Die Anzahl der CLBs auf einem FPGA variiert zwischen den einzelnen Herstellern und Architekturen. Die in der *Cray XD1* verwendeten Virtex-4 FPGAs (XC4VLX140) von Xilinx besitzen beispielsweise 152.064 CLBs [8, 31]. Die Anzahl und Komplexität der CLBs ist außerdem ein Maß für die logische Größe und Leistungsfähigkeit eines FPGAs. Da jedoch die Bauform der CLBs von Hersteller zu Hersteller variiert, gibt man die Leistungsfähigkeit meist in so genannten Gatteräquivalenten an. Die Anzahl der Gatteräquivalente gibt an, wieviele NAND-Gatter zur Realisierung der Komplexität des FPGAs notwendig wären. Dieses Maß stammt aus dem Bereich der *Gate Arrays*. Da die Logikblöcke der FPGAs jedoch nicht wie Gate Arrays aus einzelnen Gattern aufgebaut sind, bietet dieses Maß für FPGAs einen großen Ermessensspielraum. Zudem gibt es für die erforderliche Umrechnung keine einheitlichen Regeln, so dass die Hersteller verschiedene Maßstäbe anlegen. Die angegebenen Gatteräquivalente sind daher nur eine grobe Richtlinie [3, 22, 29].

Ein CLB der Virtex-Serie von Xilinx besteht aus drei Grundelementen (siehe Abb. 3.3(a)): einer Switch-Matrix, Slices und einer Verdrahtungstruktur.

Die Switch-Matrix verbindet den CLB mit dem Verbindungsnetzwerk des FPGAs. Je nach Konfiguration des FPGAs lässt sie die Signale durch oder blockiert sie. Die durchgelassenen Signale werden über ein schnelles Verbindungsnetzwerk an die Slices weitergeleitet.

Abbildung 3.3: Struktur eines CLBs und einer Slice-Einheit der Virtex-Serie

Ein CLB besitzt vier Slices. Abbildung 3.3(b) zeigt die Struktur einer solchen Slice-Einheit. Ein Slice besteht aus zwei Funktionsgeneratoren, zwei Speicherelementen, Multiplexern, Carry-Logik und weiterer arithmetischer Logik. Die Funktionsgeneratoren, oder auch LUTs (*Look-up Table*) genannt, besitzen vier Eingänge (bei Virtex-5 sind es sechs) und einen Ausgang. Eine LUT kann eine beliebige logische Funktion (NAND, XOR, AND, Multiplexer, usw.) aus den Eingangssignalen realisieren. Dies geschieht, indem in einem kleinen Speicher für jeden Zustand der Eingänge der Wert abgelegt wird, den der Ausgang annehmen soll. Für Funktionen, die mehr Eingänge erfordern, als eine einzige LUT besitzt, können mehrere LUTs direkt miteinander verschaltet werden. Darüber hinaus lassen sich LUTs noch als serielle Schieberegister oder RAMs konfigurieren. Um *sequentielle Logik* zu ermöglichen besitzen die Slices Register, die als *Flipflops* oder *Latches* verwendet werden können. Die Multiplexer-Elemente erlauben die Kombination der Funktionseinheiten sowie die Verknüpfung logischer Zwischenergebnisse mit anderen Slices des CLBs. Die zusätzliche Logik in den Slices dient der Implementierung schneller arithmetischer Operatoren, wie z. B. Integer-Addierern oder Zählern [20, 32].

### 3.3 Programmierung von FPGAs

FPGAs werden programmiert, indem ein so genannter Konfigurationsbitstrom auf den Chip transferiert wird. Nach der Konfiguration verhält sich der Baustein wie eine für eine Anwendung speziell konstruierte integrierte Schaltung. Im Unterschied zu ASICs kann das elektronische Verhalten eines FPGAs jederzeit durch erneute Konfiguration geändert werden. Die Konfiguration SRAM-basierter FPGAs ist jedoch flüchtig, d. h., dass der FPGA bei Wegnahme der Stromversorgung seine Programmierung verliert. Auf den meisten FPGA-Boards platziert man deshalb neben den FPGA ein wiederbeschreibbares *EEPROM*, in welchem der Konfigurationsbitstrom gespeichert wird. Beim Einsetzen der Stromzufuhr wird der Bitstrom dann aus dem EEPROM auf den FPGA geladen [22]. Ein Schaltungsdesign, auf dem der Konfigurationsbitstrom für den FPGA basiert, wird im Folgenden FPGA-Design genannt [20].

20 KAPITEL 3. FPGA

Hardware-Entwicklungsablauf

Software-Entwicklungsablauf

Abbildung 3.4: Entwicklungsablauf von Hardware- und Softwareentwicklung im Vergleich

### 3.3.1 Unterschied Hardware- und Softwareprogrammierung

Zwischen Hardware- und Softwareprogrammierung gibt es einige grundlegende Unterschiede. Ein Hardwaredesign ist die physikalische, ein Softwaredesign die logische Implementierung einer Funktionalität. Bei der Hardwareprogrammierung implementiert man für ein mikroelektronisches System einen bestimmten Umfang an Befehlen. Man programmiert also einen Prozessor, wobei die Befehle durch digitale Schaltungen realisiert werden. Zusammen mit einem Speicher und darin befindlichen Programmen als Abfolge solcher Befehle kommt man zum Begriff der Software [6].

Aufgrund dieser unterschiedlichen Definitionen ergeben sich auch Abweichungen beim Ablauf von Hardware- und Softwareentwicklungen. Abbildung 3.4 zeigt den Entwicklungsablauf von Hardware- und Softwaredesigns.

Die klassische Vorgehensweise bei der Softwareentwicklung beginnt mit der Beschreibung eines Designs, bzw. eines Algorithmus in einer höheren Programmiersprache, wie C, C++, Fortran, usw. Der Compiler übersetzt diesen Quellcode in Maschinensprache. Die vom Compiler generierten Module werden anschließend vom Linker zu einem ausführbaren Programm zusammengefügt. Um die Korrektheit des Algorithmus zu prüfen, wird das ausführbare Programm mit verschiedenen Testbeispielen getestet. Bei einer falschen Ausgabe, wird der Fehler im Quellcode gesucht und beseitigt. Danach wird erneut übersetzt, gelinkt und getestet, solange bis alle Testbeispiele fehlerfrei durchlaufen.

Der Entwicklungsablauf von Hardwaredesigns beginnt wie bei der Softwareentwicklung mit der Beschreibung eines Designs bzw. einer elektronischen Schaltung in einer Programmiersprache. Diese Sprache ist jedoch keine höhere Programmiersprache, sondern eine Hardwarebeschreibungssprache oder kurz HDL (*Hardware Description Language*). Die bekanntesten HDLs sind zur Zeit VHDL (*Very High Speed Integrated Circuit HDL*) und Verilog. Bevor das beschriebene Design auf

den FPGA gebracht wird, wird es simuliert. Treten hier Fehler auf, wird der HDL-Code entsprechend korrigiert und erneut simuliert. Ist die Simulation schließlich fehlerfrei, wird in der Synthese eine Netzliste erzeugt und diese anschließend in ein binäres Format konvertiert. Das so codierte Design wird im so genannten *Place & Route* auf dem FPGA platziert. Zum Schluss wird der Bitstrom generiert. Mit speziellen, vom Hersteller mitgelieferten Werkzeugen wird dann nochmals die Korrektheit des Designs überprüft, während es auf dem FPGA läuft. Treten dabei Fehler auf, werden wieder Änderungen am HDL-Code vorgenommen und alle Stufen erneut durchlaufen [28]. Auf die einzelnen Stufen der Hardwareentwicklung wird im Verlauf dieses Kapitels genauer eingegangen.

Bei der Entwicklung von Hardwaredesigns hat man also die Möglichkeit vor der eigentlichen Implementierung das Design zu simulieren und auf Fehler hin zu untersuchen. Während die Simulation bei der Hardwareentwicklung zwingend erforderlich ist, ist sie bei der Softwareentwicklung überflüssig. Ein Grund dafür ist die Zeit, die für eine Übersetzung des Designs benötigt wird. Die Übersetzungszeiten für Softwaredesigns sind in der Regel kurz. Um den Bitstrom eines Hardwaredesigns zu erzeugen, benötigt man dagegen wesentlich mehr Zeit. Die Generierung eines Bitstroms zum Lennard-Jones-Potential (B.2) beispielsweise dauerte 10 Minuten. Für das Linked-Cell-List-FPGA-Design (B.3) betrug die Mindestdauer bereits eine halbe Stunde. Für größere Designs sind Übersetzungszeiten von einem Tag und mehr realistisch [28]. Neben dem Zeitfaktor spielt die Simulation außerdem für den Schutz der Systemkomponenten eine große Rolle. Wird ein fehlerhaftes Design auf den FPGA geladen, ist es möglich, dass dadurch Systemkomponenten beschädigt werden [28].

### 3.3.2 Hardwareentwicklungsablauf

Wie schon erwähnt, wird ein FPGA programmiert, indem ein Konfigurationsbitstrom auf den FPGA transferiert wird. Um einen solchen Bitstrom zu einem FPGA-Design zu erzeugen gibt es durch hochentwickelte Designwerkzeuge eine ähnlich hohe Abstraktion der Programmierung, wie zwischen Hochsprachenprogrammierung und Maschinencode.

#### **HDL-Code**

Die Hochsprachen der Hardwareprogrammierung sind HDLs, wie VHDL oder Verilog. Mit diesen Sprachen wird nach einer vorgegebenen Syntax und Semantik die zu implementierende Schaltung formuliert. Dabei unterscheidet man zwischen der strukturellen und der verhaltensorientierten Beschreibung. Bei der strukturellen Beschreibung wird durch die Spezifikation von gegebenen Bausteinen und deren Verbindungsstruktur eine Schaltung "zusammengebaut". Die so beschriebene Schaltung ist unabhängig von einem bestimmten Ausführungszeitpunkt. Bei der verhaltensorientierten Beschreibung steht nicht mehr die Verbindungsstruktur im Vordergrund, sondern das Verhalten der Komponenten. Hierbei werden auch Zeitabhängigkeiten beschrieben [18].

Neben den klassischen HDLs existieren seit neuestem auch hochsprachenorientierte Hardwarebeschreibungssprachen wie Handel-C oder System-C. Diese Sprachen sind von der Syntax her C oder Java sehr ähnlich. Ihr Ziel ist es, in konventionellen Programmiersprachen geschriebene Algorithmen mit speziellen Hardwarecompilern direkt in eine effiziente Hardwarestruktur zu kompilieren. Damit soll es auch Softwareprogrammierern ermöglicht werden, Hardwaredesigns zu implementieren.

22 KAPITEL 3. FPGA

Durch IP-Cores, die in den eigenen HDL-Code eingebunden werden können, wird die Entwicklung von Hardwaredesigns weiter vereinfacht. IP-Cores (IP = *Intellectual Property*) sind vorgefertigte Schaltungsentwürfe, die als Block in anderen Schaltungsdesigns wiederverwendet werden können. Beispiele dafür sind Fifos, Prozessoren, serielle Schnittstellen, Ethernet-MAC-Layer, RAM-Controller, Parallel-IO, etc. [3]. Sie werden von den Herstellern der FPGAs zur Verfügung gestellt. Dabei unterscheidet man zwischen "Hard IP-Cores", die als Netzliste für eine bestimmte FPGA-Technologie geliefert werden, und "Soft IP-Cores", welche als synthetisierbare Schaltungsbeschreibung in einer HDL erhältlich sind.

#### **Simulation**

Die softwarebasierte Simulation eines FPGA-Designs ist notwendig, da das Testen des Designs direkt an der Hardware schwierig ist und sogar Schaden an Hardwarekomponenten anrichten kann. Die Fehlersuche im Echtzeitbetrieb ist aufgrund der hohen Schaltgeschwindigkeiten sehr aufwändig. Des Weiteren sind einige Signale der Schaltung nicht von außen zugänglich, so dass nicht alle Signalverläufe überwacht werden können. Bei der Simulation dagegen sind sämtliche Signale verfügbar. Die einzelnen zeitlichen Verläufe lassen sich leicht überwachen und aufzeichnen. Außerdem besteht keine Gefahr, Schaden anzurichten.

Im Hardwareentwicklungsablauf gibt es zwei Arten der Simulation. Zum einen gibt es die funktionale Simulation. Sie wird durchgeführt, nachdem der HDL-Code zum gewünschten FPGA-Design erzeugt wurde. Hierbei wird die funktionale Korrektheit des Designs getestet. Die andere Art ist die Timing-Simulation. Sie wird nach dem *Place & Route* durchgeführt und berücksichtigt zusätzlich zeitliche Faktoren.

Bei der Durchführung einer Simulation arbeitet man mit Testvektoren oder Testbenches. Testvektoren bestehen aus einer Reihe von Werten, wobei zu jedem Eingangssignal das erwartete Ausgangssignal angegeben ist. Unter Verwendung dieser Eingangssignale wird dann bei der Simulation überprüft, ob die tatsächlichen Ausgangssignale mit den erwarteten übereinstimmen. Für komplexere Simulationen eignen sich Testbenches besser als Testvektoren. Eine Testbench simuliert eine reale Umgebung für das zu testende FPGA-Design. Ihr Vorteil ist, dass sie Eingangssignale auch als Reaktion auf die Signale des zu testenden Designs erzeugen kann. Simulationswerkzeuge, wie beispielsweise *ModelSim* von *Mentor Graphics* [1] erleichtern das Erstellen von Testbenches und die Fehlersuche.

### **Synthese**

Nachdem mit Hilfe der funktionalen Simulation die Korrektheit der Funktion des FPGA-Designs gewährleistet ist, wird das Design synthetisiert. Dabei werden die in der formalen Beschreibung, also dem HDL-Code, festgelegten Elemente auf die vorhandenen Ressourcen des FPGAs abgebildet. Die endgültige FPGA-Implementierung wird jedoch noch nicht festgelegt. Das Ergebnis der Synthese ist die Netzliste. Diese enthält die schaltungstechnische Struktur des FPGA-Designs, also alle verwendeten Ressourcen, ihre Parameter und Verschaltungsstruktur. Außerdem beinhaltet sie Angaben über einzuhaltende Zeitkriterien, Platzierungsinformationen für die einzelnen Elemente, Startzustände von Speicherelementen und die Zuordnung der nach außen gerichteten Signale zu den Gehäusepins [18, 20].

Auch für die Synthese existieren geeignete Werkzeuge, die die Entwicklung eines FPGA-Designs erleichtern und die Generierung der Bitströme automatisieren. Solche Synthesewerkzeuge sind beispielsweise ISE [4] und *Synplify* [2].

#### **Place & Route**

Die Netzliste dient als Eingabe für das so genannte *Place & Route*. Hier wird die endgültige FPGA-Implementierung festgelegt. Die einzelnen Logikelemente werden auf dem FPGA platziert (*Place*), d. h. es wird festgelegt, welche CLBs welche logische Funktion realisieren. Durch ein automatisches Routing-Verfahren werden dann die einzelnen Elemente mit den vorhandenen Verbindungsressourcen miteinander verbunden (*Route*), d. h. es wird festgelegt, welche Leitungen freigeschaltet werden.

Dieser Vorgang ist sehr rechenintensiv und kann mehrere Stunden benötigen. Der Zeitaufwand hängt dabei nicht nur von der Komplexität des FPGA-Designs ab, sondern auch vom Grad der Optimierung. Optimierung bedeutet dabei, dass die einzelnen Elemente so platziert werden, dass die Verbindungswege möglichst kurz sind. Dadurch werden die Signallaufzeiten gering gehalten und der Flächenverbrauch für die benutzten Leitungen minimiert. Der Grad der Optimierung ist abhängig vom verwendeten Werkzeug. *Synplify* ermöglicht beispielsweise eine höhere Optimierung als ISE.

Nach dem *Place & Route* wird das reale Zeitverhalten der Schaltung, also die Laufzeit der Signale, berechnet. In der Timing-Simulation wird dann das Design erneut unter Berücksichtigung des Zeitverhaltens simuliert. Außerdem wird noch der längste Pfad bzw. die längste Taktperiode des Designs ermittelt und daraus die maximale *Taktfrequenz* berechnet. Treten dabei Fehler auf, werden diese entsprechend beseitigt und alle Schritte erneut durchlaufen.

Das Ergebnis des *Place & Route* ist schließlich der Konfigurationsbitstrom für den FPGA. Dieser wird auf den FPGA geladen und der Chip damit konfiguriert. Abschließend werden noch Tests mit dem konfigurierten FPGA durchgeführt. Treten hier Fehler auf, müssen erneut Änderungen am HDL-Code vorgenommen werden, solange bis das Design fehlerfrei ist.

### 3.4 Rekonfigurierbare Koprozessoren

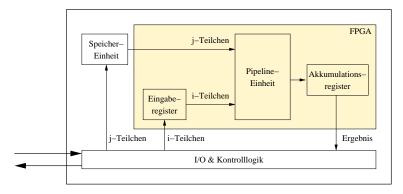

Ein weit verbreitetes Anwendungsgebiet für FPGAs sind rekonfigurierbare Koprozessoren. Bei solchen Koprozessoren handelt es sich um FPGA-basierte Komponenten, die eng mit einem konventionellen Mikroprozessor zusammenarbeiten. Das Ziel eines FPGA-Koprozessors ist nicht, den Prozessor durch eine eigene Hardware zu ersetzen. Die Grundidee besteht vielmehr darin, lediglich zeitintensive Teile eines Algorithmus auf dem FPGA zu rechnen und somit zu beschleunigen. Der restliche Algorithmus wird wie gewohnt vom Mikroprozessor bearbeitet. Die Beschleunigung wird dabei dadurch erreicht, dass die Hardware des Koprozessors durch die FPGAs speziell an den Algorithmus bzw. den entsprechenden Teil des Gesamtalgorithmus angepasst werden kann. Im Falle der Molekulardynamik lassen sich beispielsweise Pipelines zur Berechnung der Wechselwirkungen auf dem Koprozessor realisieren [18].

24 KAPITEL 3. FPGA

Abbildung 3.5: Foto des PROGRAPE-4-Boards

FPGA-Koprozessoren lassen sich auf unterschiedliche Weise realisieren. Eine übliche Variante für rekonfigurierbare Koprozessoren sind PCI-Einsteckkarten. Sie beinhalten in der Regel einen oder mehrere FPGAs, lokale Speicher, ein konfigurierbares Taktsystem und eine schnelle Schnittstelle für die Konfiguration der FPGAs und den Datentransfer [18]. Das PROGRAPE-4-Board ist ein Beispiel für einen FPGA-Koprozessor. Es wird im Folgenden genauer beschrieben.

### 3.4.1 PROGRAPE-4

Das PROGRAPE-4-Board wurde Anfang 2006 am RIKEN (Institute of Physical and Chemical Research) in Wako (Saitama, Japan) entwickelt. Das Board ist die vierte Generation der PROGRAPE-Technologie. Es wurde für die Beschleunigung der Berechnung und Simulation von Vielteilchensystemen konzipiert. Der Name PROGRAPE steht dabei für *PROgrammable GRAPE*.

PROGRAPE ist eine Weiterentwicklung der GRAPE-Technologie. Im Gegensatz zu GRAPE sind die PROGRAPE-Boards jedoch programmierbar. Die Bezeichnung GRAPE bedeutet dabei *GRAvity PipelinE*. Wie der Name vermuten lässt, enthalten die Boards der GRAPE-Technologie eine Pipeline speziell für die Berechnung der Gravitation in astrophysikalischen Vielteilchensystemen. Die GRAPE-Boards berechnen mit Hilfe von ASICs die Gravitationskraft, die Zeitableitung der Gravitationskraft und das Gravitationspotential. Alle anderen für eine Simulation notwendigen Berechnungen werden auf dem Wirtsrechner durchgeführt. Da die Kräfteberechnung 95% der Rechenzeit einer Simulation beansprucht, ist es sinnvoll lediglich diesen Teil zu beschleunigen. Durch ihre fest codierte Hardware ist das Einsatzgebiet der GRAPE-Boards jedoch auf Gravitationsberechnungen beschränkt. Die Idee, einen solchen Beschleuniger auch für andere Probleme, z. B. für Wechselwirkungen, die auf einem Lennard-Jones-Potential basieren, benutzen zu können, führte zur Entwicklung der PROGRAPE-Boards. Dabei wurde die fest codierte Logik des GRAPE durch rekonfigurierbare FPGAs ersetzt [15].

Abbildung 3.6: Architektur des PROGRAPE-4-Boards

Die PROGRAPE-Boards basieren auf dem gleichen Prinzip wie die GRAPE-Boards. Sie dienen als Koprozessoren, d. h. es wird nicht die gesamte Berechnung auf dem Board durchgeführt, sondern lediglich rechenintensive Teile, wie im Fall der Molekulardynamik die Kräfteberechnung. Die restlichen Berechnungen werden vom Wirtsrechner durchgeführt. Im Unterschied zu GRAPE, lassen sich mit PROGRAPE Pipelines für verschiedenste Probleme realisieren [15].

Das PROGRAPE-4-Board besitzt insgesamt 311.040 CLBs. Laut Angaben des Herstellers lässt sich damit eine Grenzleistung von 243,2 GFlops erreichen. Diese Angabe bezieht sich auf gravitative Vielkörperprobleme, in denen keine Kollisionen auftreten. Außerdem ist zu beachten, dass für die Berechnung gravitativer Wechselwirkungen eine geringe Genauigkeit (26 Bit zur Darstellung einer Fließkommazahl) ausreichend ist, was zusätzlich Ressourcen auf den FPGAs spart. Das Board kostet 1.543 € [12].

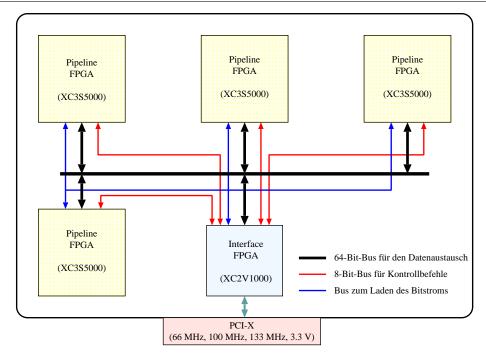

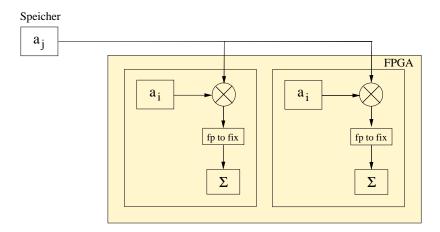

Abbildung 3.6 zeigt die Architektur des PROGRAPE-4-Boards. Es besteht aus insgesamt fünf FPGAs, vier Spartan-3 FPGAs (XC3S5000) und einem Virtex-II FPGA (XC2V1000) der Firma Xilinx. Die vier Spartan-3 FPGAs können vom Wirtsrechner mit einer beliebigen Konfiguration versehen werden. Sie werden im Folgenden Pipeline-FPGAs genannt. Sie können nur mit dem gleichen Pipelinedesign konfiguriert werden. Auf dem Board befinden sich also immer mindestens vier parallele Pipelines. Durch entsprechende Programmierung (siehe Kapitel 4) lassen sich auch mehrere Pipelines auf einem FPGA unterbringen, wodurch eine noch höhere Parallelität erreicht werden kann. Der Virtex-II FPGA kann nicht mit einem Pipelinedesign versehen werden. Er dient als Schnittstelle und wird im Folgenden Interface-FPGA genannt. Er erhält die Daten und Befehle vom Wirtssystem über einen PCI-X-Bus und leitet sie entsprechend an die Pipeline-FPGAs weiter. Kontrollbefehle, z. B. zum Starten einer Berechnung, werden über einen 8-Bit-Bus weitergeleitet. Die einzelnen Daten werden über einen 64-Bit-Bus zu den Pipeline-FPGAs gesendet. Der Interface-FPGA regelt dabei gleichzeitig die Verteilung der Daten auf die einzelnen FPGAs. Der Konfigurationsbitstrom wird über einen gesonderten Bus auf die vier Pipeline-FPGAs geladen. Das PROGRAPE-4-Board arbeitet mit Taktfrequenzen von 66, 100 und 133 MHz [14].

26 KAPITEL 3. FPGA

Abbildung 3.7: Entwicklungsablauf eines FPGA-basierten Rechners

Zur Programmierung eines PROGRAPE-Boards muss neben dem Pipelinedesign auch ein Schnittstellen-Design für den Interface-FPGA entwickelt werden. Dies ist sehr aufwändig. Um die Programmierung zu vereinfachen, wurde deshalb die Software PGR speziell für die PROGRAPE-Boards entwickelt.

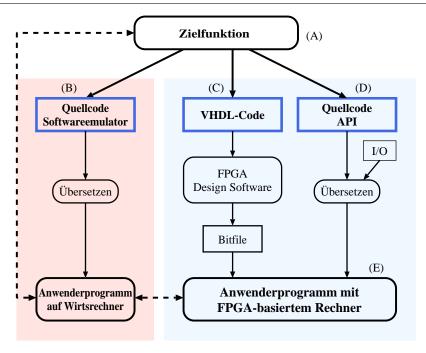

### 3.4.2 Entwicklung eines FPGA-basierten Rechners

Die Entwicklung eines FPGA-Koprozessors zur Beschleunigung eines Algorithmus ist sehr aufwändig. Grundsätzlich lässt sich der Ablauf in folgende fünf Schritte zerlegen:

#### (A) Zielfunktion:

Zunächst wird die Zielfunktion spezifiziert, das Problem, das mit Hilfe des Koprozessors beschleunigt werden soll. In der Regel ist dies ein Algorithmus, dessen Softwareimplementierung bereits existiert. Aus dieser Implementierung gilt es die zeitintensiven Teilbereiche ausfindig zu machen, die sich für eine Berechnung auf dem FPGA eignen. Außerdem werden in diesem Schritt die Ein- und Ausgabedaten für den Koprozessor definiert, respektive die Festlegung des Zahlenformats, der Wortlängen für Daten und arithmetische Operationen und die Beschreibung des Datenflusses für die Berechnung der Zielfunktion.

### (B) Softwareemulator:

In diesem Schritt wird ein Softwareemulator entwickelt. Mit Softwareemulator ist hier die Softwareimplementierung der Zielfunktion gemeint. Bei der Extrahierung von Teilbereichen zur Berechnung auf dem FPGA kann es notwendig sein, die ursprüngliche Implementierung der Zielfunktion zu modifizieren. Mit diesem Emulator wird also getestet ob der geänderte Algorithmus immer noch korrekt arbeitet, d. h. ob das in (A) spezifizierte Design die Zielfunktion korrekt berechnet. Mit dem Emulator können später außerdem Vergleichsrechnungen durchgeführt werden, um zu überprüfen, ob das FPGA-basierte Hardwaredesign korrekt

und mit der gewünschten Genauigkeit rechnet. Des Weiteren wird hier die Schnittstelle (API) zwischen Wirtsrechner und Koprozessor definiert.

### (C) Hardwaredesign:

Als nächstes erfolgt die Implementierung des Hardwaredesigns für den Koprozessor in einer Hardwarebeschreibungssprache. Dies beinhaltet nicht nur das Design für die FPGAs, sondern auch die Definition der Kontrolllogik und der Schnittstelle zum Wirtssystem. Aus diesem Quelltext wird wie in Kapitel 3.3.2 beschrieben der Bitstrom zur Konfiguration der FPGAs bzw. des Koprozessors erzeugt.

### (D) **API**:

Damit das Wirtssystem mit dem FPGA-Board kommunizieren kann, muss auf dem Wirtssystem eine Schnittstellensoftware implementiert werden. Diese regelt die Kommunikation und Datenübertragung zwischen dem Wirtssystem und dem Koprozessor. Die Schnittstellensoftware sollte außerdem eine eventuell nötige Konvertierung der Datenformate übernehmen.