**Thomas Breuer**

51

JÜLICH PORSCHUNGSZENTRUM

Forschungszentrum Jülich GmbH Peter Grünberg Institute (PGI) Electronic Materials (PGI-7)

## Development of ReRAM-based Devices for Logic- and Computation-in-Memory Applications

**Thomas Breuer**

Bibliographic information published by the Deutsche Nationalbibliothek. The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

Publisher and Forschungszentrum Jülich GmbH

Zentralbibliothek Distributor:

52425 Jülich

Tel: +49 2461 61-5368 Fax: +49 2461 61-6103

Email: zb-publikation@fz-juelich.de

www.fz-juelich.de/zb

Cover Design: Grafische Medien, Forschungszentrum Jülich GmbH

Printer: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2017

Schriften des Forschungszentrums Jülich Reihe Information / Information, Band / Volume 51

D 82 (Diss., RWTH Aachen University, 2017)

ISSN 1866-1777 ISBN 978-3-95806-270-2

Vollständig frei verfügbar über das Publikationsportal des Forschungszentrums Jülich (JuSER) unter www.fz-juelich.de/zb/openaccess.

# List of included own publications

Parts of the present work have been published in journals or on international conferences. The involvement of each topic (especially format and extent of citation and text) has been individually discussed and agreed with the coauthors. The respective publishers and copyright holders have been asked for reuse of each text or figure.

- i) T. Breuer, L. Nielen, B. Roesgen, R. Waser, V. Rana, and E. Linn, "Realization of Minimum and Maximum Gate Function in Ta<sub>2</sub>O<sub>5</sub>-based Memristive Devices", *Scientific Reports*, vol. 6, p. 23967, 2016. (See [1] and Section 2.2 and 7.1.)

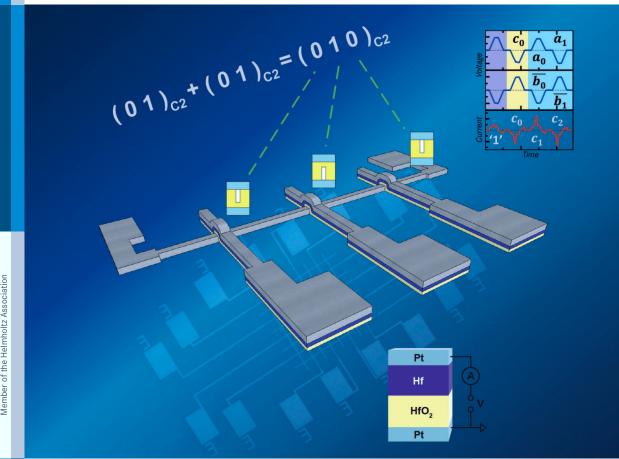

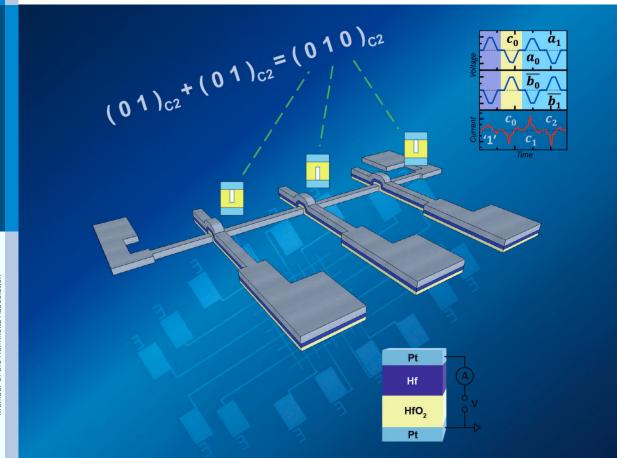

- ii) T. Breuer, A. Siemon, E. Linn, S. Menzel, R. Waser, and V. Rana, "A HfO<sub>2</sub>-Based Complementary Switching Crossbar Adder", *Advanced Electronic Materials*, vol. 1, no. 10, pp. n/a-n/a, 2015. (See [2], Abstract, Subsection 2.1.3, Section 7.3 and Chapter 8.)

- iii) T. Breuer, A. Siemon, E. Linn, S. Menzel, R. Waser, and V. Rana, "Low-current operations in  $4F^2$ -compatible Ta<sub>2</sub>O<sub>5</sub>-based complementary resistive switches", *Nanotechnology*, vol. 26, no. 41, p. 415202, 2015. (See [3], Chapter 2 and 6.)

- iv) T. Breuer, W. Kim, S. Menzel, V. Rana, A. Siemon, E. Linn, and R. Waser, "Low-Current and High-Endurance Logic Operations in  $4F^2$ -compatible TaO<sub>x</sub>-based Complementary Resistive Switches", in *Silicon Nanoelectronics Workshop (SNW)*, IEEE, pp. 1-2, 2014. (See [4] and Subsection 7.2.2, © 2014 IEEE.)

- v) A. Siemon, T. Breuer, N. Aslam, S. Ferch, W. Kim, J. van den Hurk, V. Rana, S. Hoffmann-Eifert, R. Waser, S. Menzel, and E. Linn, "Realization of Boolean Logic Functionality using Redox-based Memristive Devices", *Adv. Funct. Mater.*, vol. 25, no. 40, pp. 6414-6423, 2015. (See [5] and Subsection 7.2.2.)

- vi) A. Schönhals, D. Wouters, A. Marchewka, T. Breuer, K. Skaja, V. Rana, S. Menzel, and R. Waser, "Critical ReRAM Stack Parameters Controlling Complimentary versus Bipolar Resistive Switching", in *IEEE International Memory Workshop (IMW)*, pp. 1-4, May 2015. (See [6], Subsection 2.1.3, Section 5.1 and Subsection 5.2.2, © 2015 IEEE.)

#### **Abstract**

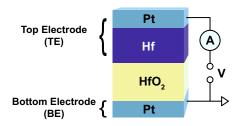

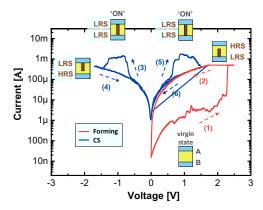

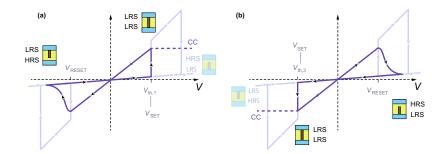

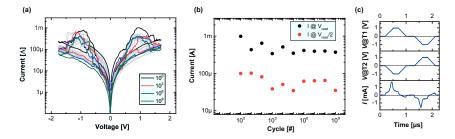

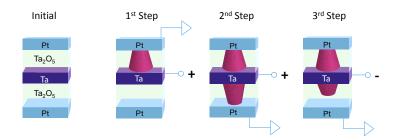

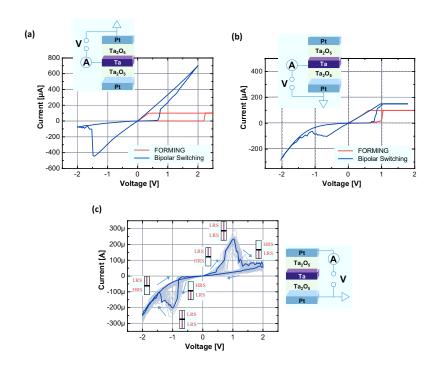

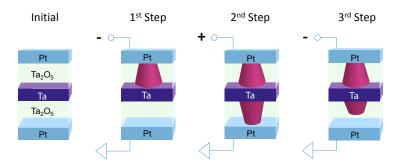

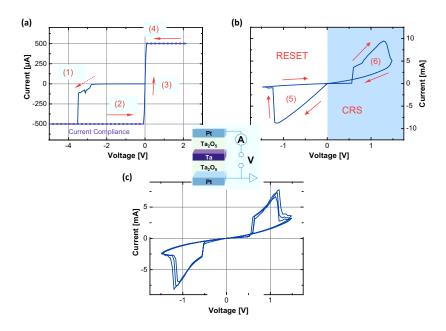

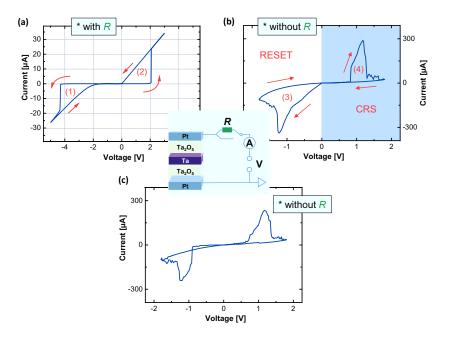

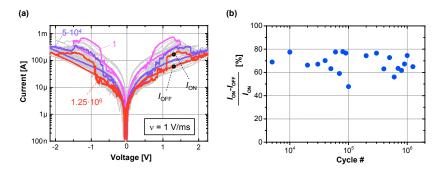

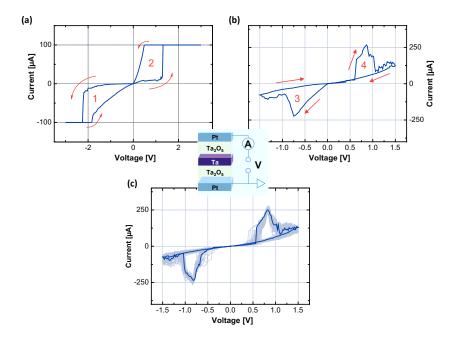

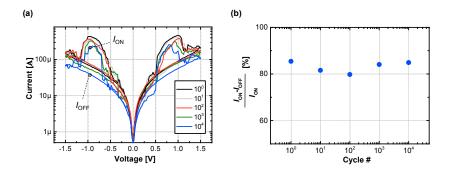

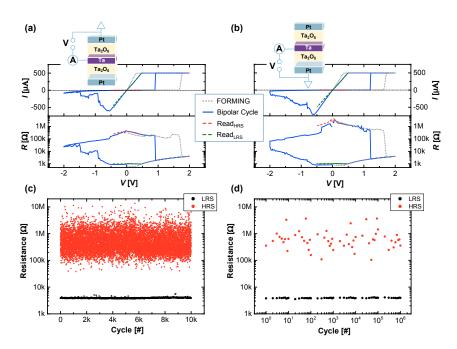

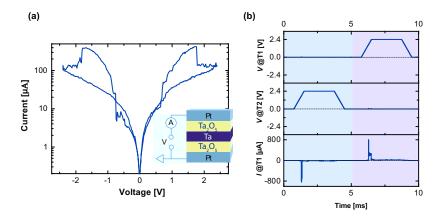

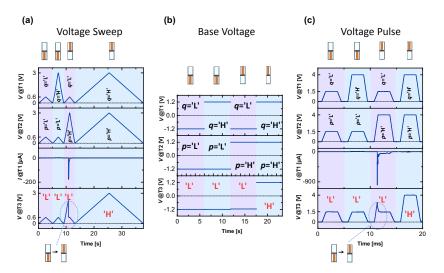

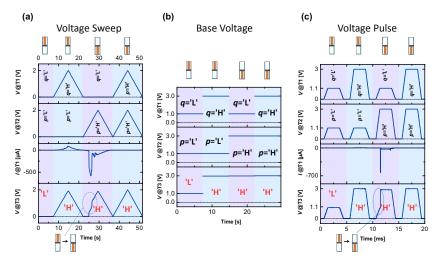

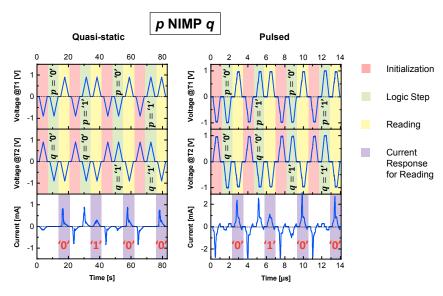

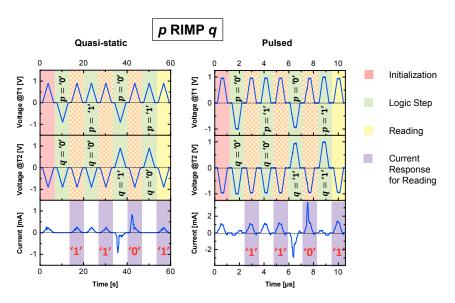

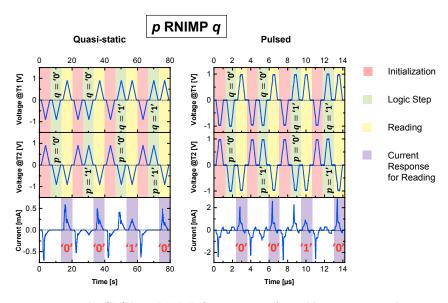

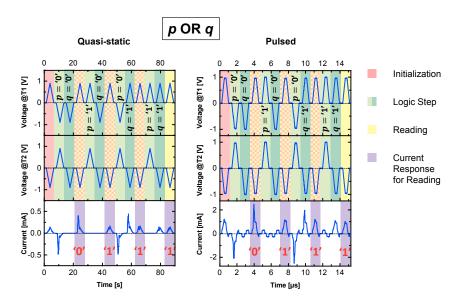

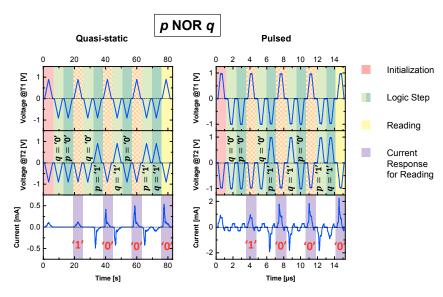

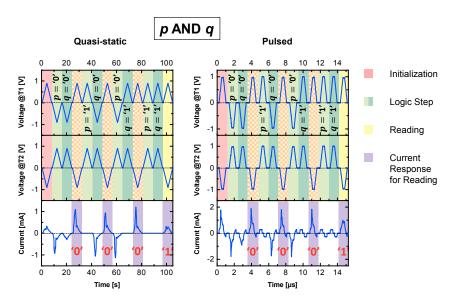

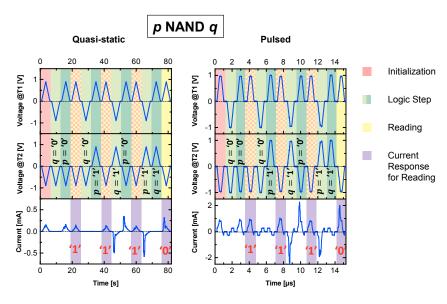

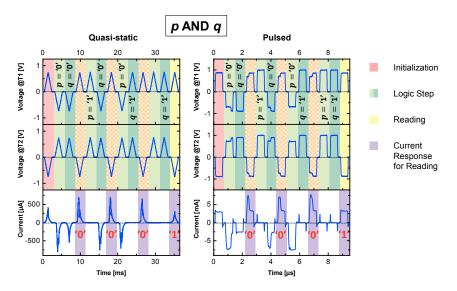

Rapid growth of future information technology depends on energy-efficient computation and ultra-high density data storage. Non-volatile redox-based resistive switching memory (ReRAM) devices offer logic-in-memory and cognitive computing capabilities and can redefine von Neuman computer architecture. The Complementary Resistive Switch (CRS), where two bipolar switching cells are vertically stacked, is a promising candidate and enables integration of highly dense passive nano-crossbar arrays in  $4F^2$  structure (with minimum feature size F). Due to the intrinsic non-linearity, the need for selector devices in the array is no longer required. Firstly, Ta<sub>2</sub>O<sub>5</sub>-based two-terminal devices (no access to the middle electrode (ME)) are considered, which facilitate simple integration and low fabrication cost. Their electrical characteristics are compared with switching of three-terminal devices (exhibiting access to the ME), in order to investigate the impact of single cell properties on the whole CRS. Initial electroforming process in the three-terminal devices is carried out by applying voltage stimuli to individual ReRAM cells. However, two-terminal devices require introduction of a novel procedure, which enables separate and controlled electroforming for low-current operations ( $< 300 \,\mu\text{A}$ ). Such devices (with improved endurance about 10<sup>6</sup> cycles) have been used to implement fuzzy logic in terms of MIN / MAX gates (concept suggested by Klimo et al. in [7], Nielen et al. in [8]), which could enable small-size sorting networks. To reduce fabrication complexity, vertically stacked Pt|HfO<sub>2</sub>|Hf|Pt ReRAM stacks are investigated, which offer similar I-V characteristics to the CRS, referred to as Complementary Switch (CS). The intrinsic complementary switching can be modified externally to eight-wise and counter-eight-wise bipolar switching. However, the Hf electrode thickness has also impact on the actual switching mode. Further process parameters, such as deposition rate of HfO<sub>2</sub>, have much more of an impact on the initial device. Next, integration of the CS into 1×8 passive crossbar arrays is demonstrated. First, the implementation of all Boolean CRS-logic operations (concept suggested by Linn et al. in [9]) with the CS is proven, showing remarkable endurance (10<sup>9</sup> cycles). Afterward, two in-memory adders (concepts introduced by Siemon et al. in [10]) are experimentally demonstrated, which perform addition and subtraction operations.

Altogether, this could pave the way for next-generation information technology for parallel processing-in-memory architecture, which is implemented by ReRAMs embedded in energy-efficient, ultra-dense  $4F^2$  passive crossbar arrays.

#### Kurzfassung

Die rapid ansteigende Nachfrage nach Lösungen für zukünftige Informationstechnologien lässt sich unmittelbar von dem enormen Bedarf an energieeffizienten Computersystemen und extrem hoher Datenspeicherdichte ableiten. Nichtflüchtige redox-basiserte resistive Speicher (ReRAM) können die derzeitige Datentechnologie mittels cognitive computing und der Möglichkeit, Logikoperationen direkt in der Speichereinheit durchzuführen (logic-in-memory), revolutionieren. Insbesondere der Complementary Resistive Switch (CRS), der aus zwei antiseriell angeordneten, vertikal gestapelten bipolar schaltenden ReRAM-Zellen besteht, ist für diese innovativen Anwendungen ein geeigneter Kandidat und ermöglicht zudem die Einbettung von  $4F^2$ -Strukturen (mit der minimalen Strukturgröße F) in enorm dichte passive nano-crossbar arrays. Aufgrund der intrinsischen Nichtlinearität muss nicht auf selector devices für die Ansteuerung einzelner Speicherelemente zurückgegriffen werden. Zunächst werden Ta<sub>2</sub>O<sub>5</sub>basierte two-terminal CRS (ohne Zugang zur Mittelelektrode) betrachtet, die die Vorteile einer einfachen Integration in Schaltkreise und niedriger Produktionskosten aufweisen. Deren elektrische Kennlinien werden mit denen von three-terminal devices (mit Zugang zur Mittelelektrode) verglichen, um so den Einfluss der beiden einzelnen Zellen auf den gesamten CRS zu untersuchen. Die initiale electroforming procedure ist für die three-terminal devices sehr einfach zu realisieren, da sich hier, über den Zugang zur Mittelelektrode, die beiden einzelnen Zellen separat kontaktieren lassen. Dahingegen ist es für two-terminal CRS notwendig, eine neuartige Prozedur einzuführen, die ein separates und kontrolliertes electroforming für low-current operations ( $< 300 \,\mu\text{A}$ ) ermöglicht. Diese CRS devices, mit verbesserter endurance von über 10<sup>6</sup> Schaltzyklen, werden für die Implementierung von Fuzzy-Logik in Form von MIN / MAX Gates verwendet (Konzept vorgeschlagen von Klimo et al. in [7] und Nielen et al. in [8]), welche bei der Realisierung von Sortier-Netzwerken helfen könnten. Um den Herstellungsprozess zu vereinfachen, werden simple vertikal gestapelte Pt|HfO<sub>2</sub>|Hf|Pt ReRAMs genauer untersucht. Diese weisen unter bestimmten Bedingungen eine ähnliche I-V-Charakteristik zu der des CRS auf und werden in dem Fall als Complementary Switch (CS) bezeichnet. Das intrinsische komplementäre Schalten kann durch äußere Einwirkung ins eight-wise oder counter-eight-wise bipolare Schalten überführt werden. Darüber hinaus hat

ebenso die Hf-Elektrodendicke eine Auswirkung auf den intrinsischen switching mode. Weitere Prozessparameter, wie die Depositionsrate von HfO<sub>2</sub>, haben dahingegen lediglich einen Einfluss auf die initialen Eigenschaften des Speicherelements. Die optimierten CS-Zellen (endurance von  $10^9$  Schaltzyklen, operation current  $\sim 500\,\mu\text{A}$ ) werden in  $1\times 8$  passive crossbar arrays eingebettet. Anhand dieser devices wird zunächst die Umsetzbarkeit von Boolean-Logik-Funktionen demonstriert (Konzept vorgestellt von Linn et al. in [9]). Im Anschluss werden zwei in-memory adders experimentell getestet, welche Additionen und Subtraktionen durchführen (Konzept eingeführt von Siemon et al. in [10]). Diese Resultate belegen deutlich die funktionale Effizienz des crossbar adder approach, der einen wichtigen Weg für höchst fortgeschrittene ReRAM-basierte computing-in-memory architecture ebnet.

## Contents

| ontei   | $_{ m nts}$                                    |                                                                                                                     | vii                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intr    | oducti                                         | ion                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1     | Scope                                          | of this work                                                                                                        | 4                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Rec     | lox-bas                                        | sed Resistive Switching Memory                                                                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1     | Switch                                         | ning Mechanisms                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.1.1                                          | Bipolar Switching                                                                                                   | 7                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.1.2                                          | Complementary Resistive Switching                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 2.1.3                                          | Complementary Switching                                                                                             | 11                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2     | Logic                                          | and Computation Properties (State of the Art)                                                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 2.2.1                                          | Boolean Logic                                                                                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 2.2.2                                          |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Exp     | erime                                          | ntal Technology                                                                                                     | 15                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1     | Analy                                          | tical Methods                                                                                                       | 15                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.1.1                                          | Thin Film Characterization                                                                                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.1.2                                          | Electrical Characterization                                                                                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.2     | Device                                         | e Preparation                                                                                                       | 24                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3 2 1                                          | Plasma Ashing                                                                                                       | 24                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 0.2.1                                          | 1 1001110 110111116                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 3.2.2                                          |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | -                                              | DC / RF Sputtering                                                                                                  | 24                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.2.2                                          |                                                                                                                     | 24<br>25                                                                                                                                                                                                                                                                                                                                                                                                               |

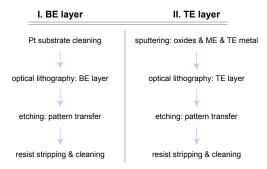

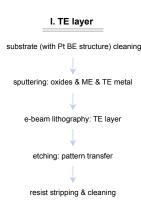

| Dev     | 3.2.2<br>3.2.3<br>3.2.4                        | DC / RF Sputtering                                                                                                  | 24<br>25                                                                                                                                                                                                                                                                                                                                                                                                               |

| Dev 4.1 | 3.2.2<br>3.2.3<br>3.2.4                        | DC / RF Sputtering                                                                                                  | 24<br>25<br>28<br><b>29</b>                                                                                                                                                                                                                                                                                                                                                                                            |

|         | Intr<br>1.1<br>Red<br>2.1<br>2.2<br>Exp<br>3.1 | 1.1 Scope  Red→x-bas  2.1 Switch 2.1.1 2.1.2 2.1.3 2.2 Logic 2.2.1 2.2.2  Experime 3.1 Analy 3.1.1 3.1.2 3.2 Device | Introduction  1.1 Scope of this work  Redox-based Resistive Switching Memory  2.1 Switching Mechanisms 2.1.1 Bipolar Switching 2.1.2 Complementary Resistive Switching 2.1.3 Complementary Switching 2.1 Logic and Computation Properties (State of the Art) 2.2.1 Boolean Logic 2.2.2 Fuzzy Logic  Experimental Technology  3.1 Analytical Methods 3.1.1 Thin Film Characterization 3.1.2 Electrical Characterization |

|   | 4.3    | Compl            | ementary Resistive Switching Devices            |

|---|--------|------------------|-------------------------------------------------|

|   |        | 4.3.1            | Three-Terminal Devices                          |

|   |        | 4.3.2            | Two-Terminal Devices                            |

| 5 | Res    | istive S         | Switching in HfO <sub>2</sub> -based Devices 51 |

|   | 5.1    | Compl            | ementary vs. Bipolar Switching 51               |

|   | 5.2    | Electro          | oforming / SET / RESET                          |

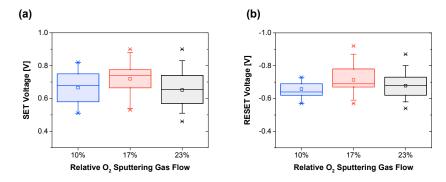

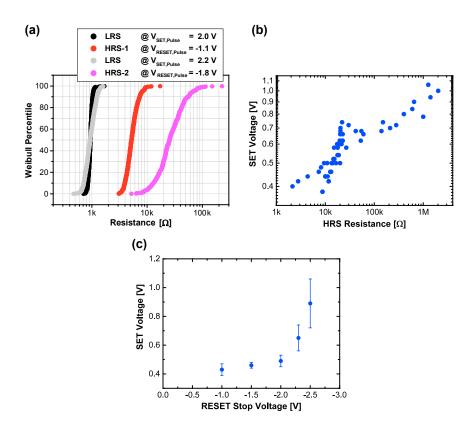

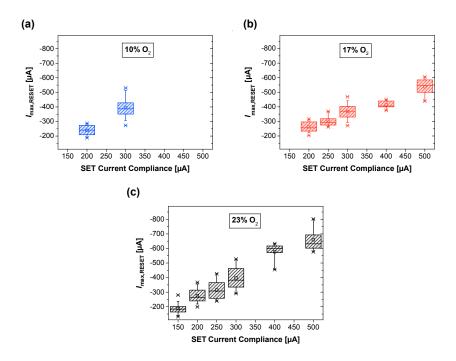

|   |        | 5.2.1            | $O_2$ Sputtering Gas Flow Variation             |

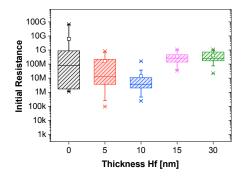

|   |        | 5.2.2            | Hf Electrode Thickness Variation 62             |

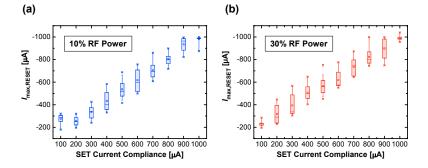

|   |        | 5.2.3            | RF Sputtering Power Variation 65                |

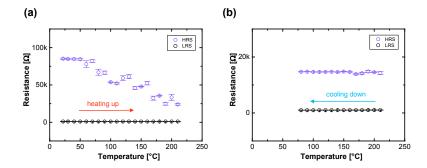

|   | 5.3    | Reliab           | ility                                           |

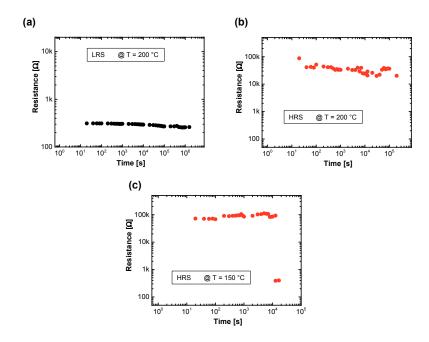

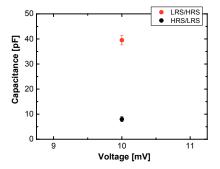

|   |        | 5.3.1            | State Stability                                 |

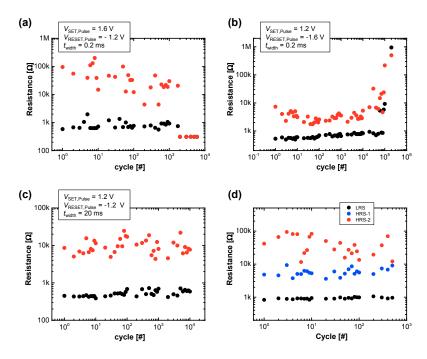

|   |        | 5.3.2            | Endurance                                       |

|   | 5.4    | Conclu           | sion                                            |

| 6 | $Ta_2$ | ${ m O}_5$ -base | ed CRS Device Optimization 79                   |

|   | 6.1    | Low-C            | urrent Operation in CRS                         |

|   |        | 6.1.1            | Three-Terminal CRS                              |

|   |        | 6.1.2            | Two-Terminal CRS                                |

|   | 6.2    | Conclu           | sion                                            |

| 7 | ReI    | RAM I            | Device Application 95                           |

|   | 7.1    | Minim            | um / Maximum Gate                               |

|   |        | 7.1.1            | Basics                                          |

|   |        | 7.1.2            | Proof-of-Concept                                |

|   |        | 7.1.3            | Discussion                                      |

|   | 7.2    | Logic-i          | in-Memory (CRS-Logic)                           |

|   |        | 7.2.1            | Basics                                          |

|   |        | 7.2.2            | Proof-of-Concept                                |

|   |        | 7.2.3            | Discussion                                      |

|   | 7.3    | Compu            | ntation-in-Memory                               |

|   |        | 7.3.1            | Basics                                          |

|   |        | 7.3.2            | Proof-of-Concept                                |

|   |        | 7.3.3            | Discussion                                      |

| 8  | Con   | clusion and Outlook            | 143   |

|----|-------|--------------------------------|-------|

|    | 8.1   | Device Improvement $\dots$     | . 143 |

|    | 8.2   | Device Applications            | . 145 |

|    | 8.3   | Outlook                        | . 147 |

| A  | App   | pendix A                       | 149   |

|    | A.1   | Electron Beam Lithography      | . 149 |

|    | A.2   | Thin Film Surface Roughness    | . 151 |

|    | A.3   | Material Stoichiometry         | . 152 |

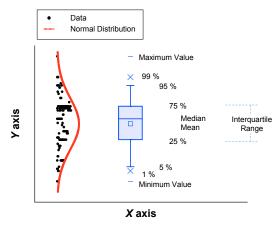

|    | A.4   | Statistical Definitions        | . 152 |

|    | A.5   | Associative Capacitive Network | . 153 |

| Li | st of | Figures                        | 157   |

| Li | st of | Tables                         | 161   |

| Bi | bliog | graphy                         | 163   |

| Αd | knov  | wledgement                     | 181   |

## Chapter 1

#### Introduction

In the age of the Internet of Things, i.e. the internetworking of smart devices, electronic memories have become an integral part of humans, as personal electronic devices such as laptops, digital cameras, smart phones and tablets are equipped with memory devices. To have better consumer experience, these memory elements should be of higher capacity, faster access speed (read and write) and as well as economically obtainable.

Conventional memory technologies, Flash, SRAM and DRAM cannot satisfy the technological and commercial requirements (e.g. due to physical limitations). Therefore, emerging memory technologies have been actively pursued for the next generation of non-volatile data storage. The ideal characteristics for future memory device include fast programming speed (< ns), low operation voltage (< 1 V), low power / energy consumption ( $\sim$  fJ/bit for write), long retention time (> 10 years), high write / read endurance (>  $10^{16}$  cycles) and excellent scalability (< 10 nm).

New memory devices include Phase-Change RAM (PCRAM), Ferroelectric RAM (FeRAM), Magnetoresistive RAM (MRAM) and Resistive / Redoxbased RAM (RRAM / ReRAM). Table 1.1 shows the comparison of the characteristics of current and future memory technologies. The ReRAM devices can be scaled down below the five nanometer-mark with  $4F^2$  feature size.[11–13] Recently, write / erase time in sub-nanosecond range has been realized.[14] Additionally, the energy consumption for toggling the memory state can be reduced to a range of 0.1 fJ.[11] Having compatibility with CMOS, ultra-high dense integration capability, ReRAM has advantages over other memory tech-

nologies and is being pursued for different application domains such as neuromorphic and reconfiguration logic. Furthermore, these memristive devices (memory resistors) offer also the capability to merge logic and computation with memory units. [9, 10, 15-20] This approach avoids the data transfer between separated memory and computation units as in the conventional von Neumann computer architecture.

Beyond these application fields, the ReRAM is also a promising candidate for innovative artificial intelligence systems, which are modeled on the highly efficient human brain. In recent years, scientists have tried to imitate the human brain capabilities with current CMOS technology. However, the power consumption is one of the biggest drawbacks in these machines. For instance, Watson IBM supercomputer is capable of processing 80 trillion operations (teraflops) per second and consumes 2.3 MW.[21,22] It runs about 2,800 processor cores and has 16 terabytes of working memory. On other hand, the human brain, an example for artificial synapses and neuromorphic processor units, contains 100 billion neurons and consumes only 25 W. Therefore, new and innovative concepts / technologies have to be considered, which enable significantly more energy efficient memory and computation applications. Due to clear similarities to synapses[23–26] and promising switching properties, the ReRAM might be able to meet all requirements.

Table 1.1: Current baseline and prototypical memory technologies. Values in brackets depict best projected achievements. The data are based upon the International Technology Roadmap for Semiconductors (ITRS) from 2013.[13]

|                                                                                               | ReRAM (Bipolar Switch)                                                      | DRAM                                                                                    | SRAM                                                   | NAND Flash          | FeRAM                                     | STT-MRAM                                                                      | PCRAM                                      |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------|-------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------|

| (Non-)Volatile                                                                                | Non-Volatile                                                                | Volatile                                                                                | Volatile                                               | Non-Volatile        | Non-Volatile                              | Non-Volatile                                                                  | Non-Volatile                               |

| Feature<br>size [nm]                                                                          | 9(>)                                                                        | 36 (9)                                                                                  | 45 (10)                                                | 16 (> 10)           | 180 (65)                                  | 65 (16)                                                                       | 45 (8)                                     |

| Cell Area $(2D)$ [F <sup>2</sup> ]                                                            | 4                                                                           | 6 (4)                                                                                   | 140                                                    | 4                   | 22 (12)                                   | 20 (8)                                                                        | 4                                          |

| Write/Erase<br>Time [ns]                                                                      | < 1                                                                         | < 10                                                                                    | 0.2 (0.07)                                             | $10^6/10^5$         | 65 (< 10)                                 | 35 (1)                                                                        | 100 (< 50)                                 |

| Retention<br>Time                                                                             | $> 10\mathrm{yr}$                                                           | $\begin{array}{c} 64\mathrm{ms} \\ (\mathrm{refresh} \\ \mathrm{required}) \end{array}$ | as long as voltage is applied                          | $> 10\mathrm{yr}$   | $> 10\mathrm{yr}$                         | $> 10\mathrm{yr}$                                                             | $> 10\mathrm{yr}$                          |

| Write<br>Cycles                                                                               | $(>)10^{12}$                                                                | > 10 <sup>16</sup>                                                                      | > 10 <sup>16</sup>                                     | $10^{5}$            | $10^{14} \ (> 10^{15})$                   | $10^{12} (> 10^{15})$                                                         | 109                                        |

| Write<br>Voltage [V]                                                                          | (<)1                                                                        | 2.5 (1.5)                                                                               | 1 (0.7)                                                | 15                  | 1.3-3.3 $(0.7-1.5)$                       | 1.8 (<1)                                                                      | 3 (< 3)                                    |

| $\begin{array}{c} \operatorname{Read} \\ \operatorname{Voltage} \left[ V \right] \end{array}$ | 0.1                                                                         | 1.8 (1.5)                                                                               | 1 (0.7)                                                | 4.5                 | 1.3 - 3.3 $(0.7 - 1.5)$                   | 1.8 (<1)                                                                      | 1.2 (< 1)                                  |

| Write<br>Energy [J/bit]                                                                       | $ \begin{array}{c c} 1 \times 10^{-13} \\ (1 \times 10^{-16}) \end{array} $ | $   \begin{array}{c c}     4 \times 10^{-15} \\     (2 \times 10^{-15})   \end{array} $ | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $1 \times 10^{-10}$ | $3 \times 10^{-14}$ $(7 \times 10^{-15})$ | $\begin{array}{c c} 2.5 \times 10^{-12} \\ (1.5 \times 10^{-13}) \end{array}$ | $6 \times 10^{-12} $ $(1 \times 10^{-15})$ |

#### 1.1 Scope of this work

The present work is focused on material / device engineering and implementation of innovative application concepts for logic- and computation-in-memory operations on the ReRAM. Here,  $Ta_2O_5$ - and  $HfO_2$ -based devices are investigated, which are promising candidates for innovative memory technologies offering excellent switching properties.[27–34]

Chapter 2 gives an overview of fundamental mechanisms involved in the ReRAM, where the focus is on the Valance Chance Mechanism (VCM), which is responsible for resistance change in subsequently demonstrated binary metal oxide devices. The discussion includes the three switching modes (bipolar switching, complementary resistive switching and complementary switching) and the state of the art of logic / computation concepts enabling operations directly in memory units.

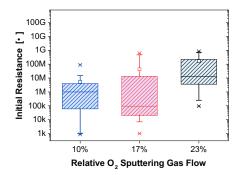

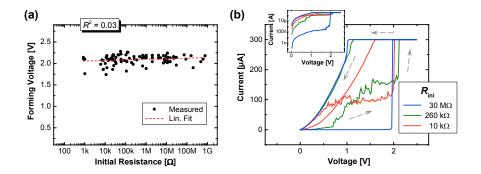

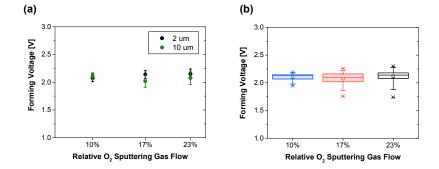

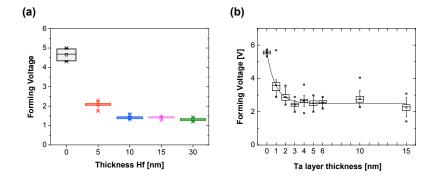

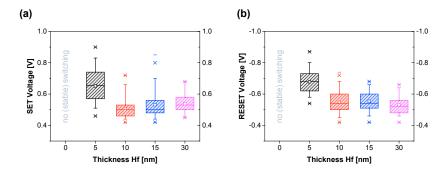

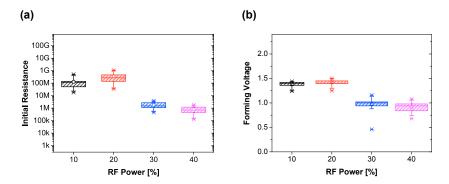

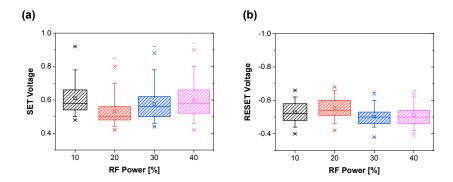

Subsequently, relevant experimental technologies are briefly described in Chapter 3, including analytical methods for material and device characterization / preparation and experimental setups. The detailed preparation and fabrication flow of the individual device types is given in Chapter 4. This also includes material characterization regarding stoichiometry, structure, film thickness and surface topography. For  $HfO_2$ -based devices, several fabrication parameters have been varied, e.g. Hf electrode thickness and sputtering power / growth rate. The impact of these parameters on device characteristics is investigated in Chapter 5, especially initial resistance, the electroforming process, state reliability and transition from bipolar to complementary switching mode.

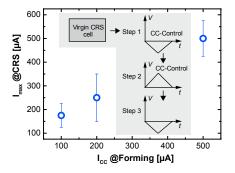

In Chapter 6, the focus is on the optimization process of  ${\rm Ta_2O_5}$ -based devices showing complementary resistive switching. Three- and two-terminal switches (offering an / no access to the middle electrode) are compared and a novel forming procedure, which implements low-current operations for micro- and nanometer scaled devices, is introduced.

Finally, three promising ReRAM applications are considered in Chapter 7: MIN / MAX gate (fuzzy logic; concept introduced by Klimo  $et\ al.$ [7] and Nielen  $et\ al.$ [8]), CRS-logic (logic-in-memory; concept introduced by Linn  $et\ al.$ [9]) and multi-bit crossbar adders (computation-in-memory; concept introduced

by Siemon  $et\ al.[10]$ ) Relevant basics of these concepts are comprehensibly explained and pre-measurements and proof-of-concept experiments are presented. At the end, the summary of this research and the outlook for future efforts are given in Chapter 8.

## Chapter 2

## Redox-based Resistive Switching Memory

#### 2.1 Switching Mechanisms

The redox-based random access memory, referred to as ReRAM, is one of the most auspicious emerging non-volatile memory (NVM) devices by reason of: low-voltage operating mode, brilliant capability of energy efficiency, outstanding scalability, compatibility to 3D fabrication and silicon technology and high endurance. [18, 19, 35–42] On the basis of switching properties, ReRAMs can be categorized into the unipolar switch, which can be programmed and erased with the same bias polarity, and the bipolar switch (BS) needing opposite bias polarities. [42, 43]

Different switching mechanisms for the resistive switching phenomena have been reported in literature. However, the most relevant ones are: Thermo-Chemical Mechanism (TCM)[44], Valence Change Mechanism (VCM)[42] and ElectroChemical Metallization (ECM)[45]. All of them are dominated by redox-related chemical processes. Due to higher endurance[27] and better uniformity, VCM-based bipolar ReRAMs are of most interest. These devices can be implemented by single layer or bi-layer structures with  ${\rm TiO}_x[46]$ ,  ${\rm HfO}_x[47]$  and  ${\rm TaO}_x[27]$  etc.

#### 2.1.1 Bipolar Switching

Bipolar switching is predominately observed in asymmetric stacks, the binary metal oxides are sandwiched between low work function and high work function metal electrodes. The device resistance can be changed reversibly from the high resistance state (HRS or '0', sometimes: 'OFF' state) to the low resistance state (LRS or '1', sometimes: 'ON' state) by external voltage or current stimuli. Both states are non-volatile, i.e. no further voltage needs to be applied to keep the actual state.

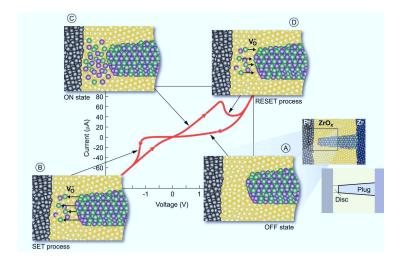

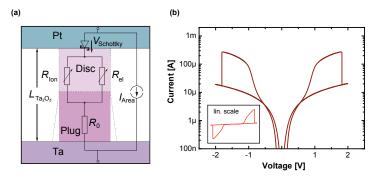

Figure 2.1 presents a typical I-V characteristic, which has been measured on a  $Pt|ZrO_x|Zr$  memory stack by applying quasi-static voltage ramps to the Pt electrode. Here, the resistance change is described by a filamentary switching model.[48] The conducting filament is ruptured and regrown during the switching as depicted by the inset sketches (A) to (D) in Figure 2.1. The filament consists of oxygen vacancies (green balls,  $V_O^{\bullet\bullet}$  in Kröger-Vink notation[49,50]) and reduced metal ions (purple balls). Here, "reduced" is relative to the ideal crystal and  ${}^{\bullet}$  denotes a positive charge relative to the perfect lattice, i.e. the  $V_{\mathcal{O}}^{\bullet \bullet}$  is twice positively charged. At the beginning, the memory device is in the 'OFF' state (A) offering a gap (in the disc region) between the permanent filament (plug region) and the Pt electrode. Applying a negative voltage to the Pt electrode, the SET process starts (B), when positively charged oxygen vacancies are attracted into the gap increasing the local conductivity and closing the filamentary rupture. After the SET process, the memory cell is in the conductive 'ON' state (C), which is stable as long as the applied voltage does not change the polarity and the RESET process does not start (D).

The difference between HRS and LRS can be physically explained by considering the oxygen vacancy profile  $[V_O^{\bullet\bullet}]$  and the energy-band model. The  $ZrO_x|Zr$  interface is assumed as ohmic contact and does not change significantly during the switching. However, the  $Pt|ZrO_x$  interface exhibits a Schottky barrier within the disc region, whose width depends on oxygen vacancy concentration as depicted in Figure 2.2. Oxygen vacancies, which are attracted into the disc region during the SET process, serve as dopants[48] and the barrier width is inversely proportional to root of the dopant concentration.[51] In the LRS, the barrier width is negligible and the contact serves as an ohmic resistor. Repelling the vacancies into the plug region (during RESET process) increases the barrier width and the current is vehemently reduced.

Figure 2.1: Valence Change Mechanism (VCM) switching scheme. The quasi-static I-V characteristic of a  $\text{Pt}|\text{ZrO}_x|\text{Zr}$  valence change memory. Consider, the displayed voltage is applied to the Pt electrode, whereas the Zr electrode is grounded. The sketches A to D present the switching stages. The oxygen vacancies are represented by green balls, whereas the purple ones indicate the Zr ions being in a lower valence state. (A) HRS (or 'OFF' state), (B) SET process, (C) LRS (or 'ON' state) and (D) RESET process.[48] (Reprinted with permission from the publisher.)

Figure 2.2: Sketch of oxygen vacancy profile  $[V_O^{\bullet\bullet}](x)$  (red line), the conducting band diagram  $W_c(x)$  (blue line) and the Fermi level  $W_F$  (black, dashed line) in the disc / plug region of the n-conducting filament in the HRS (left) and LRS (right). The illustration of the SET and RESET process considering the oxygen ion / vacancy movement (center).[48]) (Reprinted with permission from the publisher.)

#### 2.1.2 Complementary Resistive Switching

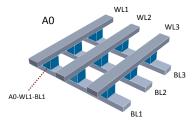

For ultra-high dense NVM applications, the ReRAM-based devices feature integration in passive  $4F^2$  (minimum feature size F) crosspoint arrays.[3, 52] Stacking of the crossbars enables further enhancing of the device embedding density to  $4F^2/n$ , where n is the number of stacks.[53] The memory elements arranged in rows and columns are highly inter-connected in this configuration. Therefore, the architecture suffers from intrinsic sneak paths.[12,54] Furthermore, this issue is aggravated, if the accessed memory cell being in HRS is surrounded by cells being in LRS. As a consequence, the sensed read current does not only pass the accessed cell. Surrounding paths with potential lower resistance also contributes to the overall current. This additional current causes misinterpretation of the actual memory device state.

The sneak current issue scales up with the crossbar array size. [3, 12] Thus, the number of embedded devices in the array is limited. [54] In order to solve this problem, various types of selector devices are available, which enable dense integration: ovonic threshold switch [55], mixed ionic electronic conductors [56], rectifying based  $Pt|TiO_2|Pt[57-59]$ , MOSFET integration [60,61] and metalinsulator transition materials [62]. However, up to now, these devices are not capable of satisfying significant requirements in terms of scalability and device properties in large  $4F^2$  crossbar arrays. For instance, MOSFET-based 1T1R architecture requires larger foot-print and in most cases the current density of available selectors is insufficient to drive ReRAMs.[12]

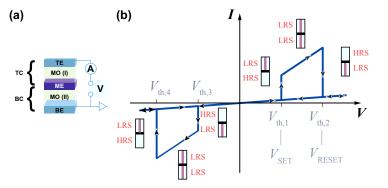

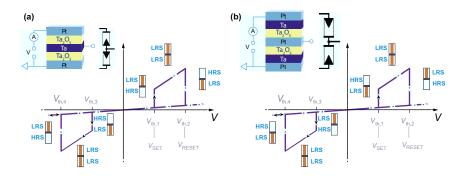

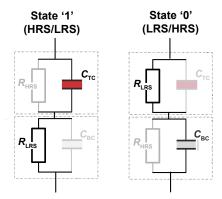

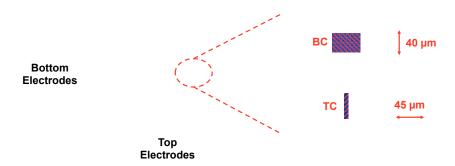

As an answer to this problem, Linn et al. have introduced the concept of the Complementary Resistive Switch (CRS).[12] This device is composed of two bipolar switching ReRAMs, which are referred to as top cell (TC) and bottom cell (BC). In the present thesis, both cells are partially vertically stacked and anti-serially connected (see Figure 2.3a).[3,12,63,64] The CRS inherently comprises a memory and selector element. Figure 2.3b demonstrates the schematical I-V switching curve of the CRS. The insets illustrate the resistance scheme of the CRS states. Independent of the concrete device state, below specific threshold voltages, the CRS offers a high resistance (cf.  $V_{\text{th},1}, V_{\text{th},3}$ ). This enables reduction of general leakage currents. Furthermore, CRS crossbar arrays are capable to fulfill the fundamental requirements for parallel write / read operations in storage-class memories, in order to guarantee high-speed data

Figure 2.3: (a) CRS stack scheme. Two anti-serially stacked ReRAM cells, top cell (TC) and bottom cell (BC). Each cell consists of the middle electrode (ME), metal oxide (MO) and top electrode (TE) / bottom electrode (BE) layer. (b) I-V scheme of the CRS. For the switching process, the threshold voltages  $V_{\text{th},1}$  to  $V_{\text{th},4}$  have to be considered. The insets indicate the actual resistance state of the BC and TC. These cells are complementarily toggled between a low resistance state (LRS) and a high resistance state (HRS).[3] (Redrawn with permission from the publisher.)

processing. [65] Additionally, ReRAMs exhibit the capability of processing-in-memory operating mode (CRS-logic), which has been suggested in [8–10] and both experimentally demonstrated in [1, 2, 5] and Section 7.2. The two CRS states LRS/HRS (TC in LRS, BC in HRS) and HRS/LRS (TC in HRS, BC in LRS) are identified with the logical '0' and '1' and used for information storage. [3] The 'ON' state, where both cells are in the LRS is only a transition, whenever the device changes from '0' to '1' and contrariwise. The 'OFF' state, where BC and TC are highly resistive, does not occur during cycling. This state only exists for the initial non-electroformed CRS. [3] This promising CRS concept has been successfully proven for several metal oxides materials, e.g.  $\rm HfO_2$ ,  $\rm Ta_2O_5$  and  $\rm TiO_2$ . [66–70]

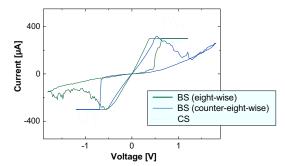

#### 2.1.3 Complementary Switching

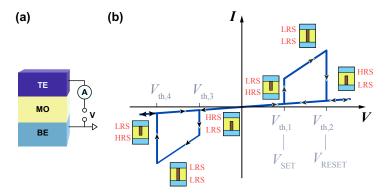

Lately, the complementary switch (CS) has been reported, which is implemented by a single VCM-based ReRAM cell (e.g.  $TiN|HfO_x|TiN$  or  $Pd|TaO_x|Ta|Pd$ ).[31, 69] These devices show similar I-V curves to the CRS device (cf. Figure 2.4), but offering a simpler stack structure.[31, 69] In con-

Figure 2.4: (a) CS stack scheme. The device consists of the top electrode (TE), the metal oxide (MO) and bottom electrode (BE) layer. (b) I-V scheme of CS device. For the switching process, the threshold voltages  $V_{\text{th},1}$  to  $V_{\text{th},4}$  have to be considered. The switching occurs at the two MO-electrode interfaces, which are complementarily toggled between a low resistance state (LRS) and a high resistance state (HRS). The insets indicate the actual CS state.

trast to the CRS, the CS is based on switching at two interfaces in the same cell.[6,71] The individual switching stages are discussed for the HfO<sub>2</sub>-based CS in Section 5.1. Since the CS features an inherent selector property, large crossbar arrays can be realized without the need of additional selector devices.

## 2.2 Logic and Computation Properties (State of the Art)

#### 2.2.1 Boolean Logic

Performance of next-generation information technology depends strongly on the successful research on novel device materials as well as efficient circuit architecture and software.[2] For this progress, passive crossbar arrays composed of redox-based resistive switches (ReRAMs) are highly auspicious candidates for ultra-high dense data storage and energy-efficient processing applications.[9, 41, 42, 72]

The conventional von Neumann architecture is based upon separated units: central processing unit (CPU) and memory unit (MU).[2] Data are transferred

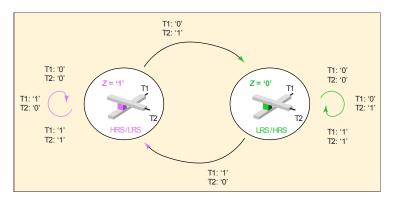

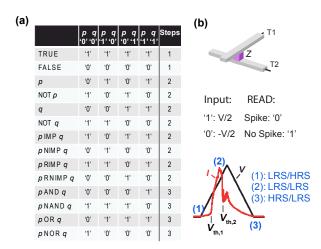

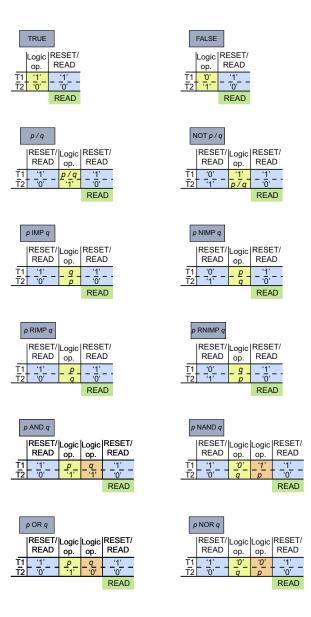

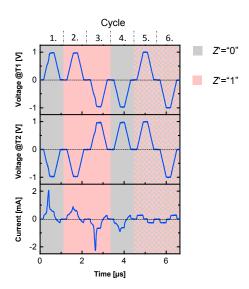

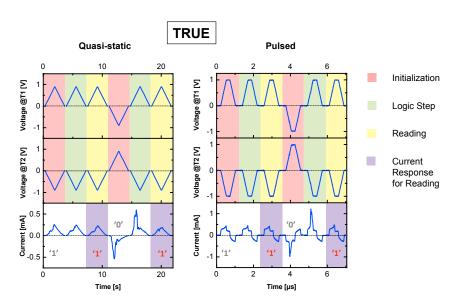

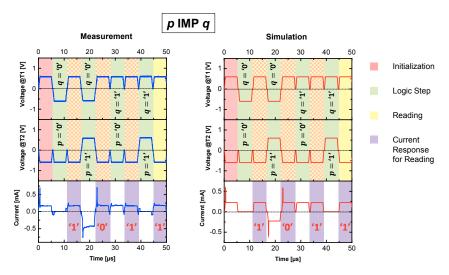

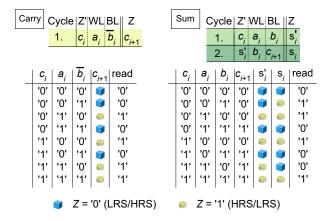

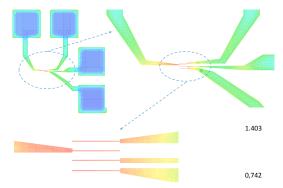

between MU and CPU via a connection line. However, the rate for data transfer is constrained. This issue is referred to as the von Neumann bottleneck. [73] In order to overcome this limitation, novel concepts have been proposed, where computations are performed directly within the memory (processingin-memory). Such concepts have recently been presented for ReRAM technology. [17, 74, 75] In those concepts, the control unit (CU) and the MU are both on the same chip. The CU is based on CMOS and the MU on ReRAM technology, which are compatible. In opposition to the conventional approach, this CU does not control only the memory operating mode, but also the logic operating mode. Rosezin et al. have demonstrated that the CRS enables realization of elementary implication operations and can be considered as a finite state machine. [76] Figure 2.5 depicts the comparison of the CRS with a finite state machine. Recently, Linn et al. have proposed CRS-logic concept.[9] The CRS-logic has several features: (1) The actual memory state is used as a third input variable for the next operation. [10] (2) The logic operations are processed by CS / CRS devices and (3) afterwards the information is directly / inherently stored in the final memory location.[9] Thus, this approach is a logic-in-memory concept designed for CS and CRS arrays, but can be used for all bipolar switching devices. Moreover, for this specific concept, two multi-bit crossbar adder schemes have been introduced by Siemon et al.[10] Proof-of-concept electrical measurements for logic- and computationin-memory applications on crossbar arrays are presented in Section 7.2 and 7.3.

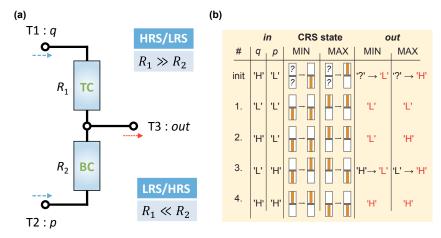

#### 2.2.2 Fuzzy Logic

Considering fuzzy logic, the truth values are not restricted to 0 (completely false) and 1 (completely true), rather any real number between 0 and 1 is possible. Inspired by this idea, Šuch and Klimo have proposed a concept, where two-memristive circuits are applied to realize Maximum and Minimum (MAX / MIN) logic gates.[7] The suggested gate structure exhibits two antiserially connected single ReRAMs, that means the device structure can be compared with the conventional CRS, but it offers an additional access to the middle electrode (ME).[3,75,77,78] In general, one MIN / MAX gate exhibits two inputs and one output for sensing the lower or higher input potential.[79]

Figure 2.5: The CS / CRS as finite state machine. Depending on the actual device state Z ('0' or '1'), the state switches only for specific input signals at the terminals T1 and T2.

Concerning binary considerations, these devices corresponds to OR / AND logic gates. [79,80] These elements can be applied for processing of analog signals and can enable implementation of sorting networks [81], while considering several constraining specifications. [1,8,79]

The corresponding three-terminal CRS devices are demonstrated and characterized in Chapter 6. Šuch *et al.* have demonstrated the characteristic of actual memristive devices differs strongly from the ideal memristor characteristic. Nonetheless, a reliable MIN / MAX gate operating mode is facilitated by considering few limitations regarding the input signal amplitude.[78, 79] Despite of these limitations, which are extensively discussed, the proposed structures are highly suitable to feature fuzzy logic operations.[1]

## Chapter 3

## Experimental Technology

#### 3.1 Analytical Methods

#### 3.1.1 Thin Film Characterization

#### 3.1.1.1 X-Ray Reflectometry

X-ray reflectometry (XRR) is used to determine the thickness of thin films sputtered on substrates in order to determine the film growing rate. This method is based on reflection principle of the x-ray light and can fundamentally be described with Snell's law

$$n_0 \cos \theta = n_1 \cos \theta_1 \tag{3.1}$$

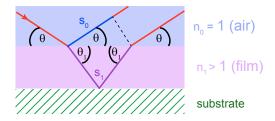

where  $\theta$  is the angle of the incident beam (to the surface), which propagates through the medium of refractive index  $n_0$ , and  $\theta_1$  is the beam refraction angle in the medium with a refractive index  $n_1$  (cf. Figure 3.1). The substrate thickness is assumed to be infinite in comparison to the thin film. Therefore, the intensity of the beam is neglected, which is refracted from the substrate and reflected back at the substrate-plate interface.

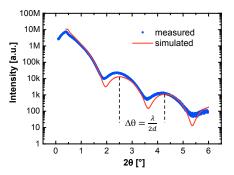

Figure 3.1 shows the optical path difference  $\Delta s$  between directly reflected wave and the refraction wave ( $\Delta s = s_1 - s_0$ ). For constructive interference,  $\Delta s$  has to be a multiple integer n of the beam wavelength  $\lambda$ . Depending on the incident angle, both waves interfere constructively or destructively. The measured x-ray reflectivity shows oscillations (Kiessig oscillations[82]) as function of the

Figure 3.1: X-ray reflection at the thin single layer (deposited on substrate). The beam incides with the angle  $\theta$  from air (refractive index  $n_0=1$ ) and partially reflected from the surface and deflected in the film by the angle  $\theta_1$ . At the film-substrate interface, the beam is reflected toward the surface, where it interferes with the directly reflected beam due to the path difference  $(s_1-s_0)$ . The substrate thickness is assumed to be infinite. Therefore, the diffracted beam is neglected in the substrate.

wavelength, incident angle, refractive indices and the film thickness. The thin film thickness d can be estimated by

$$d = \frac{\lambda}{2\Delta\theta} \tag{3.2}$$

where  $\Delta\theta$  is the distance between two neighboring intensity maxima.[83] An exemplary XRR measurement is presented in Figure 4.1. In the present work, the measurements have been performed by the Philips PW 3020 diffractometer, using a Cu-K<sub>\alpha</sub> x-ray tube ( $\lambda_{K_{\alpha,1}} = 1.540598\,\text{Å}$  and  $\lambda_{K_{\alpha,2}} = 1.544426\,\text{Å}$ ) in the Bragg-Brentano geometry. The thickness is calculated by XRR simulations, fitting film parameters (density, roughness, thickness) in a physically reasonable way.

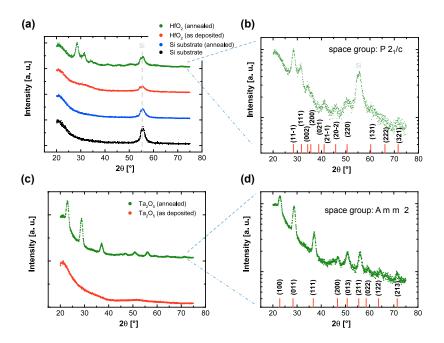

#### 3.1.1.2 X-Ray Diffraction

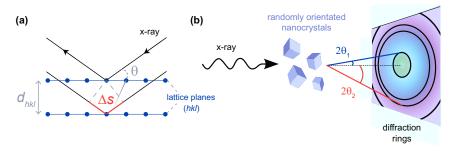

Applying the x-ray diffraction (XRD) mode by the Philips PW 3020 diffractometer enables one to investigate the structural quality of crystalline samples. Due to the periodic crystal lattice, Bragg reflections are observed for incident angles, where the diffracted waves interfere constructively, i.e. Bragg's equation

$$n\lambda = 2d_{hkl}\sin\theta\tag{3.3}$$

Figure 3.2: X-ray diffraction scheme. (a) Diffraction from two parallel crystal planes. The x-ray beam incides at angle  $\theta$ . Scattering peaks are only observed, if the path distance  $\Delta s = 2d\sin\theta$  is a multiple integer of the x-ray wavelength  $\lambda$ . (b) Schematic of the Debye-Scherrer method. The randomly orientated crystals generate diffraction rings without rotating the sample. Radial scanning enables the common  $2\theta$ -scan as shown in Figure 4.2 [84]

has to be fulfilled, where  $n\lambda$  is a multiple integer of the used wavelength and  $d_{hkl}$  refers to the lattice distance of lattice planes (hkl) with the Miller indices h, k and l (cf. Figure 3.2a).

In the case of thin films, the observed reflections depend on the substrate / film orientation. In the present work, the grown thin films however become nanocrystalline by thermal annealing. Due to the random arrangement of such nanocrystals, the full diffractogram is visible without any additional rotation of the substrate (see Figure 3.2b), which is similar to the Debye-Scherrer method for powder diffraction.[84–86] This means that there is always a sufficient number of crystals, which are orientated properly to fulfill Equation 3.3 for each Bragg reflection. The full diffractogram is measured by a single  $2\theta$ -scan.

In order to reduce the signal contribution of the substrate, the grazing incidence X-ray diffraction (GIXRD) method is used. The x-ray beam penetration depth is limited to the upper layer due to the small incidence angle. Smaller angles cause less penetration into the substrate, but require longer observation time (due to a poor signal to noise ratio).[87]

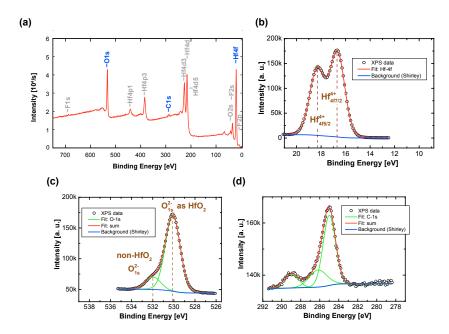

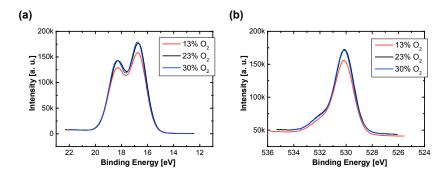

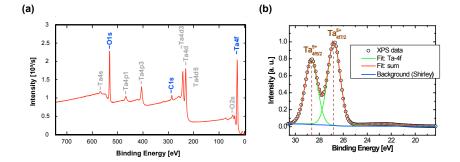

#### 3.1.1.3 X-ray photoelectron spectroscopy

X-ray photoelectron spectroscopy (XPS) is a surface sensitive measurement technique to determine the elemental composition of materials. The sample

is exposed to the x-ray beam with known wavelength (or photon energy). By absorbing photons, core electrons are excited, move toward the surface and leave the material. This is referred to as the photoelectric effect. The penetration depth (for investigations) is limited by the mean free path of electrons in solids: larger distance to the surface increases the probability of inelastic scattering and reabsorption of the excited electron. The loss ratio also depends on the kinetic energy of the electrons and the material composition (structure, density etc.)

The original depth of the non-scattered or elastically scattered electrons, which leave the surface, is up to few nanometers and can be controlled more accurately by the angle resolved XPS method. The kinetic energy  $E_{\rm kin}$  of the free electrons is measured by an electron detector. The binding energy  $E_{\rm b}$  of the electrons, which is typical for each element and the actual chemical bonding (causing chemical energy shift), is calculated by using the law of the conservation of energy

$$E_{\rm b} = E_{\rm ph} - E_{\rm kin} - \phi \tag{3.4}$$

where  $E_{\rm ph} = h\nu$  is the x-ray photon energy (Planck's constant h, the photon frequency  $\nu$ ) and  $\phi$  the work function of the material.

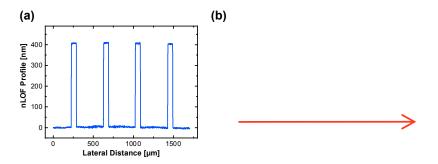

#### 3.1.1.4 Atomic Force Microscopy

To investigate the surface topography with resolution in the sub-nanometer (atomic) range, atomic force microscopy (AFM) is used. A nanoscopic tip, which is fixed to a cantilever, scans the sample surface, where the cantilever movement is realized by piezo elements. The tip is deflected by inter-atomic forces, which are caused by quantum-mechanical effects and Coulomb repulsion. In the present work, the contact mode is used, i.e. there is always a mechanical contact between sample and tip. Measuring tip deflection as function of the location enables one to determine the mapped surface height profile. A laser beam is reflected off the back of the cantilever, where the direction of the reflection is recorded by a position-sensitive photodetector.

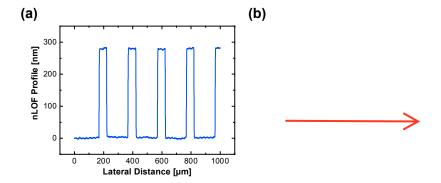

#### 3.1.1.5 Electron Microscopy

Scanning Electron Microscopy The structural quality checks of the patterned samples are performed by a SU8000 scanning electron microscope (SEM). A Schottky cathode supplies electrons, which are accelerated by an anode voltage in the range of several kilovolts (typically  $\sim 10\,\mathrm{kV}$ ). The electron beam is focused on the specimen by an electron-optical system (combination of different electrostatic and electromagnetic lenses).

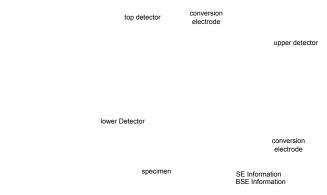

The focused specimen area is scanned by deflection of the electron beam using the optics. The applied acceleration voltage defines the penetration depth of the primary electrons into the specimen. Therefore, the acceleration voltage is used to focus on a specific layer. The striking electrons lose energy by interacting with the specimen matter, which is caused by different mechanisms. X-ray emission, low-energetic secondary and high-energetic backscattered electrons are the main products of the interactions. [88] All these physical particles sensed with individual detectors (cf. Figure 3.3) carry information about the specimen, which are used to draw conclusions on structure and elemental composition.

Particular electron species and x-rays are measured by individual detectors. The specimen is mapped by the intensity variation of detected particles while scanning the investigated area and the observed structures are displayed by black-and-white contrast images. The SU8000 resolution limit is about few nanometers.

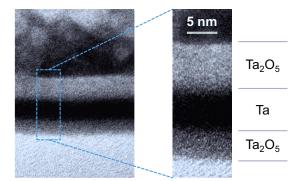

Transmission Electron Microscopy Further structural investigation of the layer / device cross-section is available by transmission electron microscopy (TEM). In contrast to the SEM technique, in the TEM, the accelerated electrons transmit the specimen and material information is only carried by these primary electrons (not by x-rays, backscattered or secondary electrons). Complete transmittance requires high acceleration voltages in the range of 100 kilovolts and electron transparency, i.e. the specimen has to be very thin (about 100 nm or thinner).

The specimen (lamella) is prepared by the focus ion beam technique, where the investigated cross-section is sliced from the sample by the ion beam. Thinner specimens reduce inelastic electron scattering and enable higher resolution.

Figure 3.3: Schematic of electron detection for the SEM. Different detectors are used for low-energetic secondary electrons (SE) and high-energetic backscattered electrons (BSE), which are generated during individual processes and carry information about the specimen.[89]

The sample is not scanned by the electron beam, therefore only a fixed area is exposed by the broad beam and investigated. After leaving the specimen, the electrons pass electron-optics for magnification and are detected by a photosensor (CCD camera). Image resolution in the sub-nanometer range is possible. For quick investigation of the cross-section, a scanning transmission microscope is used, where the electron beam scans the specimen similar to the SEM and only the transmitted electrons are detected.

#### 3.1.2 Electrical Characterization

In the present work, the electrical characterization of resistive switching elements is performed with various tools. The electrical measuring setups are used for applying quasi-static (DC) voltage sweeps with a ramp rate in the range of volt per second and voltage pulses (AC) down to the pulse width range of nanoseconds. Quasi-static means: the voltage ramp is slow to ensure the loading of parasitic capacitance in order to minimize the influence capacitive phenomena on the ReRAM device.[90] Additionally, the memory system has always sufficient time to react on the external driving force (applied voltage) and is nearly always in the quasi-equilibrium. Most of those setups are non-modified standard equipment and are not described in detail.

#### 3.1.2.1 Quasi-static Measurement

The Keithley 2611A Sourcemeter is used for quasi-static measurements applying voltage or current ramps. Here, only voltage driven experiments have been performed, where the voltage can be increased from  $1 \,\mu\text{V}$  up to  $200 \,\text{V}$ . Depending on actual measuring range, the current is sensed from 1 pA up to 1.5 A. The sourcemeter supports contacting the device under test (DUT) by two probes. The signal can be only applied to one probe, whereas the second one is set to ground. For the resistive switching, the maximal device conductivity can be controlled by applying a current compliance (CC). This CC also protects the device against electrical voltage breakthrough. The sourcemeter exhibits an instrument CC. Whenever the measured current reaches the chosen CC level, the system switches to the current source mode and keeps the current constant. As long as the applied voltage is larger than actual voltage drop across the DUT, the system stays in the current source mode. If the actual voltage drop is equal to or smaller than the applied one, the system switches back to the voltage source mode. However, due to the slow response time of the instrument CC, it has to be checked that the timing is sufficient with respect to the experimental requirements (see Chapter 6).

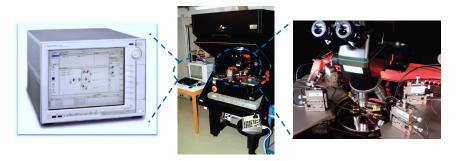

The B1500A Semiconductor Parameter Analyzer (see Figure 3.4) enables both quasi-static voltage sweeps and the application of base voltage levels. The DUT is contacted minimally with two probes, but up to four can be used, where simultaneous signals are applied. This functionality is relevant for such applications as those mentioned in Section 7.1. Using the high resolution source monitoring units, voltages up to 100 V can be applied, where the resolution ranges from  $25\,\mu\text{V}$  up to  $5\,\text{mV}$  (depending on the actual voltage range). Currents up to  $100\,\text{mA}$  can be detected with resolution from  $100\,\text{aA}$  to  $5\,\mu\text{A}$ , which is sufficient for the present experiments. The analyzer also exhibits an instrument CC.

Additionally, the Keithley 4200-SCS is available for quasi-static measurements. This system supports an instrument CC and four probes for contacting the device. Additionally, toggling between the quasi-static and the pulse measure mode (without switching between special probes) is featured. Furthermore,

Figure 3.4: Overview of the experimental equipment (center), B1500A Semiconductor Parameter Analyzer (left) and optical microscope with four probes for contacting the sample.

applying simultaneous voltage stimuli is available by multiple probes.

#### 3.1.2.2 Pulse Measurement Setup

Some endurance and retention experiments have been performed on the Keithley 2611A by applying long pulses in the micro- and millisecond range. However, better analysis regarding endurance and proof-of-concept tests for application is achieved by short pulses in the nanosecond range, which are supported by the Keithley 4200-SCS. Pulses down to few 10 ns can be applied to the DUT, if the response current level is sufficient. For instance, detecting the current by the  $10\,\mathrm{mA}$  range requires a minimum pulse width of about  $160\,\mathrm{ns}$  and a minimum pulse rising / falling time of about  $20\,\mathrm{ns}$ .

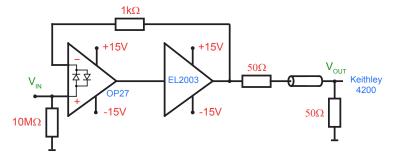

Voltage Sensing Unit. In Section 7.1, three-probe measurements are demonstrated. The voltage is applied to two different probes. A part of the voltage drops across the device (depending on the actual device state). The remaining voltage is measured at the third probe. In the quasi-static setup, this is implemented by the current bias mode, where the current is kept at constant zero ampere by applying a counter voltage to the third probe. The inverse counter voltage is equal to the voltage, which has to be sensed at the third probe. However, this method cannot work for pulsed signals, since instrumental regulation of the inverse voltage is too slow. To measure the resulting voltage at the third probe, a self-designed impedance converter has been connected

directly to the probe, which consists of an operational amplifier (OP27) and a monolithic unity gain buffer (EL2003), operating in the feedback configuration. This device combines features of the single units.[91] A simplified equivalent circuit diagram of the impedance converter is depicted in Figure 3.5. The OP27 offers a high input resistance ( $\sim 3\,\mathrm{G}\Omega$ ) to avoid current flow through the probe, which could distort the voltage measurement.

The EL2003 acts as voltage follower and can supply higher output voltage as compared to the OP27. This is important to drive the  $50\,\Omega$  terminating resistor, which suppresses signal reflections. The feedback signal of the EL2003 is transferred to the second input of the OP27. By using this feedback operation, the OP27 compares the difference between both inputs. The OP27 modifies the output signal as long as the difference disappears.[91,92]

A further  $50\,\Omega$  resistor (input resistance of the Keithley 4200) is serial to the terminating resistor of the impedance converter. Both serve as a voltage divider. The measured voltage at the Keithley 4200 has to be doubled to get the right values. The impedance converter is not an ideal device and additional resistors have to be added, to improve the device characteristics:  $1\,\mathrm{k}\Omega$  between OP27 and EL2003 to prevent oscillations and  $10\,\mathrm{M}\Omega$  at the input to avoid an offset-voltage, which has been up to  $0.7\,\mathrm{V}$  and could destroy or at least change the present device state.[91]

Figure 3.5: Simplified circuit of impedance converter for detecting pulse output signals in MIN / MAX gates.

#### 3.2 Device Preparation

#### 3.2.1 Plasma Ashing

Material structures and compositions have to be well known in order to understand effects and to tailor device properties. Minimal impurities in semiconductor manufacturing can cause huge impacts on the device characteristics. This might aggravate the explanation of the origin of the observed effects. Thus, the sample has to be cleaned sufficiently before starting the individual processing steps.

To remove organic impurities from the surface, especially rest of patterning or protection resist, the TePla 300 microwave plasma system is used. Oxygen plasma is generated by high-frequency radio waves, which ionize low pressure  $O_2$  gas. To remove hardened resist, the plasma power is set to  $600\,\mathrm{W}$  for  $30\,\mathrm{min}$ . Reactive oxygen ions combine with the resist components and form volatile ash particles like  $CO_2$ , which are removed by vacuum pump.

#### 3.2.2 DC / RF Sputtering

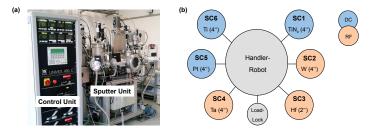

The Oerlikon Univex 450 C is available for metal and oxide thin film deposition. Figure 3.6 shows the sputtering equipment. The sample is loaded into the load lock and chamber atmosphere is pumped down to  $10^{-7}$  mbar by both a turbopump and backing pump in order to achieve clean environmental conditions, avoiding sample contamination. The system offers six separated sputtering chambers (SC) with individual sputtering targets. In this way, mutual contamination of the target materials can be excluded.

In the present work, the following targets are used: Pt (SC5), Ta (SC4) and Hf (SC3). Depending on the particular chamber, the RF or the DC sputtering technique is applied and the target size is either 4 in or 2 in. For enabling physical or reactive sputtering,  $O_2$ , Ar or  $N_2$  are available as process gases. The sample can be transferred by a handler-robot from chamber to chamber to deposit subsequently different material layers without breaking the vacuum. Individual sputtering recipes can be programmed with the control unit. This enables automatic execution of the processes and transfer between used chambers.

Figure 3.6: Sputtering equipment. (a) Overview about control unit and sputter unit. (b) Scheme of the sputter unit. Six separated sputtering chambers for individual (2''/4'') sputtering targets are available. Depending on the chamber, DC or RF sputtering technique is used. The handler-robot transfers the sample automatically from chamber to chamber.

For the sputtering, a static / high-frequency electrical field is applied between target and sample (DC / RF sputtering). The ionized gas particles are accelerated toward the target, where the surface is bombarded and target particles are ejected out. For reactive sputtering, the target material combines with the gas ions. The particles move toward the sample, where they are absorbed on the surface growing the deposition film. All sputtering processes in this work are performed at room temperature.

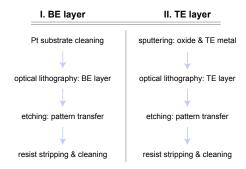

#### 3.2.3 Lithography

Depending on the structure size, the deposited films are patterned by different lithography processes: photolithography (micrometer scaled devices) or electron beam lithography (nanometer scaled devices). However, in both cases the processes are similar. The samples are first coated with a lithography resist layer, which is exposed at selected regions to high-energetic particles (controlled by a lithography mask), whereby chemical bonds are changed. Afterwards, these regions are either soluble or insoluble (positive / negative lithography resist) by the used chemical developer and the mask pattern is transferred to the resist.

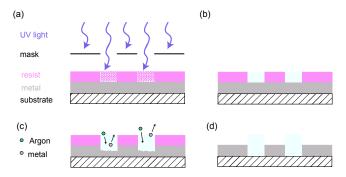

Figure 3.7: Process scheme of film patterning by photolithography. (a) Selective UV light exposure of the positive photoresist by optical mask. (b) Structured resist after development process. (c) Pattern transfer from resist to metal film by physical Ar ion beam etching. (d) Final metal structure on substrate after photoresist removal.

#### 3.2.3.1 Photolithography

A simple process scheme for a particular sample is depicted in Figure 3.7, where the sample is spin coated with positive photoresist. This resist is highly sensitive to UV light. The lithography is performed by Karl Suss MA6 Mask Aligner using an optical mask, which enables selective exposure. The selective regions of the resist, which are exposed to UV light, become soluble and are removed by the chemical developer, whereby the mask layout is transferred to the resist.

#### 3.2.3.2 Electron Beam Lithography

Nanometer scaled structures are realized by the electron beam (e-beam) lithography technique. The spin coated resist is sensitive to high-energetic electrons, which are focused to a fine beam to achieve high resolution. E-beam lithography does not require any optical mask. Using a CAD layout file, the e-beam is controlled for writing the desired pattern (see Figure A.1). Electrons show wave-like characteristics, which are described by the de Broglie hypothesis. The matter wavelength  $\lambda$  is given by

$$\lambda = \frac{h}{p} \tag{3.5}$$

Figure 3.8: Diagram showing the e-beam writing process. Selective exposure of the lithography resist is controlled by electron optics using a CAD layout file.

where h is the Planck's constant and p the electron momentum. Relativistic effects are negligible at acceleration voltages about 50 kV and the momentum is given by

$$p = \sqrt{2m_{\rm e}E_{\rm kin}} \tag{3.6}$$

with the electron mass  $m_{\rm e}$  and the kinetic energy  $E_{\rm kin}=eV_{\rm acc}$  (electron charge e, acceleration voltage  $V_{\rm acc}$ ). The wavelength is about 5 pm and does therefore not limit the writing resolution (concerning device size from 20 nm to 100 nm).[90,93] The rather dominant limitation effects are forward scattering within the resist, widening the beam and backscattering caused by the substrate.[94] The backscattered electrons expand the effective beam width, which can cause increased total exposure dose and ultimately damage the desired patterning. This is resolved by using the proximity correction, i.e. the beam base dose is modulated by a mapped correction factor.[94] Exemplary mapping of the correction factor for used nanostructures is presented in Figure A.2.

Here, the Vistec EBPG 5000plus is used as e-beam writer system, whose setup is in principle equivalent to a SEM. In the present work, a negative e-beam resist is used. Therefore, the regions, which are exposed to the e-beam (cf. Figure 3.8), will remain after the developing process. After writing, the post exposure bake is performed, which is required for crosslinking of the exposed resist regions. These regions become insoluble in the chemical developer. Next, the resist patterning is transferred to the deposited films by the etching process.

#### 3.2.4 (Reactive) Ion Beam Etching

The Oxford Ionfab 300 plus, a reactive ion beam etching (RIBE) system, is used to transfer resist patterning into the deposited thin films. The sample surface is etched by ion bombardment (physical dry etching), which is shown schematically in Figure 3.7c. The process gas is ionized by a high-frequency generator (13.56 MHz) and the ions are accelerated toward the sample by ion optics.[95] After passing the optics, the ions are neutralized by a perpendicular electron beam, otherwise the sample would be positively charged.

The etching is performed in a high-vacuum chamber to avoid any surface contamination and undesired interactions of the gas ions with other particles. Due to nature of ion beam, the etching process is anisotropic. However, depending on the etching gas composition, chemical (reactive) etching processes also occur, which are rather isotropic. Tilting the sample during etching is beneficial to remove redeposited material on the substrate or at the resist mask. Here, the RIBE process enables sufficient etching rates (range: nanometer per second) to control structuring of films precisely, which are several nanometers thick.

## Chapter 4

### **Device Fabrication**

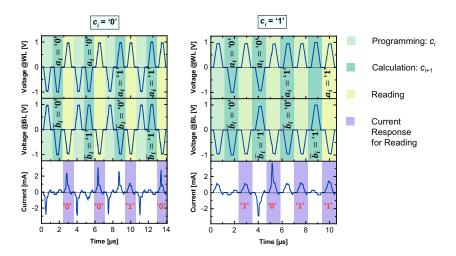

#### 4.1 Thin Film Characterization