# Investigating CMOS Based Local Bias Voltage Generation for Solid-State Qubit Potential Well Creation

Patrick Vliex<sup>1</sup>, Carsten Degenhardt<sup>1</sup>, Lotte Geck<sup>1</sup>, Andre Kruth<sup>1</sup>, Dennis Nielinger<sup>1</sup>, Stefan van Waasen<sup>1,2</sup>, Stefan Heinen<sup>3</sup> <sup>1</sup>Central Institute of Engineering, Electronics and Analytics, ZEA-2 Electronic Systems, Forschungszentrum Jülich GmbH,

<sup>2</sup>Communication Systems Department (NTS), University of Duisburg-Essen <sup>3</sup>Chair of Integrated Analog Circuits and RF Systems, RWTH Aachen University

#### Quantum Computer needs millions of physical Qubits<sup>[1,2]</sup>

- Qubits operated inside a dilution refrigerator

- Number of Qubits need to increase by several orders of magnitude to build a universal quantum processor

- Need for a completely scalable solution

- Technology operable at cryogenic temperatures, 4 K down to 20 mK

- → Integrated semiconductor based devices are promising candidates in order to meet these criteria, i.e. modern CMOS process technology

#### Integrate Local Classical Control **Electronics with Qubits**

- Long-term scalability calls for local classical control electronics:

- Reduce number of wires fed into the fridge

- Reduce bandwidth by pre-processing data

- (Partly) local quantum error correction possible

- Electronics should include: bias voltage DACs, control pulses generation, readout, data pre-processing

- Top-down system design and bottom-up implementation:

- → Investigate system partitioning (RT, 4 K and Qubit stage)

- → Design specialized ICs for cryogenic temperature

## State of the Art

#### "Brute Force" Scaling

- Increase the no. of wires to connect as many Qubits as possible

- 7 x 7 qubits are targeted to be operated<sup>[3]</sup>

- No full scalability to millions of Qubits

#### 4 K Stage Control Electronics<sup>[4]</sup>

- Ongoing research activity in order to bring control electronic into the dilution refrigerator, including use of FPGAs, ASICs and off-the-shelf components

- Only limited number of devices operated at the lowest temperature stage (e.g. MUX and DEMUX)

- Considerably more cooling power available on 4 K stage, but interconnect to Qubits via cables required

- Multiplexing used to reduce the required number of

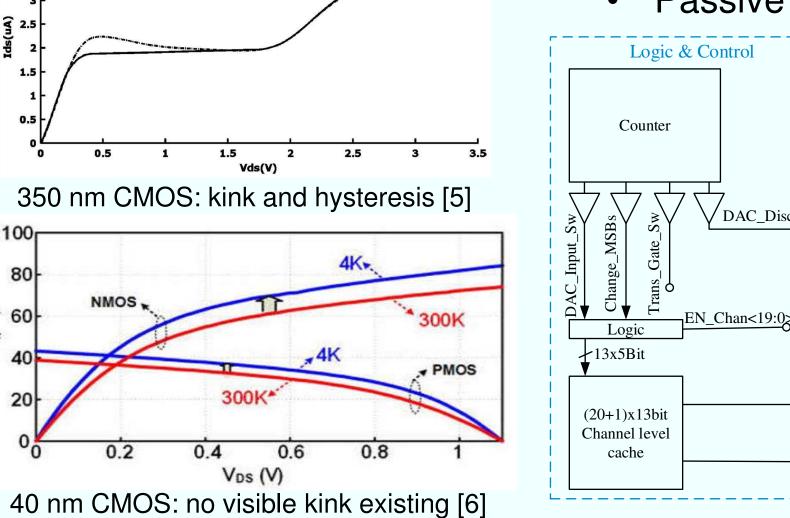

#### **CMOS Cryogenic Operation**

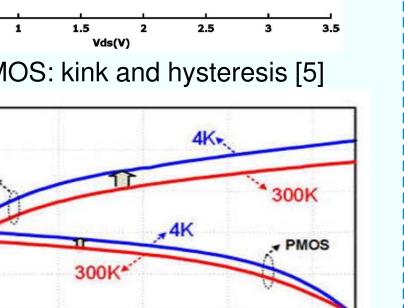

- Ultra low temperatures lead to MOSFET behavior anomalies e.g.:<sup>[5]</sup>

- Kink effect

- Dopant freeze-out (<30 K)</li>

- V<sub>TH</sub>-shift

- I<sub>D</sub>-Hysteresis

- Rapid increase of noise below 50 K, due to cryogenic anomalies (in 350 nm CMOS)<sup>[5]</sup>

- Reduced kink for CMOS process nodes < 100 nm<sup>[6]</sup> → Use small technology nodes

- No standard model for cryogenic MOSFET behavior is commercially available<sup>[6]</sup>

- Modeling and fitting of CMOS parameters is required

### System Level Considerations

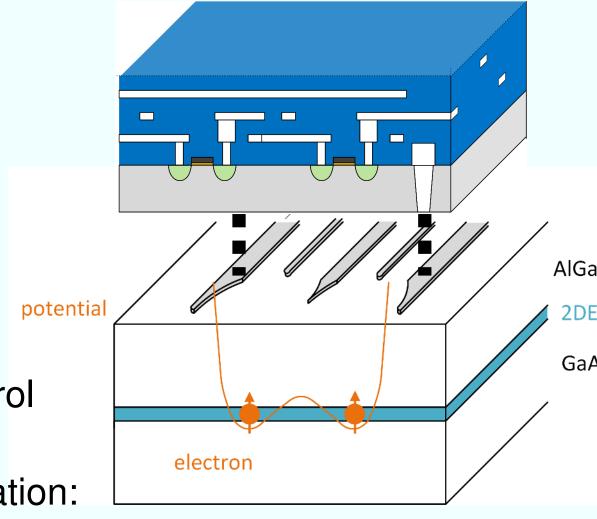

#### IC for Bias Voltage Generation

- Generate bias voltages for Quantum Dot (potential well for electrons)

- Update times in the range of milliseconds

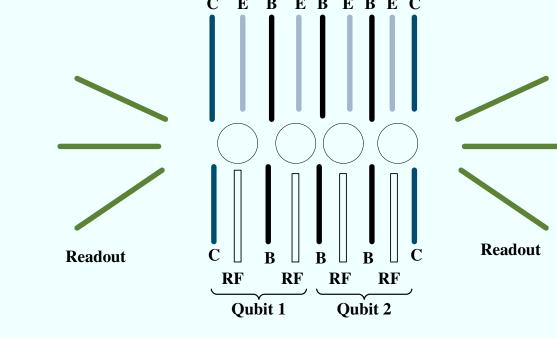

- 5-10 DC voltages needed for one Qubit

- Bias tee used for RF electrodes

- Voltage digital-to-analog converter (DAC)

Qubit

#### **Design Challenges**

- Cryogenic operating conditions

- Ultra-low power consumption: ca. 1 mW total cooling budget at lowest cooling stage

- Extremely stable output voltages: uncertainties of less than 30 μV

- Scalable architecture (e.g. multiplexing)

- Quantitative design specifications still pre-

- Include various options to tune circuit

- → Novel IC circuit architectures and approaches enabling solutions not applicable without CMOS technologies

### **Cryogenic IC Qubit Control Demonstrator**

- Design of a proof of principle demonstrator in commercial CMOS 65 nm technology

- Operation on the same interposer as the Qubits

- Lowest temperature regime of dilution refrigerator (<100 mK)

- First step: DC biasing DACs for potential well creation

- Test structures support fitting of device model parameters to cryogenic environment

- Prove feasibility of using commercial CMOS to control a Qubit and develop system concepts for full scalability

### Implementation

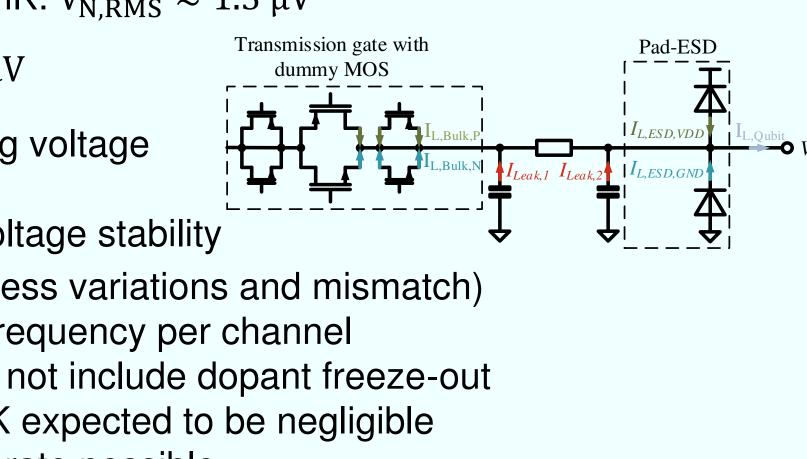

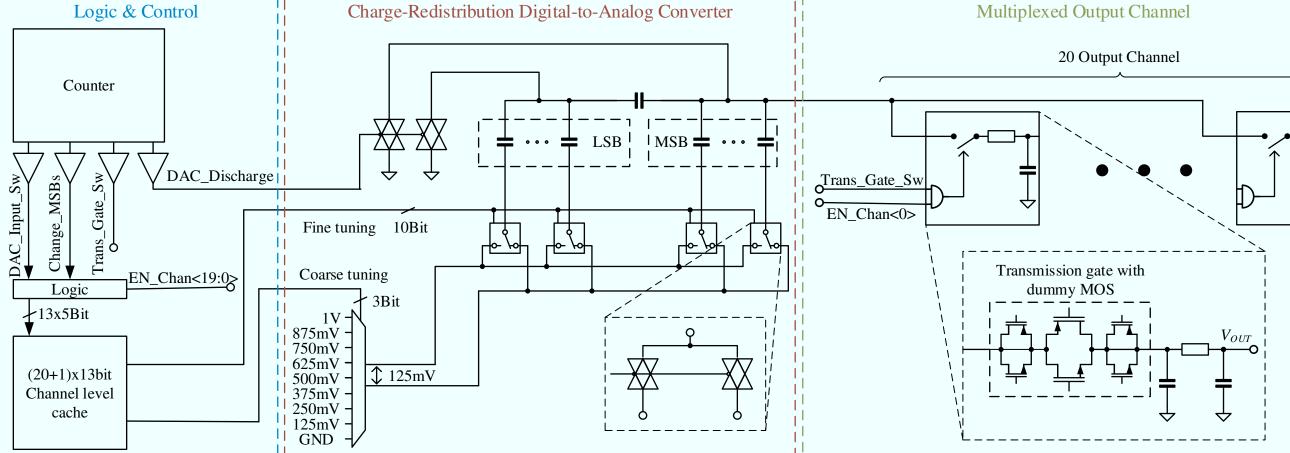

#### **Charge-Redistribution DAC Topology**

- Utilize reduced thermal noise at cryogenic temperatures:  $\overline{V}_{N,RMS} = \sqrt{\frac{k_B \cdot T}{C}}$  [8] Conclusion and Outlook

- Iterative charging concept implemented

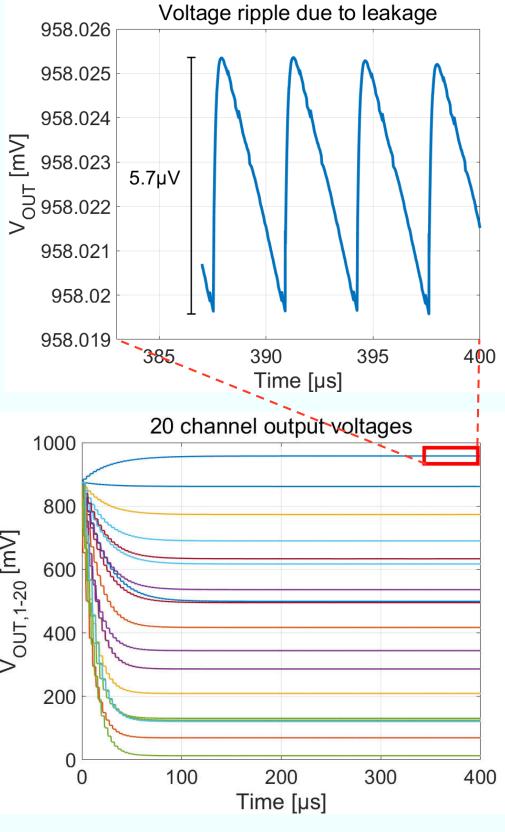

- Periodical refresh needed to compensate leakage currents

- Reduce power consumption by coarse tuning reference voltages

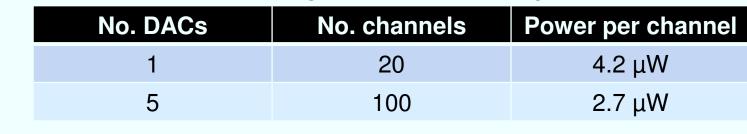

- Multiplexing of output channels to further enhance power and area efficiency

- Passive low-pass filtering of output signals

#### **Voltage Stability**

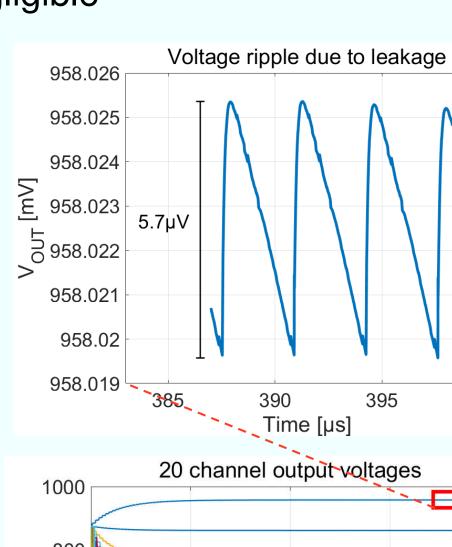

Simulated static operating point noise in one output channel and extrapolated data

$$\overline{V}_{RMS} \propto \sqrt{\mathbf{T}/\mathbf{I}_{\mathbf{D}} + \mathbf{T} \cdot \mathbf{I}_{\mathbf{D}} + \mathbf{T}^2 \cdot \mathbf{I}_{\mathbf{D}}^2}$$

[9]

Noise source: **Thermal** Channel

- Small I<sub>D</sub> due to low current flow for refreshing (range of 5-10 nA)

- Thermal noise is main contributor

- Simulated noise at 100 mK:  $\overline{V}_{N,RMS} \approx 1.3 \,\mu V$

close to

$$\sqrt{\frac{k_B \cdot 0.1K}{1 \text{ pF}}} = 1.17 \text{ }\mu\text{V}$$

- Leakage currents causing voltage drop on the capacitors

- Tradeoff: power vs. voltage stability

- Max. 10 μV (with process variations and mismatch)

- → ~300 kHz refresh frequency per channel

- Simulation models do not include dopant freeze-out

- → Leakage at 100 mK expected to be negligible

- → Decreased refresh rate possible

#### **Power Consumption**

- System speed defined by transmission gate "on"-time (4 ns → 125 MHz clock rate)

- Major part of power dissipated in digital logic and buffers for transmission gate control

- $P_{Dig} \propto V_{DD}^2$

- → Reduce supply voltage

- → Dedicated cryogenic CMOS technology operating at few mV supply

- Reuse control signals for multiple DACs

→ DAC architecture and global signals promise further reduction of power consumption

- Promising early noise simulations indicate the potential of cryogenic ICs

- Promising early power simulations encourage the feasibility to operate multiple Qubits within given power budget

- Investigate the influence of parasitics on the supplied voltages

- Need for ultra-low noise supply and reference voltages

- Decide on interface protocol (robustness, efficiency)

- Integration of ADC for DAC output verification on demonstrator

operating between 4.2 K and 300 K," Review of Scientific Instruments, vol. 83, no. 2, p. 024708

[9] BSIM4.5.0 MOSFET Model, online: http://bsim.berkeley.edu/models/bsim4/, 14.08.2017

[1] D. Wecker, B. Bauer, B. K. Clark, M. B. Hastings, and M. Troyer, Physical Review A 90, 022305 (2014). [2] R. Van Meter and C. Horsman, "A Blueprint for Building a Quantum Computer," in Communications of the ACM, vol. 56, no. 10, pp. 84-93, October 2013.

[3] Courtland, R. & Lucero, E., Google Plans to Demonstrate the Supremacy of Quantum Computing, 2017

[4]F. Sebastiano et al., "Cryogenic CMOS interfaces for quantum devices," 2017 7th IEEE International Workshop on Advances in Sensors and Interfaces (IWASI), Vieste, 2017, pp. 59-62. [5] B. Okcan, G. Gielen and C. Van Hoof, "A third-order complementary metal-oxide-semiconductor sigma-delta modulator

[6] E. Charbon et al., "15.5 Cryo-CMOS circuits and systems for scalable quantum computing," 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2017, pp. 264-265.

[7] Tim Botzem, "Coherence and high fidelity control oftwo-electron spin qubits in GaAs quantum dots," PhD Thesis, p. 36, Figure 4.2.: Schematic setup. Online: http://publications.rwth-aachen.de/record/689507, 14.08.2017 [8] Behzad Razavi, "Design of analog CMOS integrated circuits", Second Edition, Mc Graw Hill Education, 2017, p. 229

350 nm CMOS: kink and hysteresis [5]

T sensor References

T = 20 mK