Received 27 April 2018; revised 8 June 2018; accepted 3 August 2018. Date of publication 9 August 2018; date of current version 31 August 2018.

The review of this paper was arranged by Editor K. E. Moselund.

Digital Object Identifier 10.1109/JEDS.2018.2864581

# A Novel Gate-Normal Tunneling Field-Effect Transistor With Dual-Metal Gate

STEFAN GLASS<sup>®</sup> <sup>1</sup>, KIMIHIKO KATO<sup>®</sup> <sup>2</sup>, LIDIA KIBKALO<sup>1</sup>, JEAN-MICHEL HARTMANN<sup>3,4</sup>, SHINICHI TAKAGI<sup>2</sup> (Member, IEEE), DAN BUCA<sup>1</sup> (Member, IEEE), SIEGFRIED MANTL<sup>1</sup>, AND ZHAO QING-TAI<sup>®</sup> <sup>1</sup> (Member, IEEE)

1 Peter Grünberg Institut, JARA-FIT, Forschungszentrum Jülich, 52425 Jülich, Germany

2 Department of Electrical Engineering and Information Systems, University of Tokyo, Tokyo 113-8656, Japan

3 University of Grenoble Alpes, F-38000 Grenoble, France

4 CEA, LETI, MINATEC Campus, F-38054 Grenoble, France

CORRESPONDING AUTHOR: Z. Qing-Tai (e-mail: q.zhao@fz-juelich.de)

This work was supported in part by the German Federal Ministry of Education and Research through the Project "UltraLowPower" under Grant 16ES0060K, and in part by E2SWITCH from the European Community's Seventh Framework Program under Grant 619509.

**ABSTRACT** In this combined experiment and simulation study we investigate a SiGe/Si based gate-normal tunneling field-effect transistor (TFET) with a pillar shaped contact to the tunneling junction which brings forth two significant advantages. The first, is improved electrostatics at the boundary of the tunneling junction which helps to diminish the influence of adverse tunneling paths, and thus, substantially sharpens the device turn on. The second, is a simplified fabrication of a dual-metal gate using a self-aligned process. We demonstrate the feasibility of the process and show the positive effect of a dual-metal gate in experiment. Overall the paper provides general guidelines for the improvement of the subthreshold swing in gate-normal TFETs which are not restrained to the material system.

**INDEX TERMS** Tunnel FET, dual-metal gate, gate-normal tunneling, work function tuning, field-induced quantum confinement.

### I. INTRODUCTION

The study of tunneling field-effect transistors (TFETs) has been driven by the need for steep slope devices with the capability to be integrated in ultra-low power circuits [1]. The underlying idea is to reduce power consumption by supply voltage  $(V_{dd})$  scaling (<0.3V). This can be achieved by using transistors with a subthreshold swing (SS) lower than 60 mV/dec that is the physical limit of MOSFETs, stemming from their operation principle based on thermal emission over a potential barrier. Physically, the operation of TFETs, based on band-to-band tunneling is fundamentally different from MOSFETs and not restrained to 60 mV/dec at 300K. Ideally a density of states (DOS) switch is realized, which refers to the condition that the current flow sets in abruptly, as soon as an energetic alignment of source valence band and channel conduction band (or vice versa) is achieved by applying a gate voltage. In an ideal semiconductor with sharp band edges and without non-idealities the increase of DOS around the band edge can reach many orders of magnitude within a few meV. Thus, theoretically the massive

increase in available and empty states contributing to the tunneling current, when aligning the band edges, should make an increase of current by one order of magnitude possible with much less than 60 mV. However, experimentally it has been difficult to achieve according results. Therefore, a lot of research is focused on identifying the limiting issues. One major obstacle are traps. According to [2] the avoidance of bulk traps is crucial, even though there may exist device geometries which are more trap tolerant than others [3]. Moreover, the device geometry determines the abruptness of the turn-on even principally. Agarwal and Yablonovitch [4] have theoretically analyzed possible dimensional combinations at the tunneling junction, e.g., 1D/1D, 2D/2D or 2D/3D making use of abrupt changes in DOS. Gate-normal or line tunneling FETs ideally show a very sharp turn-on and on-currents scalable with the overlap area [5]-[9]. But there is always a competition between gate-normal tunneling and parasitic tunneling at edges [10], [11]. Counter doping inside the channel was proposed and has been proven to be beneficial in terms of SS and I<sub>on</sub> in experiment [12]. On the

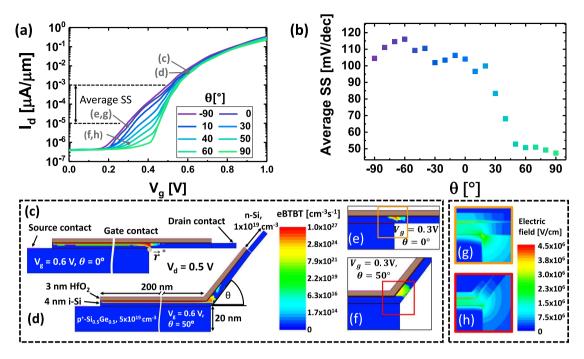

FIGURE 1. (a) Simulated  $I_d - V_g$ -characteristics for different contact arm angles  $\theta$  as defined in (d). By bending the contact arm upwards the unwanted tunneling generation at the right boundary of the SiGe-Source decreases, right-shifting the onset and thus uncovering the sharp turn-on stemming from gate-normal tunneling. Curves between  $-90^\circ$  and  $0^\circ$  do not vary from each other significantly and are thus not displayed. (b) The average SS between  $10^{-5} \, \mu A/\mu m$  and  $10^{-3} \, \mu A/\mu m$  greatly improves with increasing  $\theta$ , especially between  $20^\circ$  and  $50^\circ$ . (c,d) eBTBT contour plots for a simulated structure with  $\theta = 0^\circ$  and  $\theta = 50^\circ$  at  $V_g = 0.6$  V,  $V_d = 0.5$  V evincing that gate-normal tunneling dominates the on-state in the complete overlap region independent of  $\theta$ . (e,f) Adverse eBTBT generation at the right SiGe boundary in the early subthreshold region ( $V_g = 0.6$  V,  $V_d = 0.5$  V). (g,h) Electric field corresponding to the eBTBT plots in (e,f) illustrating that the reduced electric field at the corner for increasing  $\theta$  is the reason for smaller parasitic eBTBT generation. (Quantization neglected).

other hand counter doping needs restrictions in order to avoid band-tails [13]–[15]. Another approach is the use of a dual-metal gate, which has been analyzed theoretically in many publications [16]–[20]. Though experimental feasibility is often considered [18], [21] for a possible fabrication of dual-metal TFETs, process requirements, like lithographic alignment precision of the gate to a few nm, are often very harsh. In this paper we elucidate a revised architecture for a gate-normal TFET employing a self-aligned fabrication process to create a dual-metal gate.

### II. PRELIMINARY CONSIDERATIONS

We begin our considerations with a recapitulation of the basic gate-normal TFET architecture as described in [11], [22] shown in Fig. 1 (c) [dimensions and doping in Fig. 1(d)]. The source region which consists of boron-doped  $p^+$ -SiGe (in this example) is electrically contacted on the left. It is overlapped by a 4 nm thin i-Si channel and a high-k/metal gate, forming a vertical gate-normal tunneling junction in the overlap region. The channel and the gate extend over the right boundary of the SiGe region towards the  $n^+$ -Si drain. We will refer to this extension as the contact arm hereafter. It is commonly assumed that a buried oxide is placed below the horizontally extending contact arm [23]. For our first consideration we neglect the experimental feasibility and introduce the parameter  $\theta$  which describes the angle between the contact arm and the horizontal. Using Sentaurus

technology computer aided design (TCAD) we have analyzed the impact of  $\theta$  on the electric field and parasitic tunneling at the position, where the contact arm and the right SiGe boundary meet. The behavior at this point has been shown to be very critical for the device performance [10], [11]. We employed the dynamic non-local path BTBT model from the TCAD Sentaurus environment [24]. The BTBT model constants were obtained from strained Si/SiGe band diagrams with adjusted effective density of states and effective masses calculated with a 30-level k.p-model [25]. Quantization is neglected for now, to underline that the effect is of electrostatic origin, but will be taken into account at a later stage [see Fig. 4(b)]. Fig. 1 (a) displays the simulated  $I_d - V_{\varrho}$ characteristics for  $-90^{\circ} < \theta < 90^{\circ}$ . Between  $-90^{\circ}$  (equivalent to the contact arm being bent vertically downwards) and 0° [Fig. 1(c)] the curves agree with each other quite decently. Between  $0^{\circ}$  and  $50^{\circ}$  the onset shifts to the right and significantly sharpens the turn-on. Above 70° no further changes are obvious. The drain-current  $I_d$  is independent of  $\theta$  for  $V_g > 0.6 V$  and likewise is the on-current  $I_{on}$ . This independence from  $\theta$  illustrates that  $I_{on}$  derives its value from the properties of the gate-normal tunneling junction and not from the geometry at the contacting point of the extension arm. This is further emphasized by the contour plot in Fig. 1(c,d), which clearly displays strong eBTBT generation along the complete overlap length below the gate at  $V_g = 0.6 V$ . Contrary to that, the early subthreshold region

VOLUME 6, 2018 1071

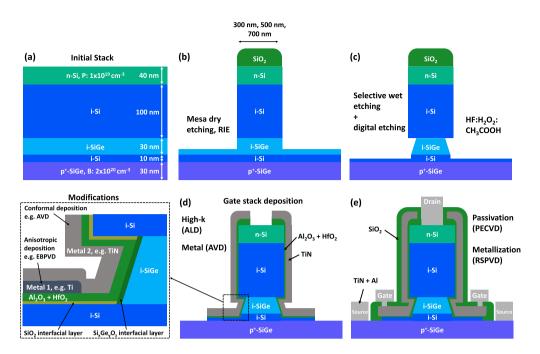

FIGURE 2. (a-e) Fabrication steps of a vertical gate-normal TFET (L-shape with rotational symmetry). (a) Initial stack composed of SiGe and Si layers as grown by CVD, where the two bottom layers form the tunneling junction. (b) Deposition (by PECVD) and patterning of a SiO<sub>2</sub> hard mask, followed by EBL and RIE used to form pillars with 300 nm, 500 nm and 700 nm diameter. The i-SiGe layers serves as an etch-stop. (c) i-SiGe is removed with selective wet chemistry, resulting in an undercut and exposing a smooth Si surface. Then, the channel thickness is reduced with digital etching. On top of the Si channel the gate stack is deposited subsequently, as shown in (d) and its inset. After Al<sub>2</sub>O<sub>3</sub>+ HfO<sub>2</sub> deposition with ALD, in an optional step metal 1 (Ti) can be deposited anistropically with EBPVD covering horizontal planes only (inset). Independent of the deposition of metal 1, AVD is (subsequently or exclusively) used to uniformly cover all surfaces with metal 2. EBL and RIE are used to define the gate area. In the gate surrounding area the i-Si layer is removed with TMAH subsequently. (e) SiO<sub>2</sub> is used as a passivation layer, contact openings are patterned into it with EBL and RIE. TiN + Al metal contacts are applied in a lift-off process.

is heavily influenced by parasitic tunneling into the contact arm as shown in Fig. 1(e,f). However, the upward-bending of the contact arm leads to significantly improved average SS between  $10^{-5}$   $\mu$ A/ $\mu$ m and  $10^{-3}$   $\mu$ A/ $\mu$ m reaching well below 60 mV/dec as evidenced in Fig. 1(b) for  $\theta > 60^{\circ}$ . To understand this, consider the electric field created by the gate at the point  $\vec{r}^*$  [Fig. 1(c)], which is depicted in Fig. 1(g,h). When  $\theta$  is increased, which is equivalent to the contact arm being bent upwards, the magnitude of the electric field at the point  $\vec{r}^*$  decreases and with it the parasitic eBTBT generation rate. Therefore, for  $\theta > 60^{\circ}$  the gate-normal and the parasitic tunneling paths set in at a similar gate voltage and SS is significantly improved.

# III. FABRICATION

From a fabrication point of view simply changing the angle  $\theta$  is not possible, but an analogous structure can be defined, as depicted in Fig. 2. The contact arm is replaced by a pillar located in the middle of a circular-symmetric source-channel-gate overlap region (see also Fig. 3). The actual devices were created according to the process steps listed in Fig. 2. The initial stack, grown by chemical vapor deposition (CVD), consists of a highly doped p<sup>+</sup>-SiGe source (Boron doped, 30 nm, p =  $2 \times 10^{20}$  cm<sup>-3</sup>), on top of which the tunneling layer is positioned which is composed of i-Si (10 nm). The mesa is defined with e-beam lithography (EBL) and reactive

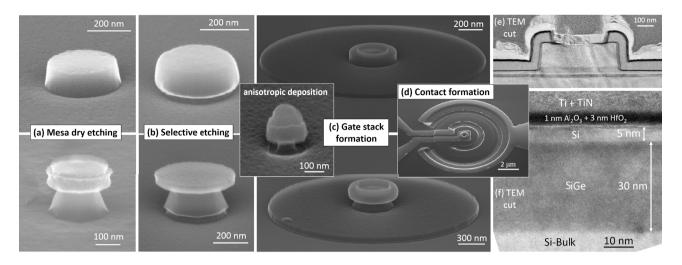

ion etching (RIE). Etching is stopped in the i-SiGe-layer [Fig. 2(b), Fig. 3(a)], which is subsequently removed with selective wet chemistry (HF:H<sub>2</sub>O<sub>2</sub>:CH<sub>3</sub>COOH, 1:2:3), resulting in a smooth Si surface [Fig. 2(c), Fig. 3(b)]. A smooth interface to the gate [see TEM micrograph in Fig. 3(e)] is crucial, because considerable roughness deteriorates the turn on by smearing out the sharp discrete 2D DOS leading to inferior SS similar to band-tails [22]. Due to the high selectivity of the etching solution an undercut of the i-SiGe layer below the i-Si in the pillar is realized. Next, the Si channel thickness was reduced by a digital etching process, comprising a dry plasma oxidation step and oxide etching in HF to achieve a target thickness of 5 nm or less, by removing 1-2 nm every cycle [see Fig. 3(e)]. Thicker layers are not feasible since the electrostatic control at the tunneling junction, which decreases exponentially with layer thickness, will be insufficient. The high-k layer (Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>) is conformally deposited by atomic layer deposition. Now one of two options was chosen. In the first option, the gate metal deposition (TiN) is carried out by atomic vapor deposition (AVD) [Fig. 2(d)] only, covering all surfaces conformally. By contrast, in the second version of the process an anisotropic metal deposition process (Ti) is inserted before AVD to create two distinctly separated regions with metals exhibiting different work functions [inset of Fig. 2(d)]. In this nonconformal deposition step, e.g., using electron beam physical

1072 VOLUME 6, 2018

FIGURE 3. (a-c) SEM images taken at different stages of the fabrication process, as indicated in the images. The lower panels show the same fabrication process steps with a tapered side wall profile below a TiN-disk on top of the pillar. The inset in (c) shows a test structure where the shadowing effect during anisotropic deposition is illustrated with a thicker metal layer than used on actual devices to enhance visibility. (d) SEM view after metal contacting. (e-f) TEM cross section of processed devices showing an overview (e) and a close-up of the tunneling junction (f).

vapor deposition, Ti covers all but the sidewalls of the pillar and especially not the undercut region. Secondly, the conformal atomic vapor deposition (AVD) process was used to cover the sidewalls and the undercut region with TiN. Next, EBL and RIE are used to etch the gate metal, thereby defining the dimensions of the gate and opening a contact window in the center of the pillar [Fig. 2(d), Fig. 3(c)]. Then, the exposed gate oxide after TiN-etching and the Si channel on the plane are removed by HF and TMAH etching respectively. At last a 100 nm SiO<sub>2</sub> passivation was deposited with plasma enhanced chemical vapor deposition (PECVD), contact openings into the passivation are created with EBL and RIE, and finally TiN+Al contacts were formed in a lift-off process [Fig. 2(e), Fig. 3(d)].

# IV. CHARACTERIZATION

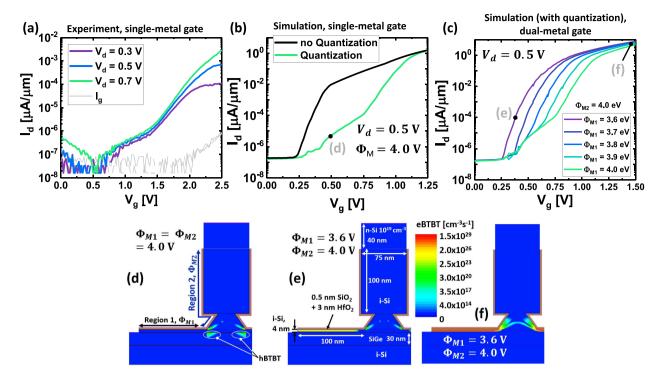

Fig. 4(a) shows the transfer characteristics of a device with single gate metal as often observed in experiment. The turnon starts at  $V_g = 0.5 V$ , from where  $I_d$  increases slowly until about  $V_g = 1.35$  V. After that, a steeper slope is observed until the current starts to saturate eventually. According to the conclusion from Fig. 1 we can exclude a purely electrostatic origin for the bipartite increase of  $I_d$ . Indeed, simulations without quantization [Fig. 4(b)] on the specific structure qualitatively reproduce the  $I_d - V_g$  characteristics in Fig. 1(a) for  $\theta > 70^{\circ}$ . However, when corrections due to (field-induced) quantum confinement are taken into account, using the density gradient quantization model incorporated in Sentaurus TCAD [24], the traits from experiment can be reproduced [Fig. 4(b)]. The consequences are illustrated in Fig. 4 (b). The green trace exhibits a similar shape as the experimental curve [Fig. 4(a)], comprising a slow initial turn-on followed by a steeper region. The eBTBT generation evaluated in this region (at  $V_g = 0.5 \ V$ ) shown in Fig. 4(d) confirms that the problem is caused by tunneling into the pillar, before gate-normal tunneling has commenced. This is a consequence of a non-uniform quantization condition. The 2DEG in region 1 is confined to a triangular potential well induced by the gate, whose width is given by the channel thickness (4 nm in the simulation). At the bottom edge of the pillar the distance from the gate to the source increases and thus the potential-well width. Hence, the correction of the potential due to quantization in the narrower well in region 1 is larger than in region 2 at the bottom of the pillar, where eBTBT generation can be seen in Fig. 4(d). This is in part related to the width of the pillar being large compared to the thin Si channel, so that the physics in the middle of the pillar are almost bulk-like. The stronger quantization in region 1 leads to a delay of the alignment of states from the conduction and valence band [26]. Additionally, the hole BTBT generation [Fig. 4(d)] stems exclusively from SiGe underneath the pillar, owing to the weaker gate-control in this region compared to SiGe underneath the gate.

While the shape of the curves is well reproduced by simulations the magnitude of the current is different, because smaller, but realistic EOT was used for simulations (0.5 nm  $SiO_2$  interfacial layer + 3 nm  $HfO_2$ ) in addition to a reduced channel thickness (4 nm) to exemplify the feasible performance of such TFETs. Yet, we point out that the employed, basic quantization model may overestimate the current and refer to more elaborate treatments of quantization such as [27], noting that therein gate-normal tunneling shows a similar delay to parasitic edge tunneling as observed here. Fig. 4(c) also contains a solution to the problem, which is a dual-metal gate as proposed before e.g., in [16] and [18]. Like we described in the fabrication section a metal with lower work-function can be deposited self-aligned on the plane with an anisotropic deposition [compare inset of Fig. 3(c)]. Therefore, the metal gate in simulations was split accordingly. The work function  $\Phi_{M1}$  is applied to

VOLUME 6, 2018 1073

FIGURE 4. (a) Experimental transfer characteristics, exhibiting a considerably delayed onset of gate-normal tunneling. (b) Comparison of simulated transfer characteristics, evincing that the shape of the experimental transfer characteristics are only reproduced when including quantization corrections. (c) Simulated transfer characteristics employing quantization and two different metal work-functions, on the plane  $(\Phi_{M1})$  and in the undercut and sidewall regions  $(\Phi_{M2})$ . Due to quantum confinement the onset of gate-normal tunneling is delayed substantially  $(\Phi_{M1} = \Phi_{M2} = 4.0 \text{ eV})$ , resulting in degraded SS. As can be seen in the contour plot (d), the cause of the degraded SS is eBTBT generation inside the pillar at the point specified in (b). Improved SS can be restored by reducing the gate work function  $\Phi_{M1}$  to 3.6 eV, leading to a simultaneous onset of eBTBT inside the pillar and in the source-gate-channel overlap region (e). (f) The on-state is dominated by gate-normal tunneling. The structure in (d-f) is symmetric to a vertical axis through the middle of the pillar but cut off for better visibility.

region 1, extending over the plane as indicated in Fig. 4(d) and stopping right at the corner of the pillar. Region 2 with  $\Phi_{M2}$  covers the undercut region and the sidewalls of the pillar up to the n-type drain region. When  $\Phi_{M1}$  is reduced, so is the onset of gate-normal tunneling, as seen in Fig. 4(c,e) for  $\Phi_{M1} = 3.6 \text{ V}$  and  $\Phi_{M2} = 4.0 \text{ V}$ . By this measure, a non-interrupted sharp turn-on with small SS is recovered. Note, that for the on-state the work-function difference does not play a major role [Fig. 4(c,f)].

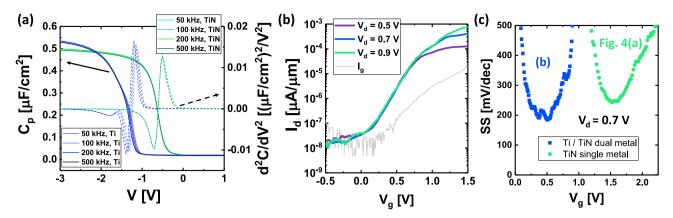

In experiment the choice for the two metals fell on Ti and TiN. By this we can estimate the range of possible workfunction combinations for different nitrogen incorporation between stoichiometric TiN and Ti. TiN is a well-established material in the semiconductor industry and it is known that the work-function of TiN can be tuned by the amount of incorporated nitrogen [28]. Hence by varying the nitrogen content a whole range of work-functions should become accessible for fine tuning. Other viable options are the additional incorporation of aluminum [29] to manipulate the work-function of TiN. Fig. 5(a) presents capacitancevoltage (CV) characteristics of MOSCAPs with Ti and TiN as gate metal on SiO<sub>2</sub>. Clearly, the curves are shifted with respect to each other. Using the inflection point method [30] we determined the flat-band voltage to calculate the difference in metal work-function  $\Delta \Phi_M$  between the two MOSCAPs. The obtained value of 0.65 V (in good agreement with [28]) is larger than the 0.4-eV-difference that is needed according to Fig. 4(b) to completely avoid any influence from parasitic edge tunneling on the transfer characteristics. Yet,  $\Delta\Phi_M = 0.4$  eV is absolutely contained in the range that is experimentally feasible when tuning the nitrogen content.

The effect of the Ti/TiN dual-metal gate is exemplified in Fig. 5(b,c). The  $I_d - V_g$ -characteristics show that the turn-on was effectively left-shifted and no region of slowly increasing current in the early subthreshold region is obvious. To reinforce this assessment, we have plotted SS vs.  $V_g$  obtained from Fig. 5(b) (blue curve) and Fig. 4(a) (green curve) in Fig. 5(c). It is evident that by reducing the onset of gate-normal tunneling with the help of a second metal with lower work-function a smaller SS is achieved. However, the absolute values of SS and  $I_{on}$  remain yet to be improved in further research, e.g., by reducing the equivalent oxide thickness, avoiding trap-assisted tunneling, exploiting other material combinations with lower (pure Ge source) or direct bandgap and other measures that have been discussed elsewhere [2]-[4], [13], [31]. It is worth noting that the experimental  $\Delta \Phi_M$  may be too large. In the worst case, BTBT uniformly occurs in region 1, whereas region 2 is still highly resistive. Thus, the switching characteristics would be dominated by the resistance in this region and not by the tunneling junction. Though, as pointed out before the issue can be resolved by adjusting  $\Phi_{M1}$  by controlling the

1074 VOLUME 6, 2018

FIGURE 5. (a) CV characteristics (solid lines, left y-axis) of a MOSCAP with Ti and TiN as gate metal on 8 nm thermal SiO<sub>2</sub>/Si-Bulk. The flat band voltage for both metals is determined via the inflection point method [30], where the zero-crossing of the second derivative of the capacitance (dashed line, right y-axis) corresponds to  $V_{FB}$ .  $V_{FB}^{TI} \approx -1.26 \ V$  and  $V_{FB}^{TIN} \approx -0.61 \ V$ , corresponding to a  $V_{FB}$ -Difference and thus a work function difference of about 0.65 V. (b)  $I_d - V_g$ -characteristics of a device with Ti / TiN dual metal gate. (c) Due to the lower work-function of Ti, gate-normal tunneling sets in earlier in the dual-metal TFET (for otherwise identical parameters) and thus a better SS is achieved.

nitrogen content. Anyhow, the general inferences that were made on TFET shape and the use of a dual-metal gate are neither mitigated by the performance nor restrained to the SiGe/Si material system. Therefore, they should be transferable to other material combinations like SiGeSn/GeSn or other material systems like III-V semiconductors.

# V. CONCLUSION

We have presented a physical analysis for a gate-normal TFET with a pillar-shaped contact to the tunneling junction and elucidated its advantages regarding a viable and self-aligned fabrication process. In addition, the pillar shape is beneficial in terms of electrostatics to reduce the negative influence of parasitic tunneling paths. Because quantum confinement delays the onset of gate-normal tunneling, we have shown that the utilization of a Ti/TiN dual-metal gate becomes necessary to restore an unobstructed turn-on. Our findings obtained on SiGe/Si TFETs are not limited to the specific material combination and thus provide directives for future research with lower bandgap materials such as GeSn/SiGeSn.

### **REFERENCES**

- A. C. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proc. IEEE*, vol. 98, no. 12, pp. 2095–2110, Dec. 2010, doi: 10.1109/JPROC.2010.2070470.

- [2] E. Memisevic et al., "Individual defects in InAs/InGaAsSb/GaSb nanowire tunnel field-effect transistors operating below 60 mV/decade," Nano Lett., vol. 17, no. 7, pp. 4373–4380, Jul. 2017, doi: 10.1021/acs.nanolett.7b01455.

- [3] S. Sant and A. Schenk, "Trap-tolerant device geometry for InAs/Si pTFETs," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1363–1366, Oct. 2017, doi: 10.1109/LED.2017.2740262.

- [4] S. Agarwal and E. Yablonovitch, "Pronounced effect of pn-junction dimensionality on tunnel switch threshold shape," EECS Dept., Univ. California at Berkeley, Berkeley, CA, USA, Rep. UCB/EECS-2013-248, 2013.

- [5] A. Bowonder et al., "Low-voltage green transistor using ultra shallow junction and hetero-tunneling," in Proc. Extended Abstracts 8th Int. Workshop Junction Technol. (IWJT), 2008, pp. 93–96, doi: 10.1109/IWJT.2008.4540025.

- [6] P. Patel, K. Jeon, A. Bowonder, and C. Hu, "A low voltage steep turn-off tunnel transistor design," in *Proc. Int. Conf. Simulat. Semicond. Processes Devices*, 2009, pp. 1–4, doi: 10.1109/SISPAD.2009.5290257.

- [7] S. Glass et al., "Experimental examination of tunneling paths in SiGe/Si gate-normal tunneling field-effect transistors," Appl. Phys. Lett., vol. 111, no. 26, Dec. 2017, Art. no. 263504, doi: 10.1063/1.4996109.

- [8] G. Zhou et al., "Vertical InGaAs/InP tunnel FETs with tunneling normal to the gate," *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1516–1518, Nov. 2011, doi: 10.1109/LED.2011.2164232.

- [9] Y. Lu et al., "Performance of AlGaSb/InAs TFETs with gate electric field and tunneling direction aligned," *IEEE Electron Device Lett.*, vol. 33, no. 5, pp. 655–657, May 2012, doi: 10.1109/LED.2012.2186554.

- [10] W. Hsu, J. Mantey, L. F. Register, and S. K. Banerjee, "Strained-Si/strained-Ge type-II staggered heterojunction gate-normal-tunneling field-effect transistor," *Appl. Phys. Lett.*, vol. 103, no. 9, Aug. 2013, Art. no. 93501, doi: 10.1063/1.4819458.

- [11] W. Hsu, J. Mantey, L. F. Register, and S. K. Banerjee, "On the electrostatic control of gate-normal-tunneling field-effect transistors," *IEEE Trans. Electron Devices*, vol. 62, no. 7, pp. 2292–2299, Jul. 2015, doi: 10.1109/TED.2015.2434615.

- [12] S. Blaeser et al., "Novel SiGe/Si line tunneling TFET with high Ion at low Vdd and constant SS," in Proc. IEEE Int. Electron Devices Meeting (IEDM), 2015, pp. 22.3.1–22.3.4, doi: 10.1109/IEDM.2015.7409757.

- [13] S. Sant and A. Schenk, "The effect of density-of-state tails on band-to-band tunneling: Theory and application to tunnel field effect transistors," *J. Appl. Phys.*, vol. 122, no. 13, Oct. 2017, Art. no. 135702, doi: 10.1063/1.4994112.

- [14] S. Agarwal and E. Yablonovitch, "Band-edge steepness obtained from Esaki/backward diode current-voltage characteristics," *IEEE Trans. Electron Devices*, vol. 61, no. 5, pp. 1488–1493, May 2014, doi: 10.1109/TED.2014.2312731.

- [15] S. Agarwal and E. Yablonovitch, "Fundamental conductance÷voltage limit in low voltage tunnel switches," *IEEE Electron Device Lett.*, vol. 35, no. 10, pp. 1061–1062, Oct. 2014, doi: 10.1109/LED.2014.2350434.

- [16] G. B. Beneventi, E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, "Dual-metal-gate InAs tunnel FET with enhanced turn-on steepness and high on-current," *IEEE Trans. Electron Devices*, vol. 61, no. 3, pp. 776–784, Mar. 2014, doi: 10.1109/TED.2014.2298212.

- [17] G. B. Beneventi, E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, "Optimization of a pocketed dual-metal-gate TFET by means of TCAD simulations accounting for quantization-induced bandgap widening," *IEEE Trans. Electron Devices*, vol. 62, no. 1, pp. 44–51, Jan. 2015, doi: 10.1109/TED.2014.2371071.

VOLUME 6, 2018 1075

- [18] C.-Y. Hsu, C.-Y. Chang, E. Y. Chang, and C. Hu, "Suppressing non-uniform tunneling in InAs/GaSb TFET with dual-metal gate," *IEEE J. Electron Devices Soc.*, vol. 4, no. 2, pp. 60–65, Mar. 2016, doi: 10.1109/JEDS.2015.2514060.

- [19] D. Gracia, D. Nirmal, and A. N. Justeena, "Investigation of Ge based double gate dual metal tunnel FET novel architecture using various hetero dielectric materials," *Superlattices Microstruct.*, vol. 109, pp. 154–160, Sep. 2017, doi: 10.1016/J.SPMI.2017.04.045.

- [20] S. Kumar *et al.*, "2-D analytical modeling of the electrical characteristics of dual-material double-gate TFETs with a SiO<sub>2</sub>/HfO<sub>2</sub> stacked gate-oxide structure," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 960–968, Mar. 2017, doi: 10.1109/TED.2017.2656630.

- [21] Y. Zeng et al., "Quantum well InAs/AlSb/GaSb vertical tunnel FET with HSQ mechanical support," *IEEE Trans. Nanotechnol.*, vol. 14, no. 3, pp. 580–584, May 2015, doi: 10.1109/TNANO.2015.2419232.

- [22] S. Sant and A. Schenk, "Modeling the effect of interface roughness on the performance of tunnel FETs," *IEEE Electron Device Lett.*, vol. 38, no. 2, pp. 258–261, Feb. 2017, doi: 10.1109/LED.2016.2636658.

- [23] S. Agarwal, G. Klimeck, and M. Luisier, "Leakage-reduction design concepts for low-power vertical tunneling field-effect transistors," *IEEE Electron Device Lett.*, vol. 31, no. 6, pp. 621–623, Jun. 2010, doi: 10.1109/LED.2010.2046011.

- [24] TCAD Sentaurus Device User Guide Version J-2014.09, Synopsys, Mountain View, CA, USA, 2014.

- [25] D. Rideau et al., "Strained Si, Ge, and Si<sub>1-x</sub> Ge<sub>x</sub> alloys modeled with a first-principles-optimized full-zone k · p method," Phys. Rev. B, Condens. Matter, vol. 74, no. 19, Nov. 2006, Art. no. 195208, doi: 10.1103/PhysRevB.74.195208.

- [26] K.-H. Kao et al., "Direct and indirect band-to-band tunneling in Germanium-based TFETs," IEEE Trans. Electron Devices, vol. 59, no. 2, pp. 292–301, Feb. 2012, doi: 10.1109/TED.2011.2175228.

[27] S. Sant and A. Schenk, "Methods to enhance the perfor-

- [27] S. Sant and A. Schenk, "Methods to enhance the performance of InGaAs/InP heterojunction tunnel FETs," *IEEE Trans. Electron Devices*, vol. 63, no. 5, pp. 2169–2175, May 2016, doi: 10.1109/TED.2015.2489844.

- [28] J. Westlinder, G. Sjöblom, and J. Olsson, "Variable work function in MOS capacitors utilizing nitrogen-controlled TiNx gate electrodes," *Microelectron. Eng.*, vol. 75, no. 4, pp. 389–396, Nov. 2004, doi: 10.1016/J.MEE.2004.07.061.

- [29] L. P. B. Lima et al., "Metal gate work function tuning by Al incorporation in TiN," J. Appl. Phys., vol. 115, no. 7, Feb. 2014, Art. no. 74504, doi: 10.1063/1.4866323.

- [30] R. Winter, J. Ahn, P. C. McIntyre, and M. Eizenberg, "New method for determining flat-band voltage in high mobility semiconductors," J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom., vol. 31, no. 3, May 2013, Art. no. 30604, doi: 10.1116/1.4802478.

- [31] U. E. Avci, D. H. Morris, and I. A. Young, "Tunnel field-effect transistors: Prospects and challenges," *IEEE J. Electron Devices Soc.*, vol. 3, no. 3, pp. 88–95, May 2015, doi: 10.1109/JEDS.2015.2390591.

of Tokyo, Japan.

**STEFAN GLASS** received the B.Sc. and M.Sc. degrees in nanostructure technology from the University of Wuerzburg, Wuerzburg, Germany, in 2012 and 2014, respectively. He is currently pursuing the Ph.D. degree with Forschungszentrum Juelich, Juelich, Germany, with a focus on TFETs.

**LIDIA KIBKALO**, photograph and biography not available at the time of publication.

**JEAN-MICHEL HARTMANN** received the Ph.D. degree in physics from Université Grenoble Alpes, France, in 1997. After a stint as a Post-Doctoral Researcher with Imperial College, London, U.K., he was offered a permanent position with CEA-LETI, Grenoble, in 1999. Since then, he has been exploring the epitaxy of group-IV semiconductors for nanoelectronics and optoelectronics.

**SHINICHI TAKAGI** (M'93) was born in Tokyo, Japan, in 1959. He received the B.S., M.S., and Ph.D. degrees in electronic engineering from the University of Tokyo, Tokyo, Japan, in 1982, 1984, and 1987, respectively. He joined the Toshiba Research and Development Center, Japan, in 1987. From 1993 to 1995, he was a Visiting Scholar with Stanford University. In 2003, he moved to the University of Tokyo, where he is currently a Professor with the Department of Electrical Engineering and Information Systems, School of

Engineering. His recent interests include the science and the technologies of advanced CMOS devices.

**DAN BUCA** (M'14) received the Ph.D. degree from the University of Cologne, Cologne, Germany, in 2002. He is currently a Group Leader "Group IV Optoelectronics and Ion Implantation" with the Peter Gruenberg Institute 9, Forschungszentrum Jülich, Jülich, Germany. His current research interests include the research of group IV material growth, SiGeSn semiconductor heterostructures for photonic applications and electronic devices.

**SIEGFRIED MANTL** is the Head of the Ion Beam Division, Peter Gruenberg Institute 9, a Professor of physics with RWTH Aachen and holds a Honorary Helmholtz Professorship. His research concentrates on silicon related nanoelectronic materials and devices.

**ZHAO QING-TAI** (M'11) received the Ph.D. degree from Peking University, Beijing, China, in 1993, where he started his career as a Lecturer and an Associate Professor. In 1997, he jointed PGI-9, Forschungszentrum Jülich, where he is currently a Senior Research Scientist and the Leader of Nano-Device Research Group. He has published over 260 papers in international journals and conferences with peer review. His research focuses on nanoelectronic devices.

1076 VOLUME 6, 2018