# A C++ BASED MPI-ENABLED TASKING FRAMEWORK TO EFFICIENTLY PARALLELIZE FAST MULTIPOLE METHODS FOR MOLECULAR DYNAMICS

#### **DISSERTATION**

zur Erlangung des akademischen Grades Doktor rerum naturalium (Dr. rer. nat.)

vorgelegt an der Technischen Universität Dresden Fakultät Informatik

eingereicht von

**Dipl.-Math. David Haensel** geboren am 31. März 1988 in Eberswalde-Finow

#### **Gutachter:**

Prof. Dr. Wolfgang E. Nagel, Technische Universität Dresden Prof. Dr. Hans-Joachim Bungartz, Technische Universität München

**Tag der Verteidigung:** 02. Juli 2018

Dresden im August 2018

# **CONTENTS**

| 1 | INTI | RODUCTION 1                                         |

|---|------|-----------------------------------------------------|

|   | 1.1  | Design Guidelines                                   |

|   | 1.2  | HPC and C++                                         |

|   | 1.3  |                                                     |

| 2 | Тне  | <b>FMM</b> IN A NUTSHELL                            |

|   | 2.1  | Particle Grouping                                   |

|   | 2.2  | Multipole and Local Expansions                      |

|   | 2.3  | FMM Operators                                       |

|   |      | 2.3.1 Multipole to Multipole                        |

|   |      | 2.3.2 Local to Local                                |

|   |      | 2.3.3 Multipole to Local                            |

|   | 2.4  | FMM Algorithmic Flow                                |

|   |      | 2.4.1 FMM Setup                                     |

|   |      | 2.4.2 Far-Field Computation                         |

|   |      | 2.4.3 Near-Field Computation                        |

|   | 2.5  | Fmsolvr – Implementation Specifics                  |

| 3 | A C- | ++ Task Engine                                      |

|   | 3.1  | rr rr                                               |

|   |      | 3.1.1 Loop-Level Parallelization                    |

|   |      | 3.1.2 Task-Based Parallelization                    |

|   |      | 3.1.3 Modeling Algorithmic Dependencies             |

|   | 3.2  | Task Engine Design Fundamentals                     |

|   |      | 3.2.1 Anatomy of a Task                             |

|   |      | 3.2.2 Work-Sharing and Work-Stealing                |

|   | 3.3  | Type-Driven Priority Scheduling                     |

|   |      | 3.3.1 Storing Tasks of Different Types              |

|   |      | 3.3.2 Priority Queues                               |

|   |      | 3.3.3 Type-Driven Priority Queue                    |

|   |      | 3.3.4 Anatomy of the Type-Driven Priority Queue     |

|   |      | 3.3.5 Type-Driven Priority Scheduler 53             |

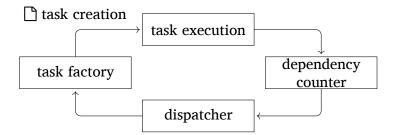

|   | 3.4  | Static Data-Flow Dispatcher                         |

|   |      | 3.4.1 Anatomy of the Static Data-Flow Dispatcher 57 |

|   |      | 3.4.2 Static Data-Flow Dispatcher User Interface 60 |

|   |      | 3.4.3 Dependency Counter 61                         |

|   |      | 3.4.4 Event Handlers                                |

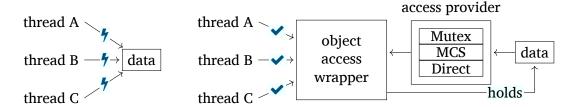

|   | 3.5  | Concurrent Data Access                              |

|   |      | 3.5.1 Encapsulation of Data Accesses 65             |

## **Contents**

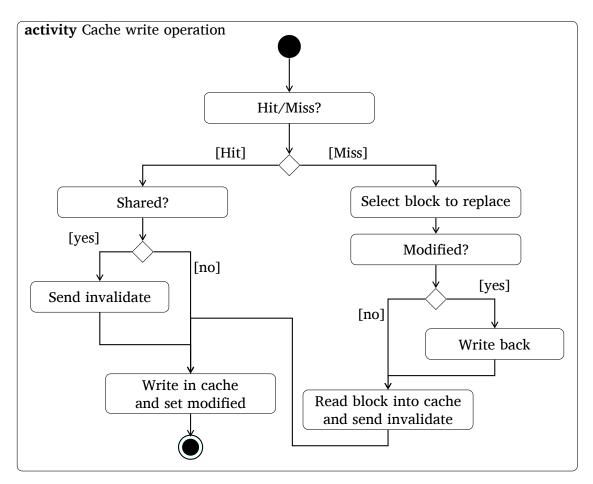

|    |        | 3.5.2     | Cache Coherency                               |

|----|--------|-----------|-----------------------------------------------|

|    |        | 3.5.3     | Locks                                         |

|    |        | 3.5.4     | Supporting NUMA                               |

|    | 3.6    | Use Ca    | ase: FMM Parallelization                      |

|    |        | 3.6.1     | Classical Loop-Based Design                   |

|    |        | 3.6.2     | Evolution of a Data-Centric View              |

|    |        | 3.6.3     | Data-Driven Task Parallel FMM                 |

|    | 3.7    | Perfor    | mance Evaluation                              |

|    |        | 3.7.1     | Overhead-Time Analysis                        |

|    |        | 3.7.2     | Work-Time Analysis                            |

|    |        | 3.7.3     | Idle-Time Analysis                            |

|    |        | 3.7.4     | NUMA-Awareness Analysis 80                    |

|    |        | 3.7.5     | Lock Comparisons                              |

|    |        | 3.7.6     | Real World Benchmarks                         |

| 4  | A C-   | ++ Tasi   | K ENGINE: INTER-NODE EXTENSION                |

| •  | 4.1    |           | essage Passing Interface (MPI)                |

|    | ••-    | 4.1.1     | Basic MPI Communications                      |

|    |        | 4.1.2     | Multithreaded MPI                             |

|    |        | 4.1.3     | Shortcomings of MPI                           |

|    | 4.2    | A C++     | Communication Layer                           |

|    |        | 4.2.1     | MPI Type Traits                               |

|    |        | 4.2.2     | Serialization                                 |

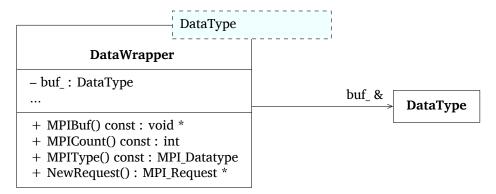

|    |        | 4.2.3     | Encapsulation of Message Data                 |

|    |        | 4.2.4     | Low Level MPI Wrapper                         |

|    |        | 4.2.5     | High Level Communication Interface            |

|    | 4.3    | Task E    | Engine Communication Extension                |

|    |        | 4.3.1     | Collecting Send Data from Different Tasks 105 |

|    |        | 4.3.2     | Dynamically Receiving Messages                |

|    |        | 4.3.3     | Defining Communication Schemes                |

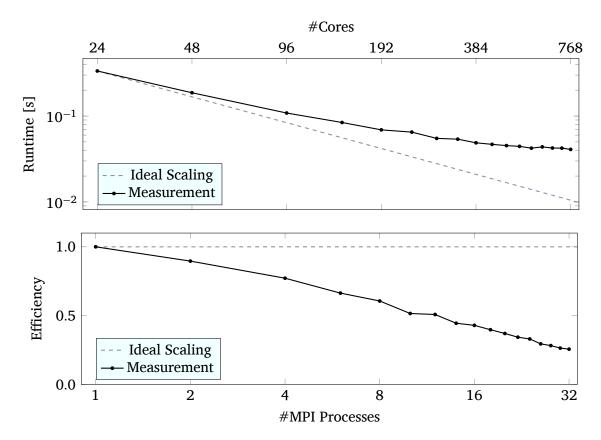

|    | 4.4    | Proof     | of Concept Benchmark                          |

| 5  | Con    | CLUSIC    | on & Outlook                                  |

| D٠ | DI 104 | 7D 4 DIII |                                               |

| DΙ | RTIO(  | JKAPH '   | Y                                             |

# LIST OF FIGURES

| 1.1  | Cores per Node/Clock Speed              | 2  |

|------|-----------------------------------------|----|

| 1.2  | Flynn's Taxonomy with Johnson Extension | 2  |

| 1.3  | Low Level and High Level Interface      | 3  |

| 1.4  | Two Developer Roles in HPC              | 3  |

| 1.5  | CRTP UML Class Diagram                  | 9  |

| 1.6  |                                         | 10 |

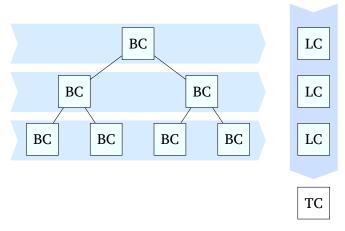

| 2.1  |                                         | 14 |

| 2.2  |                                         | 14 |

| 2.3  | Multipole and Local Expansions          | 15 |

| 2.4  |                                         | 17 |

| 2.5  | Multipole to Multipole Operator         | 17 |

| 2.6  |                                         | 18 |

| 2.7  |                                         | 19 |

| 2.8  |                                         | 20 |

| 2.9  |                                         | 20 |

| 2.10 |                                         | 21 |

| 2.11 |                                         | 22 |

| 2.12 |                                         | 23 |

| 2.13 |                                         | 24 |

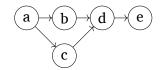

| 3.1  | Graph Drawing Example                   | 32 |

| 3.2  | Data-Flow Graph Example                 | 33 |

| 3.3  |                                         | 34 |

| 3.4  |                                         | 36 |

| 3.5  |                                         | 38 |

| 3.6  |                                         | 39 |

| 3.7  |                                         | 41 |

| 3.8  |                                         | 42 |

| 3.9  |                                         | 43 |

| 3.10 |                                         | 44 |

| 3.11 |                                         | 45 |

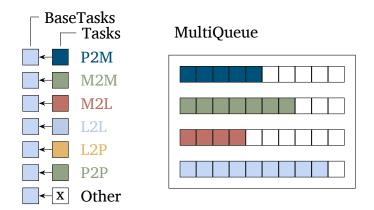

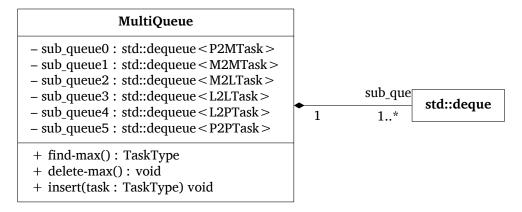

| 3.12 | Simple Multi-Queue UML Class Diagram    | 47 |

|      |                                         | 54 |

|      | · · · · · · · · · · · · · · · · · · ·   | 56 |

|      |                                         | 59 |

|      | <del>-</del>                            | 61 |

|      |                                         | 62 |

|      | 1 7                                     | 63 |

|      | inclardity of dounters                  |    |

# List of Figures

| 3.20 Object Wrapper                        | 65  |

|--------------------------------------------|-----|

| 3.21 MESI Protocol                         | 68  |

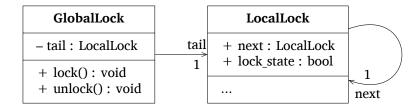

| 3.22 MCS-Lock UML Class Diagram            | 70  |

| 3.23 MCS-Lock Example                      | 70  |

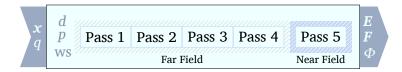

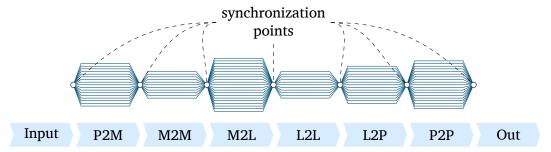

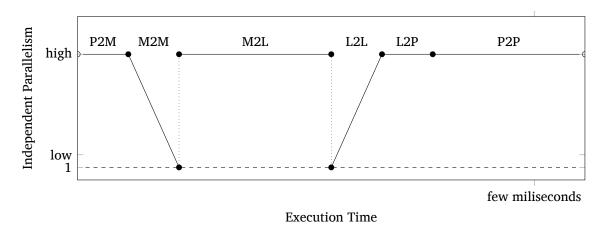

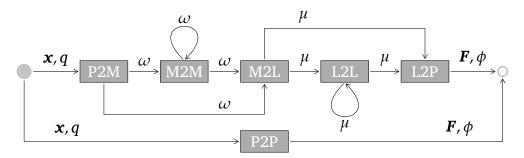

| 3.24 FMM Flow                              | 72  |

| 3.25 FMM Loop-Level Parallel               | 72  |

| 3.26 Available Parallelism                 | 73  |

| 3.27 FMM Data-Flow Graph                   | 74  |

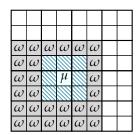

| 3.28 Target or Source Centric M2L Operator | 75  |

| 3.29 Overhead Analysis                     | 78  |

| 3.30 Work-Time Inflation of M2L Operator   | 78  |

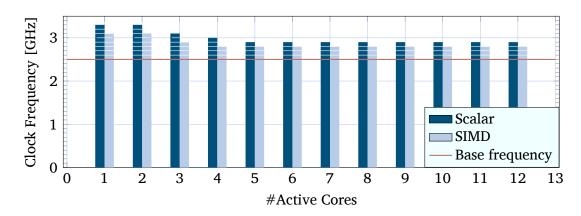

| 3.31 Intel Turbo Boost                     | 79  |

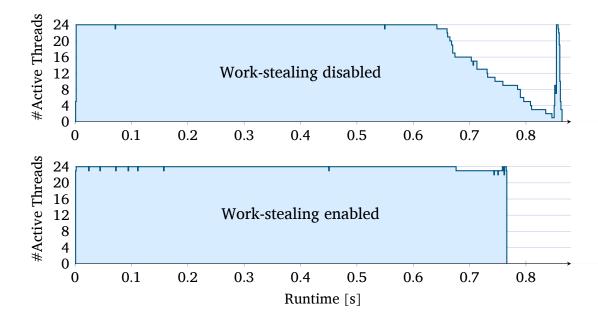

| 3.32 Idle-Time Analysis                    | 79  |

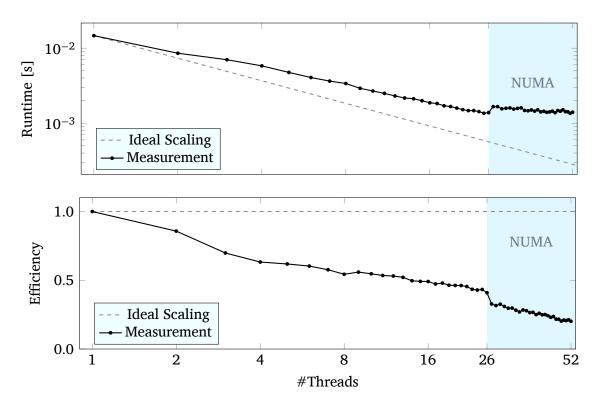

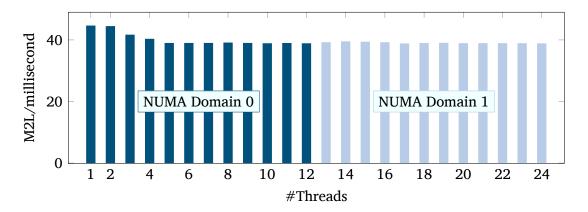

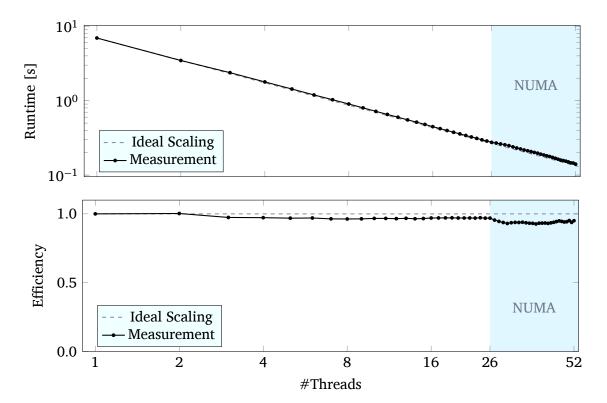

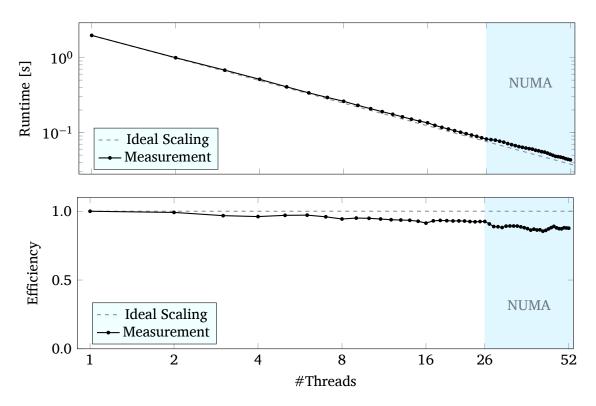

| 3.33 NUMA Analysis                         | 80  |

| 3.34 Lock Performance Comparison           | 81  |

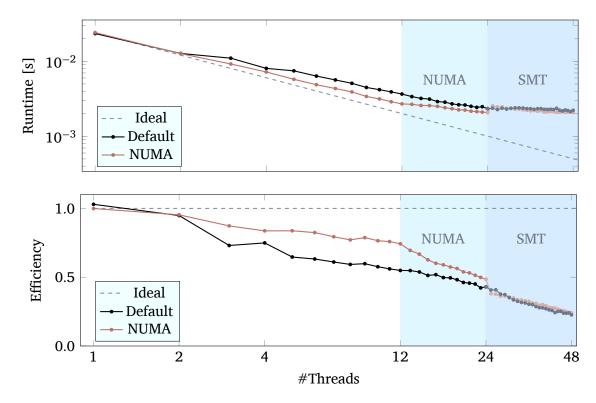

| 3.35 Real World Benchmark                  | 82  |

| 3.36 Real World Benchmark Low Accuracy     | 83  |

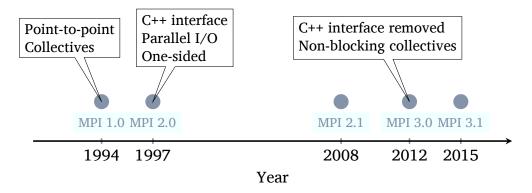

| 4.1 Historical Development of MPI          | 87  |

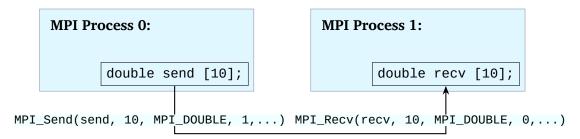

| 4.2 MPI Point-to-Point Communication       | 88  |

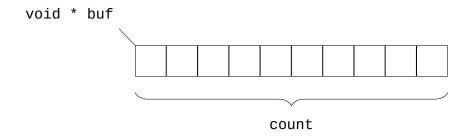

| 4.3 MPI Communication Data                 | 89  |

| 4.4 Serialized Coordinates                 | 96  |

|                                            | 100 |

| 4.6 MPI Proof of Concept                   | 107 |

# **LIST OF TABLES**

| 3.1 | Bucket-Based Priority Queue Complexities | 42 |

|-----|------------------------------------------|----|

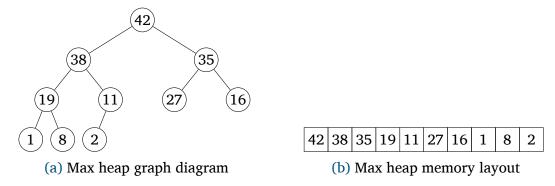

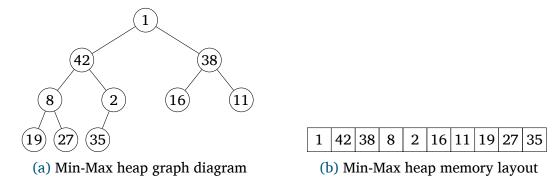

| 3.2 | Max Heap Priority Queue Complexities     | 44 |

| 3.3 | Min-Max Heap Priority Queue Complexities | 44 |

| 3.4 | Type-Driven Priority Queue Complexities  | 45 |

| 3.5 | Hardware Characteristics                 | 77 |

# **LIST OF LISTINGS**

| 1.1  | Example of compile-time branching                     | 9  |

|------|-------------------------------------------------------|----|

| 1.2  | Example of curiously recurring template pattern       | 9  |

| 3.1  | ThreadDormitory implementation                        | 35 |

| 3.2  | AbstractProcessor class implementation using CRTP     | 37 |

| 3.3  | P2MProcessor as a concrete processor example          | 37 |

| 3.4  | Simple MultiQueue M2L insert method                   | 47 |

| 3.5  | Iterating over the elements of an std::tuple          | 48 |

| 3.6  | Generic insert method of the MultiQueue               | 49 |

| 3.7  | Test program for virtual function calls               | 50 |

| 3.8  | Difference in assembly of the v-table test program    | 50 |

| 3.9  | ExecuteTask method                                    | 51 |

| 3.10 | MultiQueue insert method primary template             | 52 |

| 3.11 |                                                       | 52 |

| 3.12 | ExecuteNextOrdered method of the MultiQueue           | 53 |

| 3.13 | Examples of the MultiQueue definition                 | 55 |

| 3.14 | Data-Events and event handlers                        | 57 |

| 3.15 | Callable helper class for event handlers              | 57 |

| 3.16 | Definition of the EventListener Type                  | 58 |

| 3.17 | EventListenerContainer for collecting EventListeners  | 58 |

| 3.18 | EventListener template                                | 60 |

| 3.19 | An example of a static data-flow dispatcher           | 61 |

| 3.20 | DependencyCounter wrapper class                       | 62 |

| 3.21 | Definition of default values for dependency counters  | 63 |

|      | Implementation of the ObjectWrapper                   | 66 |

|      | Mutex lock specialization of object access strategy   | 66 |

| 3.24 | ObjectAccess used for mutex lock strategy             | 67 |

| 4.1  | Reference of non-blocking send and receive            | 88 |

| 4.2  | Allgather collective communication from MPI standard  | 90 |

| 4.3  | Example of a generic 3D coordinate class              | 90 |

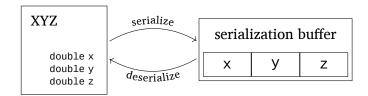

| 4.4  | Example of point-to-point communication of XYZ        | 91 |

| 4.5  | MPITypeTraits template primary definition             | 94 |

| 4.6  | MPITypeTraits specialization for int                  | 94 |

| 4.7  | Defining a generic type for a 3D coordinate           | 94 |

| 4.8  | Remove the constant qualifier from the type           | 95 |

| 4.9  | The serialize method of the 3D coordinate             | 97 |

| 4.10 | The serialize method of a nested object               | 97 |

| 4.11 | SerializationBuffer ampersand operator implementation | 98 |

# List of Listings

| 4.12 | Parts of the InputSerializationAdapter                       | 98  |

|------|--------------------------------------------------------------|-----|

| 4.13 | SizeAdapter for the computation of the serialized size       | 99  |

| 4.14 | Mpiwrapper Irecv implementation                              | 102 |

| 4.15 | Mpiwrapper Allgather implementation                          | 102 |

| 4.16 | Example of point-to-point communication of XYZ using wrapper | 103 |

| 4.17 | Point-to-Point communication of a multipole expansion        | 103 |

| 4.18 | Communication of coordinates using the CollectivesWrapper    | 104 |

| 4.19 | SendQueue implementation                                     | 105 |

# LIST OF ACRONYMS

API Application program interface

CAS Compare-and-swap

**CRTP** Curiously recurring template pattern

DAG Directed acyclic graph

FFT Fast Fourier Transform

**FIFO** First in – first out

FMM Fast Multipole Method

**HPC** High performance computing

**JSC** Jülich Supercomputing Centre

L2L Local to local

**LIFO** Last in – first out

**M2L** Multipole to local

M2M Multipole to multipole

**MD** Molecular dynamics

MPI Message passing interface

**NUMA** Non-uniform memory access

**PGAS** Partitioned global address space

PME Particle Mesh Ewald

**RDMA** Remote direct memory access

**SFINAE** Substitution failure is not an error

SIMD Single instruction, multiple data

**SIMT** Single instruction, multiple threads

SMT Simultaneous multithreading

TBB Thread building blocks

## List of Acronyms

TMP Template-meta-programming

**ULT** User-level-threads

**UMA** Uniform memory access

## **ABSTRACT**

Today's supercomputers gain their performance through a rapidly increasing number of cores per node. To tackle issues arising from those developments new parallelization approaches guided by modern software engineering are inevitable. The concept of task-based parallelization is a promising candidate to overcome many of those challenges. However, for latency-critical applications, like molecular dynamics, available tasking frameworks introduce considerable overheads. In this work a lightweight task engine for latency-critical applications is proposed. The main contributions of this thesis are a static data-flow dispatcher, a type-driven priority scheduler and an extension for communicationenabled tasks. The dispatcher allows a user-configurable mapping of algorithmic dependencies in the task-engine at compile-time. Resolving these dependencies at compile-time reduces the run-time overhead. The scheduler enables the prioritized execution of a critical path of an algorithm. Additionally, the priorities are deduced from the task type at compile-time as well. Furthermore, the aforementioned task engine supports inter-node communication via message passing. The provided communication interface drastically simplifies the user interface of inter-node communication without introducing additional performance penalties.

This is only possible by distinguishing two developer roles – the library developer and the algorithm developer. All proposed components follow a strict guideline to increase the maintainability for library developers and the usability for algorithm developers. To reach this goal a high level of abstraction and encapsulation is required in the software stack. As proof of concept the communication-enabled task engine is utilized to parallelize the FMM for molecular dynamics.

CHAPTER 1

# INTRODUCTION

Computational science has become "The 'Third Pillar' of 21st Century Science" [100, pp. 12] positioned between theory and experiment blurring the line between both of them. Several scientific breakthroughs like the decoding of the human genome [45] or the space missions to Mars [116] would have been impossible without computational science and computer simulations. Fields like drug research utilize computer simulations to discover new use cases and allow to predict unknown side effects. For almost all fields of science, computer simulations have become virtually indispensable. The resources required for those computer simulations form the rising field of high performance computing (HPC). The rapid increase in affordable computational resources and powerful hardware enables simulations that have been unthinkable decades ago. Nowadays, large scale simulations required for the weather forecast [24, 119] or simulations of quantum computers [120] are only possible because supercomputers offer a vast amount of computational power. This development took on momentum and with exascale in sight [79] further scientific insights will be discovered by an increasing field of applications.

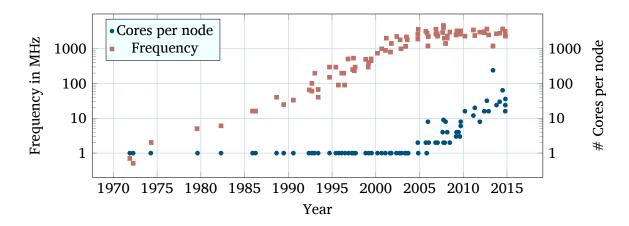

However, utilizing exascale hardware to the full extend will be challenging. In the past, supercomputers gained most of their performance by adding more nodes to the system. Additionally, an almost free performance increase came from the raised clock-speed of the processors and shrinking die sizes due to Moore's law [84]. A few years into the new millennium the clock-speed stagnated and further performance improvements were only possible through the advent of multicore processors. This also changed the subsequent development of supercomputers. Instead of increasing the performance by increasing the numbers of nodes, the nodes themselves became more powerful (see Figure 1.1). For the ongoing development towards exascale this means, the number of cores per node will increase rapidly, whereas the number of nodes will increase only moderately [11]. This inevitable leads to a more complex node. Additionally, new and wider vector instructions or the introduction of non-uniform memory access (NUMA) contribute to the complexity as well. Besides classical CPUs also new architectures like GPUs or other accelerators emerged, requiring completely differ-

Figure 1.1: A comparison of the development of the CPU frequency and the number of cores per node in the TOP500 list [111].

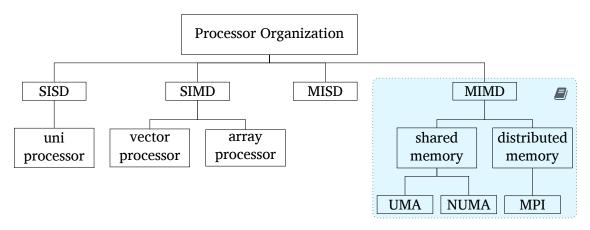

Figure 1.2: Flynn's Taxonomy and Johnson extension for MIMD architectures.

ent programming models. Referring to Flynn's extended taxonomy [40, 67] this prolonged trend holds parallelization potentials on many levels of the available hardware (see Figure 1.2).

The overall development of HPC led to many diverse systems already today, offering quadrillion ( $10^{15}$ ) of floating-point operations per second. For systems passing the exascale with quintillion ( $10^{18}$ ) of floating-point operations the hardware will become even more complicated in comparison [4]. These developments are ubiquitous in HPC and will also enforce changes on the software development. This work will contribute to the handling of rapidly developing hardware and focuses on the software engineering challenges.

How did the software development for HPC evolve? For the parallelization, the first supercomputer applications used only inter-node communication techniques to distribute the data between nodes in an otherwise sequential program. With the advent of multicore processors shared memory parallelization was required for the first time. Exploiting loop-level parallelism by sprinkling pragmas throughout

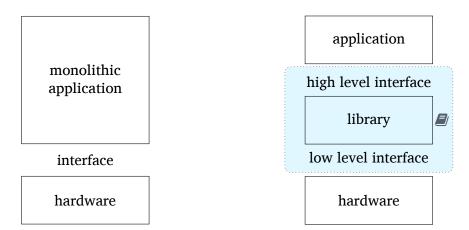

Figure 1.3: The separation of concerns splits the monolithic application into a high level and a low level layer.

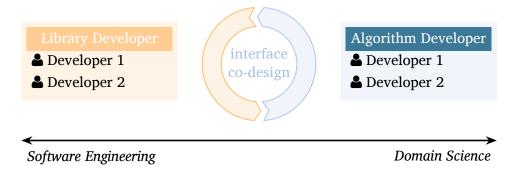

Figure 1.4: The distinguishing of two developer roles in HPC. The library developer is responsible for the low level library and hardware abstraction. The library developer provides an easy-to-use interface to the algorithm developer. The algorithm developer is responsible for the algorithm and the implementation of the algorithm using the high level interfaces provided by the library developer.

the sequential code at each loop construct solved the problem initially. However, this led to programs with millions of lines of code, being hardly maintainable and unable to adapt to even more sophisticated hardware features like vectorization.

To remain sustainable modern software requires abstractions of hardware in a more generic manner. Additionally, the separation of concerns between algorithm-specific parts of the program and the parallelization and hardware specific parts should be enforced (see Figure 1.3). In the past, for most programs a single domain scientist was responsible for everything: the algorithm, implementation, parallelization, optimization and porting. With the rapid development of new hardware and the thereby increased complexity, this is not manageable by a single software developer anymore. Therefore, the proposed separation of concerns in the software must also be considered for the software developers themselves.

This can be achieved by distinguishing two different software developer roles

in HPC (see Figure 1.4):

**The Library Developer** is responsible for the low level libraries encapsulating hardware features and parallelization. The library developer is also responsible for providing a high level interface which can be used by the algorithm developer that ideally hides most of the non-performance-critical features.

The Algorithm Developer is responsible for the high level algorithmic details and the implementation of the algorithm using the high level interfaces provided by the library developer.

Algorithmic development should be independent of specific hardware. This differentiation allows the individual developer to focus on the challenges specifically arising in their field of expertise. The challenges in providing parallelization tools and low level implementations are shifted towards computer science. Simultaneously it relieves the library developer from the responsibility of fully understanding algorithmic details and vice versa.

Even though this work focuses on the library developer side of the classification a use case for the proposed concepts is required. For this purpose the Fast Multipole Method (FMM) for solving long range interactions in molecular dynamics (MD) was chosen. This method exhibits parallelization challenges already today that other application might not experience until the exascale era. In MD the particle movement of a fixed particle system is simulated usually encompassing thousands to millions of particles. The simulation is done in discrete time steps each evaluating the long range potentials and forces using the FMM. For a reasonable simulation time millions of time steps are necessary. To avoid an excessive overall runtime, the single step runtime of the FMM must therefore be in the range of only a few milliseconds. To reach that goal massive parallelism needs to be exploited and therefore each compute unit (core) will only hold a few particles. But for a few particles per core only very little computations per core are required and data transfer and communication overheads become apparent. These kind of problems will be called latency-critical problems in this work.

To perform the parallelization of latency-critical problems, the library developer needs to provide a programming model suited for the task at hand. The programming model of this work is restricted to the shared memory parallelization and distributed parallelization in Flynn's taxonomy (see Figure 1.2). For the parallelization a coupled solution for both problems will be presented. This stands in contrast to all-inclusive solutions for inter-node and intra-node parallelization like HPX [70], Charm++ [71], PaRSEC [19] and DAGuE [18]. These libraries work well for coarse-grained tasks encompassing a sufficient number of computations. However, for latency-critical problems fine-grained tasks must be used and those approaches do not provide sufficient control to adapt the parallelization layer to the requirements of the algorithm.

For the parallelization of latency-critical application it is necessary to control the program flow on all levels. Therefore, the parallelization concepts and tools

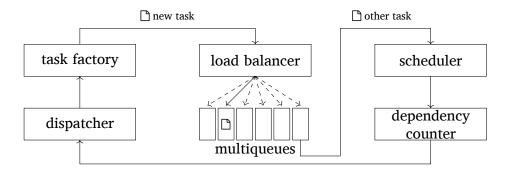

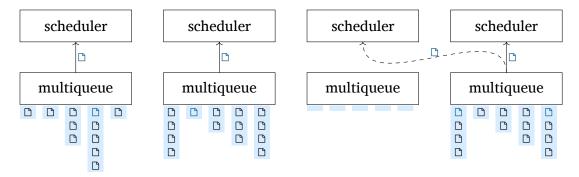

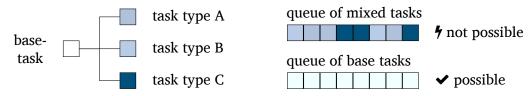

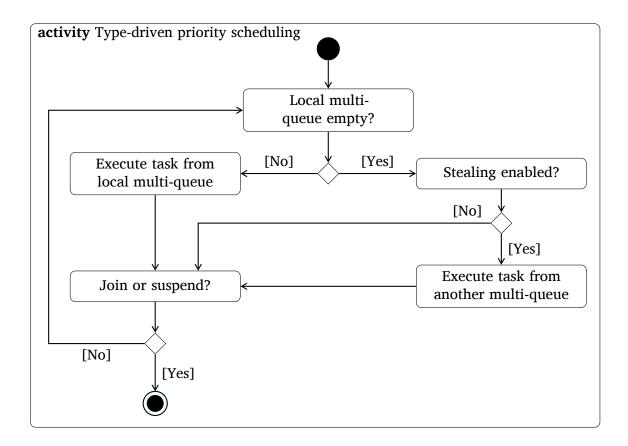

proposed within this work deal with intra-node and inter-node parallelization separately. In the chapter on intra-node parallelization current state of the art parallelization approaches will be discussed and a task engine specialized for latency-critical problems will be proposed. This task engine includes two unique components not available in other frameworks, namely the static data-flow dispatcher and the type-driven priority scheduler. The static data-flow dispatcher is compile-time configurable with algorithmic dependencies. The type-driven priority scheduler, schedules tasks using different priorities which are automatically deduced from the type of the task.

For the inter-node parallelization existing approaches and libraries will be discussed in the chapter inter-node parallelization. There, the task engine will be extended with a communication layer. This communication layer simplifies the communication interface for message passing and provides an easy-to-use high level interface for the algorithm developer. Additionally, initial concepts for task-based communication using fine-grained tasks will be shown.

#### **NOMENCLATURE**

For the remainder of this work the following nomenclature is used: A supercomputer consists of several compute nodes, which are connected with a fast network. A compute node has one or more sockets. A processor refers to a single socket CPU. This processor consists of one or more cores. On a core one or more hardware-threads are executed, depending on simultaneous multithreading (SMT).

#### 1.1 DESIGN GUIDELINES

The implementation follows several well-established software design guidelines and principles. The following four design goals are the most important ones:

- **>** Correctness,

- > Maintainability,

- > Sustainability and

- **>** Performance portability.

#### **MAINTAINABILITY**

For the long-term use of a library it is very important to provide a maintainable and readable code base. Without this requirement, it is hard to extend the library at a later point in time or adapt to new circumstances. During the implementation phase this guideline has been enforced with test-driven development [75].

An additional strategy is to stick to well established coding principles. One famous principle is the object oriented design principle SOLID [77]. SOLID consists of the following five sub-principles:

**The single-responsibility principle (S)** states, that every class or module should only have a single responsibility. This results in code with a high level of encapsulation.

- **The open/closed principle (O)** states, that the software should be "open for extension, but closed for modification" [80]. This means, that changes to a component or a class should only be possible by extension like inheritance, but not by changing the existing implementation itself.

- **The Liskov substitution principle (L)** states, that properties valid for one type should still be valid when exchanging this type with its sub-type [76].

- The interface segregation principle (I) states, small interfaces are better than big ones and thereby often too general interfaces.

- **The dependency-inversion principle (D)** suggest to better depend on abstractions instead of concrete classes.

These principles already require code with a high level of abstraction and encapsulation. Additionally, the "Don't repeat yourself" (DRY) principle [59] was followed in the implementation.

#### PERFORMANCE PORTABILITY

For applications in HPC it is expected to show good performance on the latest hardware platform. Due to the frequent changes and availability of diverse supercomputers, nowadays it is required to exhibit convincing performance on many different platforms. This requirement is herein called performance portability.

As described before the computing hardware changes in many directions. To handle quantitative changes in hardware effectively a high level of abstraction is required. For legacy software written in Fortran or C this means a lot of work porting and optimizing code to new supercomputers. Adapting to all changed hardware features and optimizing historically grown software by hand is time consuming and potentially prone to errors.

This problem can be partially solved by abstracting away the target hardware in an generic manner. Using template-meta-programming (TMP) features of C++ this can be achieved without constantly porting software by hand. Such an approach will pose a challenge to library developers, but ultimately will help domain scientists to harvest the performance of the target hardware without the need to understand hardware details. The herein proposed abstractions come with zero runtime overhead and are to this extend only possible using C++ and TMP. This makes C++ a first choice for solving the challenges for the programming of current and future supercomputers.

## 1.2 HPC AND C++

Parallelization of supercomputers cannot be discussed without putting it in context to the used programming language. The most common programming languages supported on supercomputers are Fortran, C and C++, whereas Fortran an C are the most prevailing [121, 82]. Only a few application are using C++ and when it comes to modern C++ with template-meta-programming, the numbers are even lower.

This fact is surprising since C++ has a lot to offer – especially for HPC. C++ is a mature industrial standard [66] with an established standardization process and a vivid community. The most important extension of the language for parallel computing was added in the 2011 standard. This extension concerned the memory model and the multithreaded execution capabilities directly inscribed in the language [16, 118]. Before the availability of this extension, non of the languages used in HPC were inherently parallel. It was required to use external libraries like pthreads [89] but this raised thread safety concerns [15].

The upcoming HPC technologies are not uniform anymore and the HPC ecosystem will be more diverse in future. As mentioned before, this requires a high level of abstraction in order to reach performance portability more easily and C++ has a solution for that as well. Zero-overhead abstraction [49] is one of the main design principles of the C++ language itself. As the founder of C++ B. Stroustrup said [106]:

In general, C++ implementations obey the zero-overhead principle: What you don't use, you don't pay for. And further: What you do use, you couldn't hand code any better.

Zero-overhead abstraction refers specifically to inheritance and template-meta-programming (TMP). This work is heavily based on modern C++ features and especially on TMP abstraction capabilities. In the following the foundational concepts and special language features required for the intra-node and inter-node parallelization are laid out.

#### COMPILE-TIME ABSTRACTION

Zero-overhead abstractions have been possible by using pre-processor macros in C, Fortran and C++. Besides pre-processor macros, C++ additionally offers templates. Both, C++ templates and pre-processor macros are evaluated at compile time. But in contrast to pre-processor macros, templates are part of the type system of C++. This means, that potential bugs that could arise at runtime or stay undetected, will be identified at compile-time. This increases the robustness of the code [107] tremendously.

Thus, besides the increased performance, maintainability and increased robustness are the main reasons for using C++ templates. Since it is possible to have many fine-grained layers of software designed in such a way, true separation of concerns becomes possible.

#### **GENERIC PROGRAMMING**

Generic programming describes the term of program code being independent of the actual type. This is well known from generic data structures like the vector in the C++ standard template library. The implementation of those data structures is available independently of the concrete type. Instead of concrete types, placeholders are used. These placeholders are called template parameters. These data structures can be used by applying the desired type. The compiler will

generate the code by replacing the placeholder with the desired type. Since the template parameters are replaced by concrete types at compile-time this comes without runtime overhead. This makes generic programming to an preeminent zero cost abstraction feature.

C++ offers class and function templates. These functions or classes may have template parameters. Template parameters can either be types or non-type template parameter like integers. Since C++11 it is also possible to use template packs, which is an arbitrary number of template parameters defined in a single pack.

#### **TEMPLATE SPECIALIZATION**

The original use case of templates in C++ was generic programming. Template-meta-programming (TMP) itself and the Turing completeness [115] of TMP were discovered by accident. However, the mature feature set and abstraction capabilities of TMP makes it indispensable for this work. Not utilizing TMP would require to implement a lot of compiler generated code by hand in order to reach a comparable performance and portability. This would sweep away the configurability of any library developed today.

Template specialization is the first step towards template-meta-programming (TMP). Function templates as well as class templates can be fully specialized. This means, the specialized implementation can be provided for a certain combination of template parameters. This is especially helpful for implementing generalized compute kernels not depending on a specific floating point type.

Additionally, class templates have the capability of partial template specialization. In contrast to the full template specialization, only parts of the template parameter list needs to be specialized. The remainder of the template parameters are still generic.

#### **COMPILE-TIME BRANCHING**

With a classical *if-then-else*-condition a branch of the control-flow can be determined. If it is possible to evaluate the condition at compile-time, it would be ideal to choose the branch at compile-time. With C++ and TMP this is possible. Therefore, compile-time branching is an important feature for the implementation of reusable code.

One concept facilitating compile-time branching is "substitution failure is not an error" (SFINAE). The concept of SFINAE can be described as follows: An invalid substitution of a template parameter during function overload resolution does not result in an compile-time error, but rather discards this function definition. This means, the same function could be implemented multiple times with different template parameter definitions. For calling the function template, the template parameters need to be applied either explicitly or by template argument deduction. During the overload resolution the applied parameters are substituted in all function definitions. The substitution may lead to an ill-formed function definitions, causing a substitution failure. However, this failure is not an error and the function will be discarded from the overload resolution.

#### **LISTING 1.1:** EXAMPLE OF COMPILE-TIME BRANCHING

Figure 1.5: The UML class diagram of static inheritance using CRTP.

It is important, that only one function definition remains, otherwise the function definition would be ambiguous.

For the concrete implementations the type trait std::enable\_if can be used. An example using SFINAE and enable\_if is shown in Listing 1.1. In case the condition used evaluates to true the first function implementation is used (see line 3), otherwise the second implementation will be executed (see line 7).

#### STATIC INHERITANCE

Static inheritance could be used to share behavior between classes without introducing virtual inheritance overhead. The advantage is the reduction of code duplication and hence an increased robustness and maintainability. One TMP technique enabling static inheritance is called curiously recurring template pattern (CRTP).

For CRTP a derived class inherits from a common templated base class (see Figure 1.5). Listing 1.2 shows an example of CRTP. The base class (AbstractBase)

#### LISTING 1.2: EXAMPLE OF CURIOUSLY RECURRING TEMPLATE PATTERN

```

1 template <typename Derived>

2 struct AbstractBase {

3    Derived & derived() {

4     return *static_cast<Derived *>(this);

5    }

6    void virtual_method() {

7     derived().virtual_method();

8    }

9    };

10

11 struct ConcreteDerived : AbstractBase<ConcreteDerived> {

12    void virtual_method() {}

13 };

```

uses a template parameter (Derived) which reflects the derived class. This means, strictly speaking derived classes do not have a common base class due to their different template parameters. In the base class it is possible to statically cast the object towards an instance of the derived class shown in the method derived(). With the help of such a cast, shared behavior can be implemented in the base class. By implementing the same method in the derived class, the method of the base class can be hidden. Additionally, methods behaving like virtual inheritance can be implemented. In the example given in the listing, the method virtual\_method calls the implementation of the derived class. This is done by calling the method on the derived class using the cast method derived().

#### 1.3 Molecular Dynamics

Molecular dynamics (MD) simulations characterize the evolution of a particle system over time. Therefore, the movement of particles due to their interactions is simulated. MD has a long history in computational science starting from the late sixties [3]. There are several MD implementations like Gromacs [56], NAMD [88] or Amber [22] available today. Due to the high demand in computational resources, also special purpose hardware was developed to compute MD simulations like MD Grape [46] and D.E. Shaw's Anton [103].

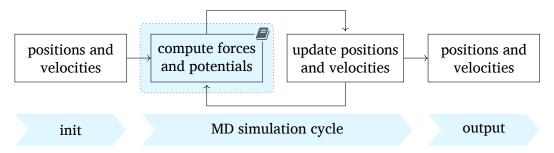

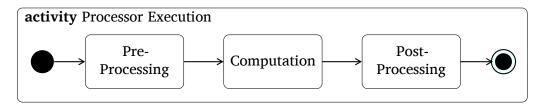

The simulation itself is performed in discrete time steps. These time steps are computed in the so called MD-loop which is shown in a simplified diagram in Figure 1.6. In general an MD loop can be described as follows. The long-range and short-range interactions (potentials and forces) are computed. The computed forces are used to determine the new particle positions in the next time step. Then, the process starts over again using the new particle coordinates. It should be mentioned, that the loop introduces an implicit synchronization. The integration can only take place after all interactions are computed.

The simulated particle systems usually consist of hundred thousands to several million of charged particles. These particles might resemble proteins, DNA or even bio-molecules like whole viruses [124]. Since the common time step required for those MD simulations is in the range of femtoseconds and the desired total simulation time is required to be in the micro- or even milliseconds, the total number of time steps therefore will be in the millions to billions. To maintain a

Figure 1.6: The simplified version of the internal MD Loop.

reasonable total runtime the execution time required for a single time step needs to be in the lower millisecond range. Since the number of particles can not be increased arbitrarily, weak-scaling is not an option and the development of MD has to focus on strong-scaling. This already imposes challenges in the parallelization on current petascale hardware.

This work contributes to a software module for the MD simulation toolbox Gromacs and is embedded in the code development of the SPPEXA [21] project GROMEX [53]. Gromacs is an open source software developed in Europe. It has a large user-base of several thousand scientists in academia and research. Additionally, the project has been included in the folding@home community extending the compute power to thousands of clients [101]. Such a large and diverse user-base requires the code to run on a multitude of hardware ranging from a student's laptop to the latest supercomputer.

One might ask, what is the most time consuming part of such MD simulations? Since the integration step is embarrassingly parallel and has no inter-particle dependencies it only takes a tiny portion of the overall runtime. The overwhelming part of the runtime is consumed by the computation of the long-range interactions. Since all mutual interactions have to be computed, the naïvely exhibited computational complexity is  $\mathcal{O}(N^2)$  with respect to the number of particles N. With the help of Particle Mesh Ewald (PME) this complexity can be reduced to  $\mathcal{O}(N\log N)$ . Nevertheless, the significant part of runtime still stems from the long-range interactions. Additionally, PME itself has another drawback. Since it employs a Fast Fourier Transform (FFT) it has an inherent parallel scaling bottleneck due to global communication requirements of such FFTs. The contributed software module exchanges the PME algorithm with the FMM for the computation of long-range interactions.

## THE FMM IN A NUTSHELL

The Fast Multipole Method (FMM) is a numerical method for solving the N-body problem. The N-body problem is about the computation of all pairwise interactions between *N* particles. Those particles might be charges interacting due to electrostatic forces or masses interacting due to gravitational forces. This work focuses especially on the computation of the Coulomb potential arising in molecular dynamics.

**Definition 2.1** The **Coulomb potential** at target position  $x_i$  for N source particles at positions  $x_i \in \mathbb{R}^3$ ;  $i, j \in \{1, ..., N\}$  and the corresponding charges  $q_i$  is defined as:

$$\Phi\left(\mathbf{x}_{i}\right) = \sum_{j=1}^{N} \frac{q_{j}}{\left\|\mathbf{x}_{i} - \mathbf{x}_{j}\right\|_{2}} \quad (i \neq j) . \tag{2.1}$$

The corresponding force at target particle at position  $x_i$  with charge  $q_i$  is defined as:

$$\boldsymbol{F}\left(\boldsymbol{x}_{i}\right) = q_{i} \sum_{j=1}^{N} \frac{q_{j}}{\left\|\boldsymbol{x}_{i} - \boldsymbol{x}_{j}\right\|_{2}^{3}} \left(\boldsymbol{x}_{i} - \boldsymbol{x}_{j}\right) \quad (i \neq j) . \tag{2.2}$$

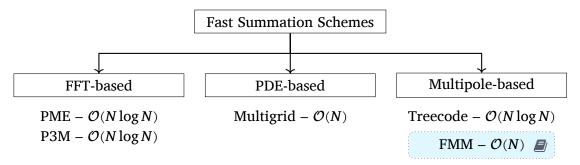

As seen in Equation 2.1, the computation of a single potential  $\Phi(x_i)$  has linear complexity. Since potentials should be evaluated for N particles, the N-body problem exhibits a computational complexity of  $\mathcal{O}(N^2)$ . This complexity is unfavorable for large simulations since the computation time increases rapidly and thereby limits the size of the simulation. There are several fast summation schemes like particle mesh Ewald [31] and Barnes-Hut [12] reducing the complexity to  $\mathcal{O}(N\log N)$  and multigrid methods [112] even exhibiting only linear complexity.

The Fast Multipole Method (FMM) also exhibits linear complexity. It was first described in 1987 by Greengard and Rokhlin [50]. This work discusses a FMM specialized for MD focusing only on the Coulomb potential. Nevertheless, many other FMM implementations exist for the Coulomb or gravitational potential like ExaFMM [123] or ScalFMM [2]. However, those implementations lack optimization and specialization for the constraints introduced by the MD use case like

Figure 2.1: Computational complexity of different fast summation schemes with reduced complexity.

homogeneous distributed particles and execution time close to a millisecond. Additionally, other FMM implementations have been proposed for arbitrary kernels in a kernel independent way like KIFMM [122].

The main idea of the FMM is the grouping of far distant particles into expansions. These expansions are used for the computation of pseudo interactions between the groups instead of the computation of every single interaction between particles of these groups. The following notation and derivation is adapted from the FMM proposed in [69].

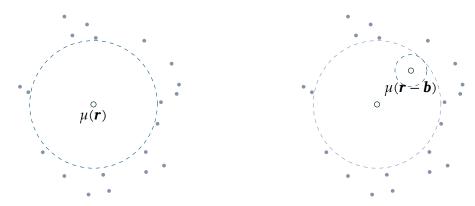

#### 2.1 Particle Grouping

To get a better understanding on how the FMM works, the particle distribution shown in Figure 2.2a is assumed. The particles are positioned in a way, that no overlapping of the spheres containing the particles can occur. The first group contains M particles and the second group contains N particles. If the interactions between particles inside a sphere are ignored, this results in  $M \cdot N$  interactions.

As long as the distance between the two groups is big enough, a change of the particle position in one group does only slightly influence the computed potentials in the other group. This means, instead of computing all  $M \cdot N$  interactions, only one pseudo interaction between both groups can be computed (see Figure 2.2b). This pseudo interaction was not introduced yet, but a first approximation could be to sum up all charges of particles inside the group. This sum can be assigned

Figure 2.2: Grouping and interaction of far distant particles for classical direct interaction via particles and interaction via pseudo-particles (multipoles).

to a pseudo particle at the center of the group. This interaction would be called a monopole interaction. Taking higher order expansions like dipoles, quadrupoles, octopoles or hexapoles into account increases the accuracy. Obviously, this approach introduces errors since the expansion must be finite. However, there exists an expansion order that corresponds to the precise (direct) computation of the system. Since other errors are introduced by the MD simulation it is sufficient to use a lower precision requirement for the FMM as well. This will speed up the computation even more.

#### 2.2 Multipole and Local Expansions

For the computation of the forces and the potentials, the FMM utilizes two different expansions. The first is the multipole expansion and the second is the local expansion. The derivation can be performed in Cartesian coordinates, however, using spherical coordinates results in a more compact representation. In order to derive the spherical expansions additional polynomials are required:

**Definition 2.2** The **Legendre polynomials** with  $l \in \mathbb{N}_0$  are defined as:

$$P_{l}(x) = \frac{1}{2^{l}l!} \frac{d^{l}}{dx^{l}} \left[ (x^{2} - 1)^{l} \right].$$

**Definition 2.3** The associated Legendre polynomials with  $m \in \mathbb{Z}$  are defined as:

$$P_{lm}\left(x\right) = \left(-1\right)^{m} \left(1-x^{2}\right)^{m/2} \frac{d^{m}}{dx^{m}} P_{l}\left(x\right) \quad \left(|m| \leq l\right) \; .$$

**Definition 2.4** A complex coefficient  $\omega_{lm} \in \mathbb{C}$  of the **multipole expansion**  $\omega$  of k particles with position  $\mathbf{a}_j = (a_j, \alpha_j, \beta_j), j \in \{1, \dots, k\}$  inside a sphere with radius  $\hat{a}$  and center  $\mathbf{a} = (a, \alpha, \beta)$  with  $a_j < \hat{a}$  and corresponding charges  $q_j$  is defined as:

$$\omega_{lm}\left(\boldsymbol{a}\right) = \sum_{j=1}^{k} \frac{q_{j} a_{j}^{l}}{(l+m)!} P_{lm}\left(\cos \alpha_{j}\right) e^{-im\beta_{j}}.$$

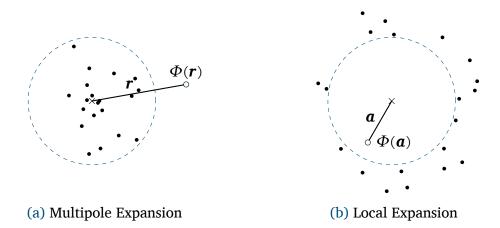

Figure 2.3: Multipole expansion and local expansion with corresponding potential  $\Phi$ .

**Definition 2.5** A complex coefficient  $O_{lm}(a) \in \mathbb{C}$  of the chargeless multipole expansion of a point  $a = (a, \alpha, \beta)$  is defined as:

$$O_{lm}(\boldsymbol{a}) = \frac{a^l}{(l+m)!} P_{lm}(\cos \alpha) e^{-im\beta}.$$

Assuming a point  $\mathbf{r} = (r, \theta, \phi)$  with  $r > \hat{a}$  outside the sphere of the multipole (see Figure 2.3a), the potential at this point introduced by the particles represented by the multipole expansion  $\omega(\mathbf{a})$  is given by:

$$\Phi\left(\mathbf{r}\right) = \sum_{l=0}^{\infty} \sum_{m=-l}^{l} \omega_{lm}\left(\mathbf{a}\right) \frac{(l-m)!}{r^{l+1}} P_{lm}\left(\cos\theta\right) e^{im\phi}. \tag{2.3}$$

The multipole expansion is valid for the computation of the potential for all points outside the sphere. The convergence with respect to the expansion length of the potential increases for increasing distance between the sphere and the evaluation point  $(r \gg a)$ .

**Definition 2.6** A complex coefficient  $\mu_{lm}(\mathbf{r}) \in \mathbb{C}$  of the **local expansion**  $\mu$  expanded at  $\mathbf{r} = (r, \theta, \phi)$  with radius  $\hat{r}$  and k particles with position  $\mathbf{r}_j = (r_j, \theta_j, \phi_j), j \in \{1, \dots, k\}$  with  $r_j > \hat{r}$  and corresponding charges  $q_j$  is defined as:

$$\mu_{lm}(\mathbf{r}) = \sum_{j=1}^{k} q_j \frac{(l-m)!}{r_j^{l+1}} P_{lm}(\cos \theta_j) e^{im\phi_j}.$$

(2.4)

**Definition 2.7** A complex coefficient  $_{lm}(r) \in \mathbb{C}$  of the **chargeless local expansion** of a point  $r = (r, \theta, \phi)$  is defined as:

$$M_{lm}\left(\boldsymbol{r}\right) = \frac{(l-m)!}{r^{l+1}} P_{lm}\left(\cos\theta\right) e^{im\phi}.$$

Let's assume another point  $\mathbf{a}=(a,\alpha,\beta)$  with  $a<\hat{a}$  inside the sphere (see Figure 2.3b). The potential at this point introduced by the particles outside the sphere represented by the local expansion  $\mu$  is given by:

$$\Phi(P) = \sum_{l=0}^{\infty} \sum_{m=-l}^{l} \mu_{lm}(\mathbf{r}) \frac{a^{l}}{(l+m)!} P_{lm}(\cos \alpha) e^{-im\beta}. \qquad (2.5)$$

In contrast to the multipole expansion, this formula is only valid for evaluation points inside the sphere and the convergence becomes better for points close to the center of the expansion ( $a \ll r$ ). Equation 2.5 and Equation 2.3 show, that the outer sum extends to infinity. For the computation the series must be truncated at a finite  $p \in \mathbb{N}_0$ , called the *multipole order*. This truncation introduces an error which can be controlled. There exist error estimation schemes, but as a general rule of thumb a higher order expansion leads to a smaller error in the computation.

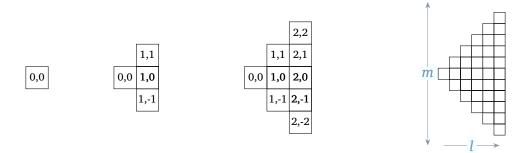

Figure 2.4: Triangular structure of a multipole or local expansion for a monopole, a dipole, a quadrupole and a multipole with multipole order p = 5.

Additionally, it can be observed that, the series uses a double index *l,m*. For the truncated formula this leads to a triangular-like structure of the used multipole expansion coefficients (see Figure 2.4). Furthermore, multipole expansions expanded at the same center can be summed up. In this case, the radius of the new multipole expansion is the larger of both radii. The same summation rule is valid for local expansions at the same center. However, for local expansions the smaller radii is the radius of the new expansion.

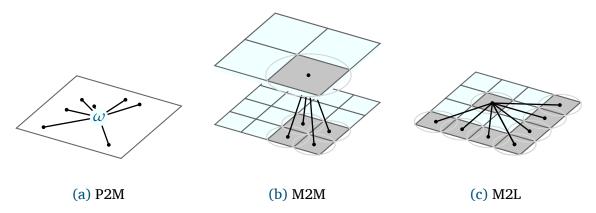

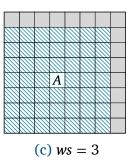

#### 2.3 FMM OPERATORS

Until now, only multipole expansions or local expansions at a certain center can be computed. For the FMM algorithm it is of interest, to compute expansions directly from other expansions without using particles in every step. Operators facilitating such possibilities are shown in the following sections.

#### 2.3.1 MULTIPOLE TO MULTIPOLE

**Definition 2.8** The coefficients  $A_{jk}^{lm}$  of the **multipole to multipole** operator are defined as:

$$A_{jk}^{lm}\left(\boldsymbol{b}\right)=O_{l-j,m-k}\left(\boldsymbol{b}\right)\;.$$

The multipole to multipole (M2M) operator can be used to shift a multipole from one center to another center without expanding particles again. This means, a

Figure 2.5: The multipole to multipole operator allows to shift multipoles around an old center to a new center.

Figure 2.6: The local to local operator allows to shift a local expansion around an old center to a new center inside the sphere.

multipole  $\omega(\mathbf{a})$  expanded at the center  $\mathbf{a}$  can be shifted to a new center  $\mathbf{a} + \mathbf{b}$  (see Figure 2.5). The coefficients of the new multipole  $\omega(\mathbf{a} + \mathbf{b})$  can be computed as follows:

$$\omega_{lm}\left(\boldsymbol{a}+\boldsymbol{b}\right) = \sum_{j=0}^{l} \sum_{k=-l}^{l} \omega_{jk}\left(\boldsymbol{a}\right) A_{jk}^{lm}\left(\boldsymbol{b}\right) . \tag{2.6}$$

This operation does not introduce additional errors itself. The result of applying the operator is the same as if the particles were expanded directly at the new center. As seen in Equation 2.6 the computation of a single coefficient of the multipole expansion  $\omega(\mathbf{a} + \mathbf{b})$  exhibits a complexity of  $\mathcal{O}(p^2)$ . Since the multipole expansion has (p+1)(p+2)/2 complex coefficients, the complexity for the computation of all coefficient is  $\mathcal{O}(p^4)$ .

#### 2.3.2 LOCAL TO LOCAL

**Definition 2.9** The local to local operator  $C_{jk}^{lm}$  is defined as:

$$C_{jk}^{lm}\left(\boldsymbol{b}\right)=O_{j-l,k-m}\left(\boldsymbol{b}\right)$$

.

The local to local (L2L) operator can be used to shift a local expansion from its center to another position inside the expansion sphere (see Figure 2.6). This means, a local expansion  $\mu(\mathbf{r})$  around the center  $\mathbf{r}$  can be shifted to a local expansion  $\mu(\mathbf{r} - \mathbf{b})$ . The coefficients of the new local expansion can be computed using:

$$\mu_{lm}\left(\boldsymbol{r}-\boldsymbol{b}\right) = \sum_{j=l}^{p} \sum_{k=-j}^{j} C_{jk}^{lm}\left(\boldsymbol{b}\right) \mu_{jk}\left(\boldsymbol{r}\right). \tag{2.7}$$

Similar to the M2M operation, the re-expansion of the new local expansion does not require to use the original particles. In contrast to M2M this operator introduces additional errors with respect to the expansion length. As seen in Equation 2.7 the computation of the new local expansion has a complexity of  $\mathcal{O}(p^4)$ .

Figure 2.7: The multipole to local operator translates a multipole expansion at a center a to a local expansion at b-a outside of the sphere of the multipole expansion.

#### 2.3.3 MULTIPOLE TO LOCAL

**Definition 2.10** The multipole to local operator  $B_{ik}^{lm}$  is given by:

$$B_{jk}^{lm}\left(\boldsymbol{b}\right)=M_{j+l,k+m}\left(\boldsymbol{b}\right)$$

.

The multipole to local (M2L) operator can be used to translate a multipole  $\omega(\boldsymbol{a})$  into a local expansion  $\mu(\boldsymbol{b}-\boldsymbol{a})$  (see Figure 2.7). Assuming a multipole expansion for particles in a sphere around the center  $\boldsymbol{a}$ , this multipole represents the impact of the expanded particles on any point outside the sphere. Using the M2L operator a local expansion at a point  $\boldsymbol{b}-\boldsymbol{a}$  outside the sphere around  $\boldsymbol{a}$  can be computed. This local expansion represents the impact of these particles on points inside the sphere of the new local expansion. For the radius of the new local expansions it is required, that the two spheres are disjoint. This translation can be computed without using the particles as proposed in Equation 2.4. The computation can be done using the following formula:

$$\mu_{lm}\left(\boldsymbol{b}-\boldsymbol{a}\right) = \sum_{j=0}^{\infty} \sum_{k=-j}^{j} M_{j+l,k+m}\left(\boldsymbol{b}\right) \omega_{jk}\left(\boldsymbol{a}\right). \tag{2.8}$$

This operator is the only operator introducing an additional operator error since the summation of j is limited to p. Nevertheless, this error can be estimated a priori and controlled [69] within the FMM. Equation 2.8 shows that the application of this operator exhibits  $\mathcal{O}(p^4)$  complexity. Now, all operators required for an FMM have been derived.

#### 2.4 FMM ALGORITHMIC FLOW

The computation of forces and potentials using the FMM is split up into far-field and near-field computations. For  $p \to \infty$  the forces  $F_{FF}$  and potentials  $\Phi_{FF}$  are exact. The forces  $F_{NF}$  and potentials  $\Phi_{NF}$  are always exact since no expansions will be used in the near-field. For the sake of simplicity the error introduced from numerical round-off errors will be ignored. Since the forces and the potentials are cumulative they can be written as:

$$\boldsymbol{F} = \boldsymbol{F}_{NF} + \boldsymbol{F}_{FF}$$

Figure 2.8: An example of a quadtree for subdivision depth zero, one, two and three.

Figure 2.9: The spatial representation of a quadtree. In the first figure the nodes are indexed using a two dimensional index. In the second figure the nodes are indexed with a one dimensional index using a space filling curve. The last figure shows the corresponding graph representation of the quadtree.

and

$$\Phi = \Phi_{NF} + \Phi_{FF}.$$

#### **2.4.1 FMM SETUP**

Spheres are ideal to describe regions of convergence, but unfortunately they are not well suited to fill space without overlapping. For the algorithm, a space filling shape without overlap is required. Therefore, the algorithm used in this work, utilizes cubes. Cubes can be handled easily and are filling space. Other shapes are possible, but complicate the algorithm and convergence requirements. To keep things simple, only cubes will be discussed here. In the following, cubes are also called boxes.

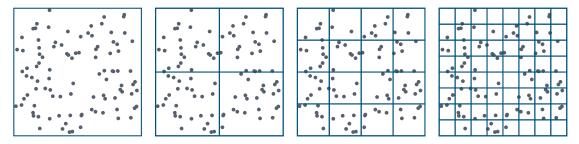

#### SPATIAL SUBDIVISION USING OCTREE

Since all of the introduced operators require a certain spatial subdivision, the FMM has to provide this subdivision as a first step of the algorithm. The FMM uses an octree to divide space. In an octree, every vertex, except the leaf vertices has 8 child vertices. Even though the algorithm works in 3D using octrees, the shown examples are for simplicity only in 2D (see Figure 2.8). The creation of the octree can be setup as follow: It starts with a simulation box which represents the root vertex (see Figure 2.9). This simulation box is then subdivided recursively until a certain maximum depth  $d_{\rm max}$  is reached. This maximum depth must be defined by the user or in this implementation it is set automatically by the error and runtime optimizer. Every level in the tree has  $8^d$  vertices, where d denotes

Figure 2.10: The particle to multipole (P2M) operation expands the particles at the center of a box on the lowest level in the tree in a multipole expansion  $\omega$ . The multipole to multipole (M2M) operation shifts the multipoles from one center of a child box to the center of the parent. This step is repeated for all child boxes of one parent box. The expansions are accumulated at the parent box. The multipole to local (M2L) operation translates multipole expansions to local expansions. Expansions with the same center can be summed up.

the depth of the subdivision. After the last subdivision, the boxes on the lowest level, the leaf vertices are reached. The leaves of the tree are the smallest boxes in the spatial tree each covering  $1/8^d$  of space.

#### **BINNING PARTICLES**

The presented octree has subdivided the simulation space so far. However since the computed properties stem from particles a radix sort [27] is used to bin the particles into the boxes on the lowest level.

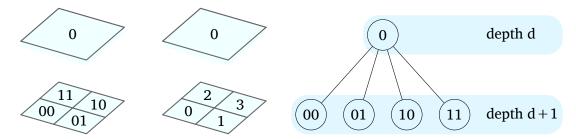

#### 2.4.2 FAR-FIELD COMPUTATION

For the far-field computation the particles need to be expanded into multipole expansions. For this, one multipole for each box on the lowest level will be expanded (see Figure 2.10a) at the center of the box using only particles contained in the box. As discussed before, the expansion of one particle has the computational complexity of  $\mathcal{O}(p^2)$  and is done for all N particles, hence this step has  $\mathcal{O}(Np^2)$  complexity.

After all multipole expansions for all boxes on the lowest level are computed, the multipoles need to be distributed in the tree at higher levels starting from  $d = d_{\text{max}} - 1$  to d = 0. This is achieved by using the aforementioned M2M operator. As shown in Figure 2.10b the multipoles are shifted from the center of the box to the center of the parent box. Since every parent box has eight child boxes, this results in eight shifted multipole expansions for each parent box. These multipoles can be accumulated since they share the same center.

After the M2M step, all boxes in the tree own a multipole expansion representing the particles contained therein. For further computation, the multipoles must be translated into local expansions using the M2L operator. For this operator it

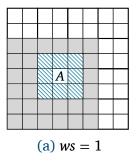

Figure 2.11: Three examples of the M2L interaction set using different well separation criteria in 2D.

is necessary, that the surrounding spheres of the multipole expansion and the local expansion to be generated do not overlap. However, the sphere of direct box neighbors in the octree overlap. The requirement is satisfied by the well separation criteria *ws* and the thereby defined interaction set.

The well separation criteria *ws* is a FMM parameter usually provided by the user. The interaction set is defined as follows:

- 1. Let us consider any box *A* inside the tree.

- 2. Only *ws*-neighbors of *A*'s parent box are considered in the interaction set of the box *A*.

- 3. All child boxes of these boxes under consideration are added to the interaction set.

- 4. Afterwards, all *ws* direct neighbors of *A* itself are excluded from the interaction set again.

This results in 189 interacting boxes for ws = 1. In general, the maximum number of boxes in the interaction set depending on ws is given by:

$$(2(2ws+1))^3 - (2ws+1)^3$$

.

An example of the size of interaction sets can be seen in Figure 2.11.

This means, ws = 1 defines the smallest distance satisfying the non-overlapping criteria. A large well separation criteria increases the distance between the target box and the boxes in the interaction set. After the interaction set is defined, the M2L operator (see Figure 2.10c) is applied for each box in the interaction set and computes a local expansion from all multipole expansions of boxes in the interaction set at the center of box A.

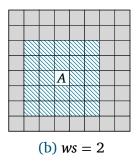

After the M2L step, local expansions representing the potentials and forces of particles in the interaction set are scattered within the full tree. To maintain the linear complexity of the algorithm all local expansions from higher tree levels need to be shifted to their leaf nodes. This is done using the L2L operator. As seen

Figure 2.12: The local to local (L2L) operation shifts the local moments from the center of the parent box towards the center of all child boxes. The local to particle (L2P) operation computes the far-field forces influencing the particles in the box. The particle to particle (P2P) operation computes the near-field interactions using a direct solver.

in Figure 2.12a the operator is used to shift the local expansion from a parent box to all child boxes. This is done starting at the root node on downwards. Since every child box has already a local expansion from the M2L step on its respective level, the shifted local expansion and the local expansion from the M2L step have to be accumulated. After the lowest level in the octree containing the leaf nodes is reached, the resulting local expansion represents all particles in the far-field of this box. These local expansions on the lowest level will be used to compute the far-field forces and potentials affecting the particles using the L2P operator.

**Definition 2.11** The potential  $\Phi_{FF}$  and force  $F_{FF}$  for a particle at position  $\mathbf{a}_k = (a_k, \alpha_k, \beta_k)$  in a box with the corresponding local expansion  $\mu_{lm}(\mathbf{r})$  can be computed using the **local to particle** operator with the following equations:

$$\Phi_{FF}\left(\boldsymbol{a}_{k}\right) \approx \sum_{l=0}^{p} \sum_{m=-l}^{l} \mu_{lm}\left(\boldsymbol{r}\right) \frac{a_{k}^{l}}{\left(l+m\right)!} P_{lm}\left(\cos\alpha_{k}\right) e^{-im\beta_{k}}$$

$$\mathbf{F}_{FF}\left(\mathbf{a}_{k}\right) \approx \sum_{l=0}^{p} \sum_{m=-l}^{l} \mu_{lm}\left(\mathbf{r}\right) \nabla_{\mathbf{a}_{k}} \left[ \frac{a_{k}^{l}}{(l+m)!} P_{lm}\left(\cos \alpha_{k}\right) e^{-im\beta_{k}} \right]$$

As seen in the equations the computation of the force and the potential has a computational complexity of  $\mathcal{O}(p^2)$ . Similar to the P2M step this step is performed for all N particles resulting in a total complexity of  $\mathcal{O}(Np^2)$  for this step.

# 2.4.3 NEAR-FIELD COMPUTATION

The near-field forces and potentials have not been taken into account yet. These are computed from M particles contained in the ws neighboring boxes. The computation itself is only done with this limited set of particles and Equation 2.1 and Equation 2.2, exhibiting a computational complexity of  $\mathcal{O}(M^2)$ . It is done for

*N* particles and thus results in a total complexity of  $\mathcal{O}(M^2N)$ . Since the number of particles can be fixed to *M* for any given system, the total complexity of the FMM is still  $\mathcal{O}(N)$ .

# 2.5 FMSOLVR – IMPLEMENTATION SPECIFICS

Fmsolvr [41] is an FMM implementation specialized for MD simulation developed at the Jülich Supercomputing Centre (JSC). It is part of the SPPEXA [21] project GROMEX [53]. Fmsolvr is implemented using modern C++11 and relies heavily on language and standard library features like vectors or template-meta-programming. In the following, implementation specifics important for this work are presented.

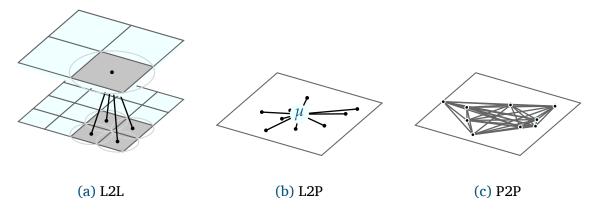

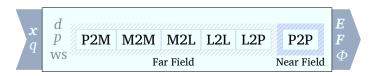

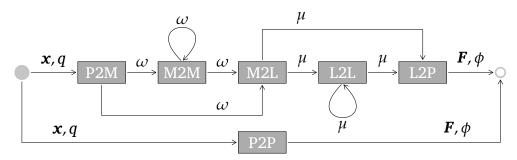

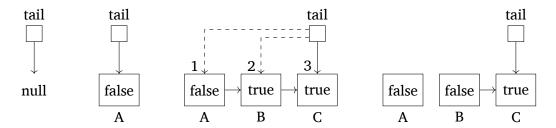

As a brief summary, the complete algorithm flow is shown in Figure 2.13. In the *Fmsolvr* implementation the sequential flow can be described in five distinct passes.

- Pass 1 computes P2M and M2M.

- Pass 2 computes all M2L steps on all levels.

- **Pass 3** includes all L2L operations.

- Pass 4 computes the far-field forces and potentials via the L2P operator.

- Pass 5 computes the near-field forces and potentials via P2P.

The operators (M2M, M2L and L2L) presented before, exhibit a computational complexity of  $\mathcal{O}(p^4)$ . Using an additional rotation operators, it is possible to reduce the complexity to  $\mathcal{O}(p^3)$  [117]. Nevertheless, for the parallelization proposed in this work, it is not important, which kernel implementation is used. This is a decision done by the algorithm developer and is fully independent from the task engine proposed in the following chapters.

The most important data structures for the algorithm are the multipole expansion and the local expansion. As discussed before, these expansions exhibit a triangular structure. Therefore, the data structure used to store the expansion coefficients has a triangular structure as well using generic complex floating point types for the coefficients itself. It can be configured to store the coefficients column or row major.

Furthermore, the multipole expansion and local expansion have an not yet discussed symmetry. The part for  $m \ge 0$  of the coefficients in the triangular

Figure 2.13: The algorithmic flow of the sequential FMM. The parameter d, p and ws are required to set the accuracy of the algorithm.

structure can be used to compute the part for m < 0 of the triangular using the following relation:

$$\begin{split} \omega_{l,-m} &= \left(-1\right)^m \cdot \overline{\omega}_{l,m} \\ \mu_{l,-m} &= \left(-1\right)^m \cdot \overline{\mu}_{l,m} \end{split}$$

This reduces the memory required for the expansions and can be beneficial for data transfer operations. The implementation can be configured at compile time to store the complete coefficient triangular or only the upper half. Besides the expansions, the implementation has custom data structures for particles and their corresponding charges.

# A C++ TASK ENGINE

Shared memory parallelization becomes more and more important in the age of exascale, single core consumer hardware barely exists anymore. Even today's smartphones already feature octa-core processors. To make things worse those processors are heterogeneous which means, that the cores have different capabilities like different clock speeds. For both, smartphone hardware and HPC hardware, the number of cores per node increases rapidly. By extrapolation, 1000 cores per node can easily be reached within the next few years. This development poses new challenges for the software development, especially in HPC.

Available strategies for parallelizing HPC nodes with a moderate number of cores are not necessarily adaptable for thousands of cores. Additionally, the increasing number of cores is not the only development impeding the exploitation of performance on a single node. Things like single instruction, multiple data (SIMD), heterogeneous cores, caches or hierarchical memory need to be considered as well. How could an increase of complexity be coped from a software developer point of view? The concept of abstraction allows to map certain hardware features to the software layer in a generic manner.

To understand this problem from the viewpoint of a software engineer the hardware developments need to be distinguished into two different categories.

**Qualitative** changes in hardware describe the introduction of new features, not present in one hardware generation, but available in the next, like the multicore processors or vectorization (SIMD).

**Quantitative** changes describe the enhancement of existing features like the increasing number of cores in a multi-core processor from only a few to several dozens.

Obviously, it is not possible to foresee qualitative changes and the software cannot adapt to them automatically. However, to some degree it is possible to account for quantitative changes. To cope with these challenges, primarily one thing is required from modern software engineering: software abstractions of hardware features. With abstractions, quantitative changes are already represented in the

software and the achieved performance then only depends on the quality of the implementation.

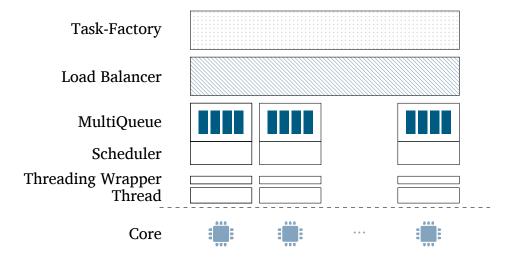

For HPC applications, especially latency-critical ones, strategies that are capable to map performance critical hardware features into software abstractions are vital already today. In this chapter a task engine for HPC is presented. The task engine design especially focuses on latency-critical applications.

The proposed task engine will be introduced for intra-node usage in this chapter. Since the tasking approach in general is a relatively new one in HPC the chapter starts with a discussion of current intra-node parallelization approaches and their limitations.

# 3.1 STATE OF THE ART PARALLELIZATION APPROACHES

Historically, intra-node parallelization was not part of any programming language like C or Fortran, since supercomputers started out with only one core per node and hence no necessity to parallelize on the node. Therefore, language extension or external libraries have been used for the parallelization in the early days of multicore nodes.

For some HPC application on today's hardware it might even be sufficient to solely use inter-node parallelization using the message passing interface (MPI) on the node. Those HPC applications use multiple MPI processes on a single node. Since, inter-node parallelization was required on supercomputers anyway, this is a working solution without additional efforts. Nevertheless, unnecessary additional overhead is introduced by this approach. The overhead stems from an increased memory foot print due to usage of additional MPI processes instead of lightweight threads. Also, data must be explicitly communicated instead of directly accessed in shared memory by threads resulting in unnecessary duplication of data and communication overhead. This approach lacks any usage of shared resources and especially gives up the advantage of using the shared memory.

For only few cores per node, this is not a problem and may be acceptable to ignore the overhead of additional MPI processes. But for future supercomputers it will not be possible to gain performance with such an approach anymore.

# 3.1.1 LOOP-LEVEL PARALLELIZATION

Loop-level parallelism is one of the most common approaches for intra-node parallelization. The main idea of this approach is to obtain parallelism from existing loops (e.g. for-loop). The independent loop iterations are split up and parallelized by assigning subsets of the iterations to different threads.

Without inter-loop data-dependencies or other synchronization requirements and a sufficient number of iterations, this approach scales efficiently for a single loop. However, applications usually encompass more then a single loop and exhibit different inter-loop dependencies. Additionally, due to remaining sequential parts outside the loops the scaling is limited quickly by Amdahl's law [5]. Amdahl's law

gives an upper bound for the achievable speedup S depending on the sequential portion  $r_S$  and parallel portion  $r_D$  of the program executed on P cores as

$$S(P) = \frac{1}{r_s + \frac{r_p}{P}} \quad (r_s + r_p = 1).$$

(3.1)

The limit value of Amdahl's law shows the upper bound of the speedup depending on the sequential parts of the program:

$$\lim_{P \to \infty} S(P) = \frac{1}{r_{\rm s}}.\tag{3.2}$$

Those sequential regions may stem from different sources:

- ➤ Data-dependencies or other synchronization requirements within the algorithm will sequentialize the program.

- **>** Computations outside of parallelized loops will remain sequential.

- ➤ Multiple subsequent parallel loops may utilize thread creation via fork-join which requires synchronization at the end of the loop and thereby introduces sequential parts at the synchronization points.

To give an example, let's assume a program has a sequential portion of 5 % the achievable speedup is limited by 20. On a machine encompassing 40 cores, this would lead to a maximum parallel efficiency of 50 %. This utilization is completely insufficient. The limitation in scaling due to the sequential regions might only be acceptable for low core numbers, but unacceptable for future systems.

Furthermore, loop-level parallelism is limited by the distribution of work. It might be the case, that not all loop iterations encompass the same amount of work. This leads to a load imbalance which has to be actively resolved introducing additional overhead.

The main drawback of loop-level parallelism however stems from the concept itself. The algorithm developer is forced into an artificial loop-based view of his algorithm. Of course it makes sense to parallelize existing loops with this approach. But, it is counter intuitive to introduce new arbitrary loops for the sole purpose of parallelization. It seems to be much more intuitive to think about task-based parallelization, which inherently avoids any predefined structure of parallel execution.

## PRAGMAS AND OPENMP

The de-facto standard to exploit loop-level parallelism is OpenMP [28]. OpenMP is an application program interface (API) for intra-node parallelization. It was first published in 1997 by the OpenMP architecture review board focusing on loop-level parallelism. Starting with version 3.0, OpenMP introduced task-based functionalities. OpenMP natively supports Fortran, C and C++ and implementations are available for almost all common compilers used on today's supercomputers.

OpenMP is based on compiler directives, so called pragmas. Pragmas provide an easy-to-use syntax for parallelization, especially for languages like Fortran and C. Those pragmas are being substituted during the compile process by the OpenMP compiler itself.

Pragmas are language extensions and therefore are not part of the programming language standardization process. Especially from the view point of modern C++, these kind of extensions seem to be outdated. C++ offers various zero-cost abstraction features and parallelization functionality as part of the language standard. Thus, additional compiler directives are not required to handle intra-node parallelization.

Additionally, OpenMP lacks sophisticated scheduling for latency-critical applications which may require the prioritization of a critical path. For example, the FMM exhibits a parallelism bottleneck in the upper tree levels. With OpenMP it is not trivially possible to influence the scheduling in such a way that the prioritization of the critical path can take place.

Furthermore, it is not possible as a user to influence the program flow inside the OpenMP library. Since it is not desirable to change the compiler implementation of OpenMP, it is not possible to change any program specifics that might be required to enable certain optimizations. In contrast, for a C++ library it would be easier to exchange components and adapt for different scenarios.

# 3.1.2 TASK-BASED PARALLELIZATION

Instead of exploiting parallelism solely from loops, task-based parallelization splits up the entire program flow into several units of work and their dependencies. These units of work are called tasks and may be executed in parallel. For a task-based parallelization, dependencies need to be tracked in order to maintain the correct execution of the tasks.

Due to the increasing number of cores and the limitation of loop-level parallelism, task-based parallelization becomes an increasingly popular approach in HPC. There exit several libraries implementing different APIs for task-based parallelization like Argobots [102], Intel TBB [96], StarPU [9], OpenMP Tasks [10] or Wool [39]. Due to the availability of many different task engines, only the most prominent ones are discussed shortly.

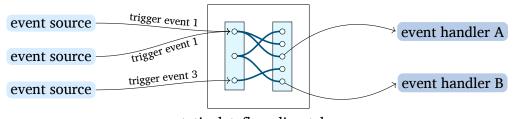

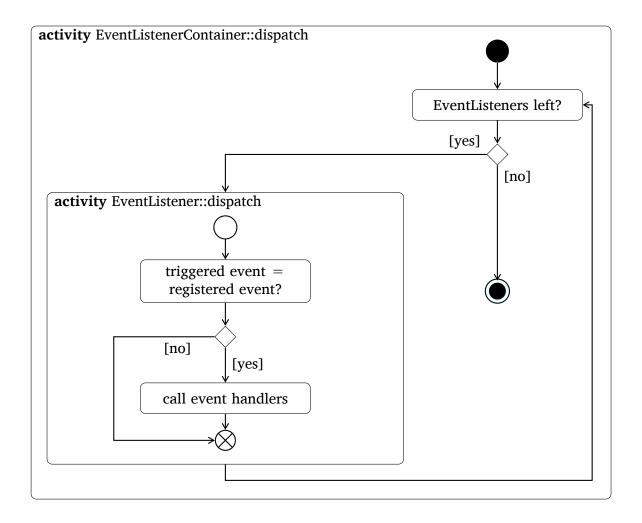

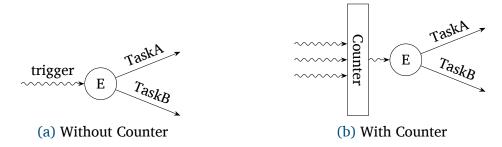

## **ARGOBOTS**