# 30 GHz-voltage controlled oscillator operating at 4 K

Cite as: Rev. Sci. Instrum. **89**, 114701 (2018); https://doi.org/10.1063/1.5038258 Submitted: 02 May 2018 . Accepted: 28 October 2018 . Published Online: 13 November 2018

Arne Hollmann, Daniel Jirovec, Maciej Kucharski, Dietmar Kissinger, Gunter Fischer, and Lars R. Schreiber

## ARTICLES YOU MAY BE INTERESTED IN

A micro-SQUID with dispersive readout for magnetic scanning microscopy Applied Physics Letters 112, 252601 (2018); https://doi.org/10.1063/1.5030489

A reconfigurable cryogenic platform for the classical control of quantum processors Review of Scientific Instruments 88, 045103 (2017); https://doi.org/10.1063/1.4979611

A compact ultrahigh vacuum scanning tunneling microscope with dilution refrigeration Review of Scientific Instruments 89, 113707 (2018); https://doi.org/10.1063/1.5043636

# 30 GHz-voltage controlled oscillator operating at 4 K

Arne Hollmann,<sup>1,a)</sup> Daniel Jirovec,<sup>2</sup> Maciej Kucharski,<sup>3</sup> Dietmar Kissinger,<sup>3</sup> Gunter Fischer,<sup>3</sup> and Lars R. Schreiber<sup>1</sup>

<sup>1</sup>JARA-FIT Institute for Quantum Information, Forschungszentrum Jülich GmbH and RWTH Aachen University, D 52074 Aachen, Germany

<sup>2</sup>Institute of Science and Technology Austria, Am Campus 1, 3400 Klosterneuburg, Austria

<sup>3</sup>IHP, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

(Received 2 May 2018; accepted 28 October 2018; published online 13 November 2018)

Solid-state qubit manipulation and read-out fidelities are reaching fault-tolerance, but quantum error correction requires millions of physical qubits and therefore a scalable quantum computer architecture. To solve signal-line bandwidth and fan-out problems, microwave sources required for qubit manipulation might be embedded close to the qubit chip, typically operating at temperatures below 4 K. Here, we perform the first low temperature measurements of a 130 nm BiCMOS based SiGe voltage controlled oscillator at cryogenic temperature. We determined the frequency and output power dependence on temperature and magnetic field up to 5 T and measured the temperature influence on its noise performance. The device maintains its full functionality from 300 K to 4 K. The carrier frequency at 4 K increases by 3% with respect to the carrier frequency at 300 K, and the output power at 4 K increases by 10 dB relative to the output power at 300 K. The frequency tuning range of approximately 20% remains unchanged between 300 K and 4 K. In an in-plane magnetic field of 5 T, the carrier frequency shifts by only 0.02% compared to the frequency at zero magnetic field. *Published by AIP Publishing*. https://doi.org/10.1063/1.5038258

#### I. INTRODUCTION

The performance of individual solid-state qubits is reaching a level that is sufficient to perform quantum error correction. 1-7 Hitherto, all viable concepts for solid-state quantum processors share the need of cryogenic temperatures below 1 K. Any quantum processor has to be interfaced by classical control hardware to manipulate and read out the qubits. This has to be fast compared to the time scale of decoherence, low-noise and scalable in terms of required lines, size, and power consumption.<sup>8</sup> Fulfilling these requirements for an enormous number of signal lines is a scale-up challenge. Besides multiplexing<sup>9–12</sup> concepts, it might be unavoidable to place part of the control hardware close to the qubits and thus at cryogenic temperature. Power-consuming control hardware might be placed at temperatures between 1 K and 4 K since the available cooling power is less problematic in this range. The qubit chips have to be either thermally isolated, e.g., by superconducting signal lines, or operated at an elevated temperature. 13

Within the last years, there have been several approaches to start developing cryogenic control hardware. The use of cryogenic digital-to-analog converters, <sup>14</sup> analog-to-digital converters, <sup>15</sup> and field-programmable gate arrays <sup>16,17</sup> enables the possibility to process data in close vicinity of the qubit and avoid a high rate data transfer between the quantum processor and room temperature control electronics. First key components for a scalable cryo-CMOS qubit controller based on CMOS technology have been tested. <sup>18</sup> In addition to these semiconductor based approaches, rapid single-flux quantum logic offers a promising low-power alternative,

Depending on the specific qubit realisation, control and read-out schemes require high frequency signals in the 100 MHz range<sup>21</sup> up to tens of gigahertz.<sup>2,4–6,22–24</sup> It might also become beneficial to develop cryogenic high frequency sources which need to be low-noise and tunable in frequency, in order to address different qubits and to enable high-fidelity qubit operation.<sup>8,18</sup>

Here, we test the performance of a commercial heterojunction bipolar transistor (HBT) based voltage controlled oscillator (VCO) at 4 K for the first time. SiGe HBTs are extremely fast compared to CMOS transistors and cryo-compatible due to their high doping profiles. A unity gain cut-off frequency of 800 GHz was observed in an HBT cooled down to 4 K. <sup>25–27</sup> Our VCO showed full functionality from 300 K down to 4 K. We measured that the oscillator's phase noise is mainly dominated by input noise coupling to the system. The magnetic field dependence on the carrier frequency is minimal.

The paper is structured as follows: In Sec. II, we shortly present the device under test and the measurement setup. In Sec. III, the low temperature characterization is presented including phase noise measurements and magnetic field dependence of the output signal.

#### II. DEVICE DESCRIPTION

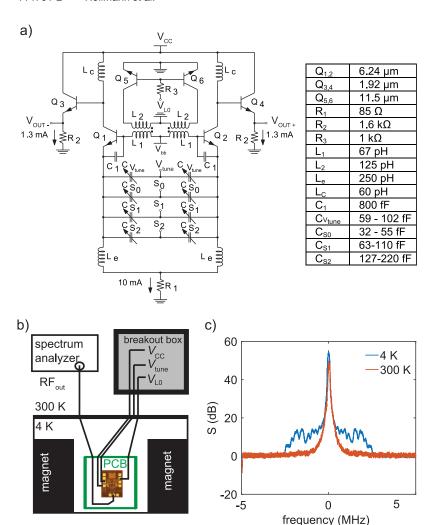

In this work, we tested a wide band, low phase noise LC-voltage controlled oscillator (VCO) at 4 K. The device was fabricated with a SiGe 130 nm BiCMOS technology of Innovations for High Performance Microelectronics (IHP)<sup>28</sup> [Fig. 1(a)].  $Q_1$  and  $Q_2$  are the core transistors used to generate a negative resistance to compensate for the losses of the tank

especially for superconducting qubits, which require control currents. 19,20

a) Email: arne.hollmann@rwth-aachen.de

FIG. 1. (a) Circuit diagram of the dual-band VCO with a table for used resistors R, inductors L, capacitors C, and transistors Q. For the transistors, only the emitter length is listed. The emitter width is 0.12  $\mu$ m for all transistors. The simulated current in each branch is labeled. (b) Schematic of the measurement setup. The VCO is bonded to a PCB and can be measured at 4.2 K and in a magnetic field up to 6 T. Voltages ( $V_{\rm CC}$  for supply,  $V_{\rm tune}$  for tuning the frequency, and  $V_{\rm L0}$  for switching between the frequency bands) are applied from a home built low-noise DC source operating at room temperature. (c) Average power spectrum of 20 measurements taken at room temperature (red) and at 4 K (blue) as a function of frequency offset from the carrier frequency. The peak position shifts from 29.81 GHz at 300 K to 30.76 GHz at 4 K.

circuit. The signal must be buffered before driving the external load in order to not influence the oscillator's core. This is accomplished by taking the signal not at the emitters but the collectors of  $Q_1$  and  $Q_2$ . Emitter follower stages composed of  $Q_3$  and  $Q_4$  further increase the isolation and drive a cascade amplifier used to provide sufficient power at 50  $\Omega$  external load. The VCO can be tuned continuously from 29.6 GHz to 32.4 GHz (at room temperature) by a voltage input signal. The frequency band can be switched to a second band ranging from 32.0 GHz to 35.5 GHz. Thus, the total frequency tuning range is 20%. The oscillator has three varactor banks  $(S_0-S_2)$ for coarse digital frequency control and one varactor for fine tuning (by the input voltage  $V_{\text{tune}}$ ). The change between the two frequency bands is realized by switch-coupled inductors  $L_1$  and  $L_2$ . The switch is implemented with  $Q_5$  and  $Q_6$  operating either in saturation or cut-off region depending on the  $L_0$  value. The quality factor of the varactors is enhanced by the inductors  $L_{\rm c}$ . The inductors  $L_{\rm C}$  are used to provide a load for the fundamental signal.<sup>28</sup> The circuit occupies an area of 0.1 mm<sup>2</sup>. For operation, a supply voltage of  $V_{CC} = 3$  V is used. To switch between the two frequency bands, a voltage of  $V_{L0} = 3$  V has to be applied to the  $L_0$  pin. The frequency is tuned by varying  $V_{\text{tune}}$  between 0 V and 3 V [Fig. 1(b)]. The simulated output power of the device at  $V_{\rm CC}$  = 3 V is 75 mW where 37 mW are consumed by the core oscillator and the emitter follower stages.

The VCO is bonded to a high frequency printed circuit board (PCB), which provides control and supply voltages and transfers the VCO output signal. The PCB with the VCO is measured in a 4 K setup consisting of a dipstick and a helium vessel with a 6 T magnet. An in-plane magnetic field can be applied to the device under test. The supply voltages are applied by using a home built DC source with a white noise floor of  $20 \text{ nV/}\sqrt{\text{Hz}}$ . The output signal of the VCO is measured by using a 40 GHz spectrum analyzer (Agilent E4446A) [Fig. 1(b)].

### III. ELECTRICAL CHARACTERIZATION

Figure 1(c) shows a spectrum averaged over 20 single traces taken at room temperature (red curve) and at 4 K (blue curve). The power is normalized to the noise floor. At 300 K, we measure an output power of –31.5 dBm. The spectrum has a sharp peak with a full width at half maximum of approximately 200 kHz and centre frequency of 29.81 GHz, if  $V_{\rm tune}$  is set to 0 V. For comparison, at 4 K, the carrier frequency is shifted by almost 1 GHz to 30.76 GHz. A two times larger temperature impact on the frequency was observed for a CMOS oscillator in Ref. 18. The peak width is similar to the room temperature measurement; however, at a low temperature, next to the main peak, we measure small oscillations with an abrupt edge at ±2.5 MHz distance from the centre peak. The power of these

unintentional oscillations is 45 dB smaller than the maximum of the signal. This effect could be attributed to small, slow output fluctuations on the sinusoidal output signal. An orders of magnitude smaller effect is also present at room temperature, which is barely visible in Fig. 1(b). By assuming a square-like flickering modulation on the output signal, we estimated that the modulation amplitude is by a factor of 100 smaller than the amplitude of the output signal.

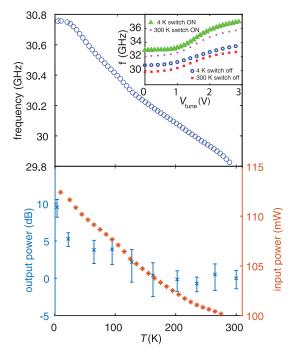

To further investigate the effect of temperature, we measured the power spectrum during cool down of the device. The carrier frequency shifts almost linearly between 300 K and 20 K. Below 20 K, the carrier frequency remains constant at around 30.76 GHz (Fig. 2). Both at room temperature and at 4 K, the frequency can be varied by almost 3 GHz when applying a tuning voltage V<sub>tune</sub> between 0 V and 3 V to the varactor bank (inset, Fig. 2, top). An additional frequency shift of 3 GHz can be induced by applying a voltage to the switchcoupled inductors. In total, a frequency window of almost 6 GHz is accessible. We conclude that both the varactor and the coupled inductor operate down to 4 K. Presumably, the frequency increases due to a reduction in the capacitance of the varactor's depletion region and parasitic capacitances. Beside the frequency shift during cool-down, the input power of the VCO increases by a factor of 1.28 when reducing the temperature to 4 K. The output power is increased by a much larger factor of 10 (Fig. 2); thus, the VCO becomes more power efficient at 4 K. We assign this effect to an increase in the electron mobility of the SiGe devices.

The oscillator's phase noise is an important figure of merit. For semiconducting oscillators, one typically distinguishes

FIG. 2. Top: Carrier frequency versus temperature measured during cool down. Inset: Carrier frequency as a function of  $V_{\rm tune}$  for the low frequency band, i.e.,  $V_{L0} = 0$  V at 300 K (red star) and 4 K (blue circle), respectively, and second frequency band, i.e.,  $V_{L0} = 3$  V at 300 K (purple dot) and 4 K (green triangle), respectively. Bottom: Output (blue) and input (orange) power of the VCO as a function of temperature. The output powers are determined by fitting the spectra to a Lorentzian keeping its width constant.

device noise and modulation noise. Device noise is contributed by the device itself consisting of 1/f-noise only relevant at low frequencies, as well as shot noise and thermal noise which are dominant for high frequency applications. Additionally, the output signal is affected by noise of several DC voltages such as the supply voltage  $V_{\rm CC}$  and the tuning voltage  $V_{\rm tune}$  referred to as modulation noise.  $^{29,30}$  Here, we measured the phase noise of the output signal as a function of temperature, which should ideally decrease for lower temperature values.

The phase noise  $S_{\omega}$  is extracted from the power spectrum of the VCO output signal. In the following, we will refer to the single-side band power  $S_{\rm SSB}$  in 1 Hz bandwidth, normed to the power of the peak as phase noise,

$$\mathcal{L}(\omega)(\mathrm{dBc/Hz}) = \frac{S_{\mathrm{SSB}}(\omega, \Delta f = 1 \,\mathrm{Hz})}{\int_{\mathit{peak}} \mathrm{d}\omega \, S_{\mathrm{SSB}}}.$$

(1)

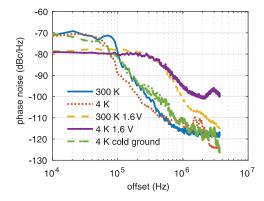

To determine the phase noise, we measured the spectrum with an Agilent E4446A power spectrum analyzer. The phase noise is extracted from the power spectrum using Eq. (1). The resulting phase noise as a function of frequency offset from the carrier frequency is depicted in Fig. 3. First, we compare the measurements, for which  $V_{\text{tune}}$  was connected to the roomtemperature voltage source set to 0 V. The blue solid line reveals the phase noise at room temperature dropping from -80 dBc/Hz at 100 kHz to approximately -115 dBc/Hz at 1 MHz. The overall phase noise is small and comparable to other low noise VCOs. 18,31-33 We now compare the result to a similar measurement taken at 4 K (red dotted line). At 100 kHz, the phase noise is slightly lower (-90 dBc/Hz) and at 1 MHz slightly higher  $(-110 \, dBc/Hz)$  with respect to the room temperature measurement. For frequencies in the MHz-range, the oscillations also noticed in Fig. 1 become visible.

We further investigate how the noise from the voltage source influences the performance by repeating the measurement at 4 K with the  $V_{\rm tune}$ -pin of the oscillator directly wire bonded to the cold finger inside the fridge. This configuration is referred to as cold ground. The phase noise behavior remains similar compared to the previous measurements, for which the  $V_{\rm tune}$ -pin was set to room-temperature ground of the voltage source (Fig. 3). Thus, the phase noise is not significantly

FIG. 3. Phase noise versus offset from the carrier frequency at 300 K and 4 K where the  $V_{\rm tune}$ -pin was set to lab ground (blue and red, respectively) and where it was bonded to cold ground (green). No large variation can be detected, implying that the VCO is limited by thermal noise. Setting  $V_{\rm tune}$  to 1.6 V shows an increased phase noise (yellow and purple).

affected by external noise at  $V_{\rm tune}=0$  V. Notably, no significant effect of temperature on phase noise is observed. The phase noise exhibits approximately a  $1/f^3$  dependence expected from simulations. We attribute this prominent  $1/f^3$  dependence of the phase noise to the noise of the supply voltage up-converted to phase noise. This noise masks the temperature noise contribution. If applying  $V_{\rm tune}=1.6$  V, the phase noise increases consistently, both at room temperature and 4 K (Fig. 3). In this case, the phase noise is dominated by the input noise of the tuning voltage  $V_{\rm tune}$  and  $V_{\rm CC}$  (modulation noise) since the device becomes more sensitive to input noise at  $V_{\rm tune}=1.6$  V as we will further discuss below. A similar 4 K measurement with a CMOS oscillator showed a decrease in phase noise for offset frequencies above 20 MHz but an increased  $1/f^3$  phase noise corner frequency.

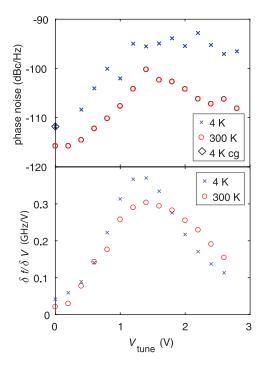

To further analyze the sensitivity of phase noise to  $V_{\rm tune}$ , we measured the phase noise for different tuning voltages. A low-noise, home built DC source was connected to the  $V_{\rm tune}$ -pin and the voltage was varied over the full range from 0 V to 3 V. The resulting phase noise at a constant offset of 1 MHz from the carrier frequency is depicted in Fig. 4. Similar to Fig. 3 at 0 V, the phase noise is insensitive to noise of  $V_{\rm tune}$ . Applying 0 V input voltage with the DC source or grounding the  $V_{\rm tune}$  pin does not change the phase noise (black dot in Fig. 4). Increasing the tuning voltage up to 1.4 V leads to an increase in noise of 15 dB. For  $V_{\rm tune} \geq 1.4$  V, the noise decreases again at 300 K; however, it stays almost constant at 4 K. We compared these measurements with the derivative of the carrier frequency of the output signal with respect to  $V_{\rm tune}$

FIG. 4. Top: Phase noise at a constant offset of 1 MHz versus  $V_{\rm tune}$  at 300 K and 4 K. The phase noise strongly increases for increasing  $V_{\rm tune}$  up to 1.4 V, reduces for  $V_{\rm tune} \geq 1.4$  V at 300 K, and stays almost constant at 4 K. Bottom: For comparison, the derivative of the frequency tuneability in Fig. 2(b) inset with respect to  $V_{\rm tune}$  is displayed for the two operation temperatures. The sensitivity of the carrier frequency with respect to  $V_{\rm tune}$  matches the phase noise amplitude plotted in the upper panel.

from the measurement data in Fig. 2(b) (inset). As depicted in Fig. 4, the qualitative behavior of the curves is similar. Within the region at which the carrier frequency is most sensitive to  $V_{\text{tune}}$  ( $V_{\text{tune}} = 1.6 \text{ V}$ ), i.e., the VCO gain is maximal, the VCO is also most sensitive to the noise of the voltage source. At  $V_{\text{tune}} = 1.4 \text{ V}$ , the frequency sensitivity is approximately 15 times larger than at  $V_{\text{tune}} = 0 \text{ V}$  (Fig. 4). Thus, we expect an increase in phase noise from  $V_{\text{tune}} = 0.0 \text{ V}$  to 1.4 V of approximately 12 dB, which is close to the measured phase noise increase of 15 dB (see Fig. 3). The phase noise of an oscillator used for qubit control affects the gate fidelity. The overall effect of control electronics on this fidelity depends on the type of qubit and details of the control methods. For example, to achieve an x, y and identity gate fidelity of F = 99.9% for a resonantly driven single spin qubit at 1 MHz Rabi frequency, the oscillator's phase noise has to be below -106 dBc/Hz (at 1 MHz from the carrier).<sup>8</sup> For low tuning voltages, the phase noise of our device is below this value (Fig. 3).

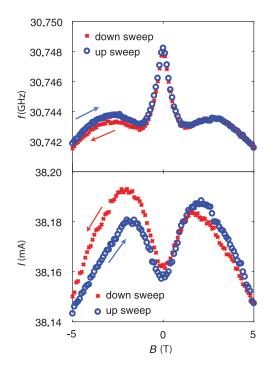

Some qubits do not only require low temperature but also require a magnetic field. Especially, magnetic fields in the order of 1 T are required for encoding single electron spin qubits.  $^{13,34,35}$  Thus, the effect of magnetic field on the performance of electronics in close proximity to the qubit-chip has to be considered. Therefore, we studied the effect of a magnetic field B on the carrier frequency of the VCO. The magnetic field was applied in the plane of the VCO and swept from -5 T to 5 T and back to -5 T. At 5 T and -5 T, the carrier frequency is reduced by 6 MHz compared to zero magnetic field (Fig. 5). The magnetic field dependence of the carrier frequency reveals a saddle point at around  $\pm 2$  T. Furthermore, the up-sweep and down-sweep do not coincide exactly. A tiny hysteresis is visible in the order of  $10^{-5}$ . The current consumption reveals two

FIG. 5. Top: Carrier frequency as a function of the applied magnetic field. The magnetic field is first swept up from -5 T to 5 T and then down from 5 T to -5 T. Bottom: Current consumption for the same measurement.

side peaks at  $\pm 2$  V (Fig. 5), but the overall change is in the order of  $10^{-4}$ . The magnetic field dependence on the frequency is a tiny fraction of the output frequency. This does not constitute a severe limitation since usually the magnetic field is held constant in spin qubit experiments but has to be taken into account for high fidelity spin qubits in, e.g.,  $^{28}$ Si<sup>4</sup>.

## **IV. CONCLUSION**

In this work, we presented the first low-temperature measurements of a high frequency (30 GHz) VCO based on HBT technology. The device showed complete functionality, even at 4 K. By varying the control voltage  $V_{\text{tune}}$  and using the base band switch, a frequency band of 6 GHz is accessible. Compared to room temperature, the VCO becomes more power efficient and the carrier frequency shifts by almost 1 GHz at 4 K. The phase noise of the oscillator has been analyzed at room temperature and at 4 K. The noise is dominated by modulation noise, e.g., the noise on the tuning input, and no significant effect of the temperature on the noise was observed. Notably, power consumption in the order of 100 mW restricts the use of this device to the 4 K stage of a dilution refrigerator. For spin qubit manipulation, microwaves can be applied to the high-impedance metal gates of electrostatically defined quantum dots. Thus, a high impedance output of the oscillator is sufficient. Omitting the buffer for the 50  $\Omega$  matched output would already reduce the power by approximately 10 mW. The power consumption can be further reduced by lowering the supply voltage  $V_{\rm CC}$ . The oscillator can still be operated at 2.3 V where we simulated a power consumption of 10 mW. Much further reduction of the power consumption requires the development of dedicated low-power cryo-devices and circuit redesign. The SiGe-HBT BiCMOS technology is a promising platform to start the development of fast cryogenic control hardware for scalable quantum computing.

#### **ACKNOWLEDGMENTS**

We would like to thank H. Bluhm for useful discussions and F. Haupt for proof reading this manuscript. This project is sponsored by the Federal Ministry of Education and Research under Contract No. FKZ: 13N14778. Project Si-QuBus has received funding from the QuantERA ERANET Cofund in Quantum Technologies implemented within the European Union's Horizon 2020 Programme.

- <sup>1</sup>M. Veldhorst, J. C. C. Hwang, C. H. Yang, A. W. Leenstra, B. de Ronde, J. P. Dehollain, J. T. Muhonen, F. E. Hudson, K. M. Itoh, A. Morello, and A. S. Dzurak, Nat. Nanotechnol. 9, 981 (2014).

- <sup>2</sup>T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, Nature 555, 633 (2017).

- <sup>3</sup>J. T. Muhonen, A. Laucht, S. Simmons, J. P. Dehollain, R. Kalra, F. E. Hudson, S. Freer, K. M. Itoh, D. N. Jamieson, J. C. McCallum, A. S. Dzurak, and A. Morello, J. Phys.: Condens. Matter 27, 154205 (2015).

- <sup>4</sup>J. Yoneda, K. Takeda, T. Otsuka, T. Nakajima, M. R. Delbecq, G. Allison, T. Honda, T. Kodera, S. Oda, Y. Hoshi, N. Usami, K. M. Itoh, and S. Tarucha, Nat. Nanotechnol. **13**, 102 (2017).

- <sup>5</sup>R. Barends, J. Kelly, A. Megrant, A. Veitia, D. Sank, E. Jeffrey, T. C. White, J. Mutus, A. G. Fowler, B. Campbell, Y. Chen, Z. Chen, B. Chiaro, A. Dunsworth, C. Neill, P. O'Malley, P. Roushan, A. Vainsencher,

- J. Wenner, A. N. Korotkov, A. N. Cleland, and J. M. Martinis, Nature 508, 500 (2014).

- <sup>6</sup>J. Kelly, R. Barends, A. G. Fowler, A. Megrant, E. Jeffrey, T. C. White, D. Sank, J. Y. Mutus, B. Campbell, Y. Chen, Z. Chen, B. Chiaro, A. Dunsworth, I. C. Hoi, C. Neill, P. J. O'Malley, C. Quintana, P. Roushan, A. Vainsencher, J. Wenner, A. N. Cleland, and J. M. Martinis, Nature 519, 66 (2015)

- <sup>7</sup>T. E. O'Brien, B. Tarasinski, and L. DiCarlo, npj Quantum Inf. **3**, 39 (2017).

- <sup>8</sup>J. P. G. van Dijk, E. Kawakami, R. N. Schouten, M. Veldhorst, L. M. K. Vandersypen, M. Babaie, E. Charbon, and F. Sebastiano, e-print arXiv:1803.06176 (2018).

- <sup>9</sup>R. K. Puddy, L. W. Smith, H. Al-Taie, C. H. Chong, I. Farrer, J. P. Griffiths, D. A. Ritchie, M. J. Kelly, M. Pepper, and C. G. Smith, Appl. Phys. Lett. 107, 143501 (2015).

- <sup>10</sup>J. M. Hornibrook, J. I. Colless, I. D. Conway Lamb, S. J. Pauka, H. Lu, A. C. Gossard, J. D. Watson, G. C. Gardner, S. Fallahi, M. J. Manfra, and D. J. Reilly, Phys. Rev. Appl. 3, 024010 (2015).

- <sup>11</sup>H. Al-Taie, L. W. Smith, A. A. J. Lesage, P. See, J. P. Griffiths, H. E. Beere, G. A. C. Jones, D. A. Ritchie, M. J. Kelly, and C. G. Smith, J. Appl. Phys. 118, 075703 (2015).

- <sup>12</sup> M. Veldhorst, H. G. J. Eenink, C. H. Yang, and A. S. Dzurak, Nat. Commun. 8, 1766 (2017).

- <sup>13</sup>L. M. K. Vandersypen, H. Bluhm, J. S. Clarke, A. S. Dzurak, R. Ishihara, A. Morello, D. J. Reilly, L. R. Schreiber, and M. Veldhorst, npj Quantum Inf. 3, 34 (2017).

- <sup>14</sup>M. T. Rahman and T. Lehmann, in *Proceedings of Conference on International Midwest Symposium on Circuits and Systems* (IEEE, 2014), Vol. 57, p. 9.

- <sup>15</sup>B. Okcan, P. Merken, G. Gielen, and C. Van Hoof, Rev. Sci. Instrum. 81, 024702 (2010).

- <sup>16</sup>H. Homulle, S. Visser, B. Patra, G. Ferrari, E. Prati, F. Sebastiano, and E. Charbon, Rev. Sci. Instrum. 88, 045103 (2017).

- <sup>17</sup>I. D. Conway Lamb, J. I. Colless, J. M. Hornibrook, S. J. Pauka, S. J. Waddy, M. K. Frechtling, and D. J. Reilly, Rev. Sci. Instrum. 87, 014701 (2016).

- <sup>18</sup>B. Patra, R. M. Incandela, J. P. G. van Dijk, H. A. R. Homulle, L. Song, M. Shahmohammadi, R. B. Staszewski, A. Vladimirescu, M. Babaie, F. Sebastiano, and E. Charbon, IEEE J. Solid-State Circuits 53, 1 (2018).

- <sup>19</sup>K. K. Likharev and V. K. Semenov, IEEE Trans. Appl. Supercond. 1, 3 (1991).

- <sup>20</sup>R. McDermott, M. G. Vavilov, B. L. T. Plourde, F. K. Wilhelm, P. J. Liebermann, O. A. Mukhanov, and T. A. Ohki, Quantum Sci. Technol. 3, 024004 (2018).

- <sup>21</sup>P. Cerfontaine, T. Botzem, D. P. Divincenzo, and H. Bluhm, Phys. Rev. Lett. 113, 150501 (2014).

- <sup>22</sup>L. R. Schreiber, F. R. Braakman, T. Meunier, V. Calado, J. Danon, J. M. Taylor, W. Wegscheider, and L. M. K. Vandersypen, Nat. Commun. 2, 556 (2011).

- <sup>23</sup> D. Zajac, A. Sigillito, M. Russ, F. Borjans, J. Taylor, G. Burkard, and J. Petta, Science 26, 439 (2017).

- <sup>24</sup>J. Yoneda, T. Otsuka, T. Nakajima, T. Takakura, T. Obata, M. Pioro-Ladrière, H. Lu, C. Palmstrøm, A. C. Gossard, and S. Tarucha, Phys. Rev. Lett. 113, 267601 (2014).

- <sup>25</sup>J. D. Cressler, Proc. IEEE **93**, 1559 (2005).

- <sup>26</sup>J. D. Cressler, IEEE Trans. Device Mater. Rel. **10**, 437 (2010).

- <sup>27</sup>P. S. Chakraborty, A. S. Cardoso, B. R. Wier, A. P. Omprakash, J. D. Cressler, M. Kaynak, and B. Tillack, IEEE Electron Device Lett. 35, 151 (2014).

- <sup>28</sup>M. Kucharski, F. Herzel, H. J. Ng, and D. Kissinger, in *Proceedings of the 2016 11th European Microwave Integrated Circuit Conference* (IEEE, 2016), Vol. 2, p. 201.

- <sup>29</sup>F. Herzel and B. Razavi, IEEE Trans. Circuits Syst. II **46**, 56 (1999).

- <sup>30</sup>J. B. Frank Herzel and W. Winkler, Proc. SPIE **5473**, 16 (2004).

- <sup>31</sup>J. C. Chien and L. H. Lu, IEEE J. Solid-State Circuits **42**, 1942 (2007).

- <sup>32</sup>Y.-J. E. Chen, W.-M. L. Kuo, S. Member, Z. Jin, J. Lee, Y. V. Tretiakov, J. D. Cressler, and A. An, IEEE Trans. Microw. Theory Techn. 53, 1672 (2005).

- <sup>33</sup>N. Chen, S. Diao, L. Huang, X. Bai, and F. Lin, J. Semicond. **34**, 095009 (2013).

- <sup>34</sup>D. Loss and D. P. DiVincenzo, Phys. Rev. **57**, 12 (1998).

- <sup>35</sup>E. Kawakami, P. Scarlino, D. R. Ward, F. R. Braakman, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, Nat. Nanotechnol. 9, 666 (2014).