# Experimental Demonstration of Memristor-Aided Logic (MAGIC) Using Valence Change Memory (VCM)

Barak Hoffer<sup>®</sup>, Vikas Rana, Stephan Menzel<sup>®</sup>, *Member, IEEE*, Rainer Waser<sup>®</sup>, *Member, IEEE*, and Shahar Kvatinsky<sup>®</sup>, *Senior Member, IEEE*

Abstract — Memristor-aided logic (MAGIC) is a technique for performing in-memory computing using memristive devices. The design of a MAGIC NOR gate has been described in detail, and it serves as the basic building block for several processing-in-memory architectures. However, the input stability of the MAGIC NOR gate forces a limitation on the threshold voltages: the magnitude of the set voltage must be higher than the magnitude of the reset voltage. Unfortunately, many of the current leading resistive switching technologies, particularly, valence change memory (VCM), have the opposite ratio between the threshold voltages. In this article, we experimentally demonstrate the undesirable effects of input instability. Furthermore, we introduce three new MAGIC gates for devices with low set-to-reset voltage ratios and experimentally demonstrate their robust operation using Pt/Ta<sub>2</sub>O<sub>5</sub>/W/Pt devices. The three gates, combined with constant values, are functionally complete and are demonstrated as building blocks for in-memory logic on VCM devices.

Index Terms—Logic-in-memory, memristor, memristoraided logic (MAGIC), processing-in-memory (PIM), valence change memory (VCM).

# I. INTRODUCTION

EMRISTIVE devices have attracted much attention, in the context of both future nonvolatile memories, as well as computation-in-memory [1]–[4]. For binary storage and computing using memristive devices, the logical states are

Manuscript received April 22, 2020; revised June 4, 2020; accepted June 6, 2020. Date of publication June 25, 2020; date of current version July 23, 2020. This work was supported in part by the European Research Council (ERC) through the European Union's Horizon 2020 Research and Innovation Programme under Grant 757259 and in part by the Israel Science Foundation under Grant 1514/17. The review of this article was arranged by Editor Y. Chauhan. (Corresponding author: Barak Hoffer.)

Barak Hoffer and Shahar Kvatinsky are with the Andrew and Erna Viterbi Faculty of Electrical Engineering, Technion-Israel Institute of Technology, Haifa 3200003, Israel (e-mail: barakhoffer@campus.technion.ac.il; shahar@ee.technion.ac.il).

Vikas Rana is with the Peter-Grünberg-Institut 10 & JARA-FIT, Forschungszentrum Jülich GmbH, 52425 Jülich, Germany.

Stephan Menzel is with the Peter-Grünberg-Institut 7 & JARA-FIT, Forschungszentrum Jülich GmbH, 52425 Jülich, Germany.

Rainer Waser is with the Institut für Werkstoffe der Elektrotechnik 2 & JARA-FIT, RWTH Aachen University, 52070 Aachen, Germany, and also with the Peter-Grünberg-Institut 7 & JARA-FIT, Forschungszentrum Jülich GmbH, 52425 Jülich, Germany.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2020.3001247

represented by two resistive states. Generally, the high resistive state  $R_{\rm OFF}$  is considered as logical '0' ("OFF") and the low resistive state  $R_{\rm ON}$  as logical '1' ("ON"). To switch between the states, a voltage pulse is applied across the device;  $V_{\rm SET}$  is used to switch from OFF to ON and  $V_{\rm RESET}$  from ON to OFF. In bipolar devices, the polarity of these voltages is opposite. In this article, we refer to  $V_{\rm SET}$  as a negative voltage and  $V_{\rm RESET}$  as a positive one.

Stateful logic [4] is a computation-in-memory technique, in which the data stored in the memristors, represented by their logical state, is used as input and the result is written to an output memristor as a logical state. Examples of such logic families include material implication (IMPLY) [5] and memristor-aided logic (MAGIC) [6], [7]. In the MAGIC family, unlike IMPLY logic, memristors for the input and output are separated, the output is written to a dedicated memristor, and there are no additional devices in the periphery. The MAGIC architecture is therefore, preferable over IMPLY logic in terms of area, latency, and energy [8]. Furthermore, the crossbar-compatible MAGIC NOR gate is considered a promising building block for processing-in-memory (PIM) architectures [9]–[12].

To the best of our knowledge, the MAGIC NOR gate, as opposed to the IMPLY logic gate [13]–[15], has only been experimentally demonstrated on exotic polymer-resistive devices [16]–[18]. Yet, these devices are not compatible with complementary metal–oxide–semiconductor (CMOS) processes.

Valence change memory (VCM) [19] is a category of CMOS-compatible bipolar-resistive switching devices, which use transition metal oxides as the insulating material, e.g., TiO<sub>2</sub> [20], HfO<sub>2</sub> [21], [22], or Ta<sub>2</sub>O<sub>5</sub> [23]–[26], combined with asymmetric electrodes. Specifically, Ta<sub>2</sub>O<sub>5</sub>-based devices are considered as a promising resistive technology because of their fast switching speed [23], relatively high endurance [24], and long retention properties [25]. However, to prevent overwrite of inputs in the MAGIC NOR gate, the magnitude of the set voltage should be at least twice the magnitude of the reset voltage. Yet, many VCM devices exhibit low set-to-reset voltage ratios.

In this article, we describe and experimentally demonstrate the obstacles in executing MAGIC NOR using VCM. Then, we propose adding three new logic gates to the MAGIC family. We describe the design methodology, and explain how these gates ensure input stability for devices with low set-to-reset

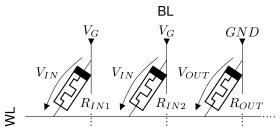

Fig. 1. Schematic of a two-input MAGIC gate within a crossbar. According to the passive sign convention,  $V_{\rm OUT}$  has the same sign as  $V_{\rm G}$ , while  $V_{\rm IN}$  has the opposite sign.

voltage ratios. Finally, we experimentally demonstrate, using  $Ta_2O_5$ -based memristive devices, that the new gates produce correct and reproducible results. Additionally, we demonstrate more complex logic operations, such as half adders, using the proposed gates as building blocks.

#### II. MEMRISTOR-AIDED LOGIC

MAGIC [6] is a family of stateful memristive logic gates. A two-input MAGIC gate consists of two input memristors (IN1, IN2), connected in parallel, and an additional memristor (OUT) for the output. A schematic of a two-input gate is shown in Fig. 1. The operation of a MAGIC gate consists of two sequential steps. The first step initializes the output memristor to a known logical state. In the second step, a voltage  $V_G$  is applied across the logic gate. While applying  $V_G$ , the voltage across the output memristor depends on the logical states of the input and output memristors (i.e., a voltage divider). For specific input combinations, the voltage across the output memristor is sufficiently high to change its logical state, whereas, for other input combinations, the voltage across the output is relatively low and its logical state remains at the initialized state.

# A. MAGIC NOR

Since NOR is functionally complete and MAGIC NOR can be easily mapped to a crossbar array, the MAGIC NOR gate was originally proposed as the basic building block for implementing in-memory logic in memristive memory processing units (mMPU) [27]. The initial execution step includes setting the output memristor to  $R_{\rm ON}$ . Then, evaluation is achieved by grounding the OUT bitline and applying a voltage pulse  $V_{\rm G}$  at the bitlines of the input memristors (for simplicity, the wire resistance is neglected in the following calculations).

In the evaluation step, the voltage on the output cell is the result of a voltage divider between the input cells and the output cell

$$V_{\rm OUT}({\rm IN1,IN2}) = V_{\rm G} \cdot \frac{R_{\rm ON}}{R_{\rm IN1}||R_{\rm IN2} + R_{\rm ON}}.$$

(1)

Assume  $R_{\rm OFF} \gg R_{\rm ON}$  (at least one order of magnitude), to switch the output in all cases, except for the (IN1=IN2='0') case,  $V_{\rm G}$  must be greater or equal to  $2|V_{\rm RESET}|$ . Table I lists the voltages across the output for each input combination, when selecting  $V_{\rm G}=2|V_{\rm RESET}|$ . This dictates the functionality of a NOR gate.

#### B. Input Stability

Another constraint of the gate is input stability. Table I lists the voltages across the input and output memristors for each

TABLE I

INPUT AND OUTPUT VOLTAGES FOR THE MAGIC NOR GATE

| State                  |                        | Voltage                   |                          |

|------------------------|------------------------|---------------------------|--------------------------|

| $R_{IN1}$              | $R_{IN2}$              | $V_{IN}$                  | $V_{OUT}$                |

| R <sub>OFF</sub> ('0') | R <sub>OFF</sub> ('0') | $-2 V_{RESET} $           | 0V                       |

| R <sub>OFF</sub> ('0') | R <sub>ON</sub> ('1')  | $- V_{RESET} $            | $ V_{RESET} $            |

| $R_{ON}$ ('1')         | R <sub>OFF</sub> ('0') | $- V_{RESET} $            | $ V_{RESET} $            |

| $R_{ON}$ ('1')         | R <sub>ON</sub> ('1')  | $-\frac{2}{3} V_{RESET} $ | $\frac{4}{3} V_{RESET} $ |

TABLE II VCM DEVICES COMPARISON

| Device                                                      | $\left rac{ m V_{SET}}{ m V_{RESET}} ight $ | $rac{ m R_{OFF}}{ m R_{ON}}$ | Reference |

|-------------------------------------------------------------|----------------------------------------------|-------------------------------|-----------|

| Pt/Ti/TiO <sub>2</sub> /TiN                                 | 0.6                                          | 10                            | [20]      |

| TiN/HfO <sub>2</sub> /Ti/TiN                                | 0.25-1                                       | -                             | [21]      |

| Pt/HfO <sub>2</sub> /TiN                                    | 1-1.3                                        | 10 <sup>2</sup>               | [22]      |

| Pt/Ta <sub>2</sub> O <sub>5-x</sub> /TaO <sub>2-x</sub> /Pt | 0.5                                          | 10                            | [24]      |

| Pt/Ta <sub>2</sub> O <sub>5</sub> /Ta/Pt                    | 0.3-0.6                                      | 10-10 <sup>2</sup>            | [26]      |

| Pt/Ta <sub>2</sub> O <sub>5</sub> /W/Pt                     | 0.4-0.6                                      | 10-10 <sup>3</sup>            | [26]      |

input combination. It demonstrates that the voltage across the input memristors is not negligible and may unintentionally change their logical state during the logical operation. Since the voltage polarity of the inputs is opposite to the voltage polarity of the output, when a reset event is targeted on the output, we risk triggering a set event on the inputs. This leads to the following device parameters condition to ensure input stability:

$$\left| \frac{V_{\text{SET}}}{V_{\text{RESET}}} \right| > 2. \tag{2}$$

While this condition can be extended for an *n*-input MAGIC NOR gate:

$$\left| \frac{V_{\text{SET}}}{V_{\text{RESET}}} \right| > \frac{1 + \frac{1}{1 + \frac{R_{\text{ON}}}{R_{\text{OFF}}} \cdot (n-1)}}{1 + \frac{R_{\text{ON}}}{R_{\text{OFF}}} \cdot n}$$

(3)

correct logic implementation requires that  $R_{\rm ON} \ll (R_{\rm OFF}/n)$ , which reduces (3) to approximately (2). It is noted that other gates based on the same principle of conditional reset switching, e.g., NOT [6], NAND [7], and minority logic function (MIN) [28], have a more relaxed condition on the set-to-reset voltage ratio, but still require  $|V_{\rm RESET}| < |V_{\rm SET}|$ .

Originally, this condition was described to prevent destructive input operation and not for the functionality of the gate operation itself [6], [7]. Table II lists different popular VCM memristive devices and demonstrates that they do not sustain the MAGIC NOR condition for input stability. A recent study simulated MAGIC NOR with set/reset voltage pairs that do

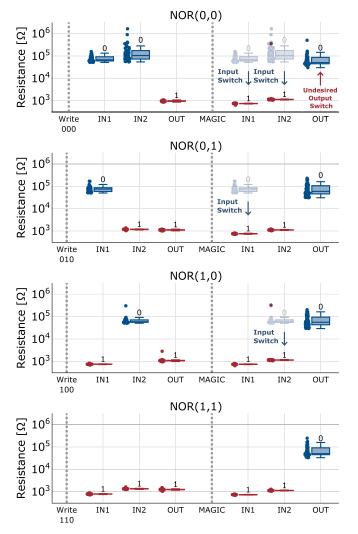

Fig. 2. Results of 50 cycles of MAGIC NOR attempts measured on the fabricated VCM devices. For the NOR(0, 0) case, due to input instability, the inputs switch, resulting an undesired output switch.

not fulfill the condition for input stability [29]. It discussed the fact that input stability is critical, since changing the inputs means that, eventually, the output will also change. The authors suggested solving this issue by finding a pulse length that is sufficiently long to switch the output for the desired cases, but short enough to prevent unintended switching for the (IN1=IN2='0') case. While they succeeded in simulating this for a single gate, they eventually concluded that to execute MAGIC NOR in a crossbar array, a device with  $|V_{\rm RESET}| \ll |V_{\rm SET}|$  is needed. Furthermore, in our view, basing the functionality of the gate on fine-timing of the pulse length is impractical for real devices because of cycle-to-cycle variations in the switching time between states.

We conducted several experiments with fabricated VCM devices, and concluded that input stability is critical for proper logic operation. For successful logic operation of the MAGIC NOR gate, we were interested in switching the output in all input states, except the (IN1=IN2='0') case. Unfortunately, as can be seen from the results in Fig. 2, the output switched for all possible states of the inputs, including the (IN1=IN2='0') case, resulting in logical failure. The complete experimental setup is detailed in Section IV.

The instability of the inputs was dominant when the two inputs are initially in the  $R_{\rm OFF}$  state. Furthermore, for almost all the cycles, if an input was in the  $R_{\rm OFF}$  state, it switched to  $R_{\rm ON}$ . These results can be explained by the voltage across the input cells, which was above the set threshold. This instability of the input cells can further explain the logical failure of the MAGIC NOR gate. For the (IN1=IN2='0') state, the voltage across the output cell is lower than the reset threshold, but the voltage across the inputs is higher than the set threshold. This causes a switching event on the inputs. After the input is switched, the state of the gate is effectively in a different input combination. Then, the voltage across the output cell is greater than the reset threshold, causing an undesired switching of the output. Logically, we can think about it as if we moved from one row of the truth table to another.

Considering these experimental results, we conclude that to support computation using VCM memristive devices, new MAGIC gates that support the set-to-reset ratio of VCM devices are required. In Section III, we propose three gates that fit the VCM properties and are compatible within a memristive crossbar array.

#### III. NEW MAGIC GATES

## A. MAGIC OR

The same structure of a two-input MAGIC, as shown in Fig. 1, can be used to implement different logic gates [7]. Herein, we propose a MAGIC OR gate. First, the output memristor is initialized to  $R_{\rm OFF}$  (rather than  $R_{\rm ON}$  in NOR). Hence, a set event on the output is targeted, as opposed to a reset event in MAGIC NOR. To support this, a negative  $V_{\rm G}$  is used. In the evaluation step, the voltage across the output is

$$V_{\rm OUT}({\rm IN1,IN2}) = V_{\rm G} \cdot \frac{R_{\rm OFF}}{R_{\rm IN1}||R_{\rm IN2} + R_{\rm OFF}}.$$

(4)

Assume  $R_{\text{OFF}} \gg R_{\text{ON}}$ , by setting  $V_{\text{G}} \approx -|V_{\text{SET}}|$ , we maintain the output in  $R_{\text{OFF}}$  for the (IN1=IN2='0') case, and switch it to  $R_{\text{ON}}$  for any other input combination. This gives the desired functionality of an OR gate.

The voltages across inputs and output for the MAGIC OR gate are listed in Table III. The voltage across the inputs is always approximately 0 V, except for the (IN1=IN2='0') case, where the inputs are already in the  $R_{\rm OFF}$  state. Hence, input stability is guaranteed and, in terms of functionality, the MAGIC OR gate can be performed without any limitation on the set-to-reset voltage ratio of the device.

Nevertheless, for the cases where the output switches to  $R_{\rm ON}$ , the amplitude of the voltage across the inputs increases during the operation. Therefore, if we want to guarantee a nondestructive operation and keep the inputs unchanged even after the output switched to  $R_{\rm ON}$ , the threshold voltages should fulfill the following condition:

$$\left| \frac{V_{\text{SET}}}{V_{\text{RESET}}} \right| < 2 \tag{5}$$

since once the output has completed the switch to  $R_{\rm ON}$ , the maximum voltage across the inputs is half of the applied voltage. It is noted that all the devices listed in Table II fulfill this condition.

If we extend these results for an *n*-input MAGIC OR gate, we get similar results. Before the output is switched,

| State                  |                        | Voltage                |                         |

|------------------------|------------------------|------------------------|-------------------------|

| $R_{IN1}$              | $R_{IN2}$              | $V_{IN}$               | $V_{OUT}$               |

| R <sub>OFF</sub> ('0') | $R_{OFF}$ ('0')        | $\frac{1}{3} V_{SET} $ | $-\frac{2}{3} V_{SET} $ |

| $R_{OFF}$ ('0')        | R <sub>ON</sub> ('1')  | 0V                     | $- V_{SET} $            |

| R <sub>ON</sub> ('1')  | R <sub>OFF</sub> ('0') | 0V                     | $- V_{SET} $            |

|                        |                        |                        |                         |

TABLE III

INPUT AND OUTPUT VOLTAGES FOR THE MAGIC OR GATE

the voltage across the inputs is always approximately 0 V, except for the case where all the inputs are in the  $R_{\rm OFF}$  state. After switching, the maximum voltage across the inputs is half of the applied voltage.

$-|V_{SET}|$

$R_{ON}$  ('1')

## B. MAGIC NIMP

$R_{ON}$  ('1')

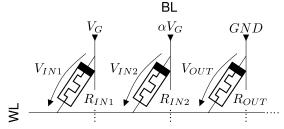

Enabling MAGIC OR is still insufficient for in-memory logic, since it is not functionally complete. To support (partially) complete logic, we introduce another MAGIC gate by breaking the symmetry between the two inputs, as shown in Fig. 3.

The output cell is initialized to  $R_{\rm OFF}$ , and in the evaluation step,  $V_{\rm G}$  is applied to the bitline of one of the inputs, while  $\alpha V_{\rm G}$  (0 <  $\alpha$  < 1) is applied to the bitline of the other input. The voltage across the output during the evaluation step is

$$V_{\text{OUT}}(\text{IN1,IN2}) = V_{\text{G}} \cdot \frac{R_{\text{IN2}} ||R_{\text{OFF}}|}{R_{\text{IN2}} ||R_{\text{OFF}} + R_{\text{IN1}}|} + \alpha V_{\text{G}} \cdot \frac{R_{\text{IN1}} ||R_{\text{OFF}}|}{R_{\text{IN1}} ||R_{\text{OFF}} + R_{\text{IN2}}|}.$$

(6)

Assume  $R_{\text{OFF}} \gg R_{\text{ON}}$ , by setting  $V_G \approx -|V_{\text{SET}}|$ , switching is achieved only in the (IN1='1', IN2='0') case, resulting in the not implication (NIMP) operation.

The NIMP logic operation has previously been suggested for memristive crossbars, using a crossbar structure with a resistor in the periphery. Chen *et al.* [30] proposed a two-memristor version, where the output overwrites one of the inputs. It was simulated and used sequentially to implement more complex logic operations [31]. Kim and Williams [32] demonstrated a three-memristor, nondestructive version. The peripheral resistor was left floating, so, essentially, the gate functionality is similar to ours.

The factored voltage,  $\alpha V_{\rm G}$ , gives some degree of freedom for gate implementation. To minimize errors, the voltage on the output should be minimal for all non-switching cases. At the same time, to ensure input stability, the voltage across the inputs should be minimal, for all input combinations. The maximum voltage across the output, for all non-switching cases, is given by the (IN1=IN2='1') case. The maximum voltage across the inputs, that can cause input switching, is the voltage across IN2 for the (IN1='1,' IN2='0') case. Since  $\alpha$  has an opposite effect on the magnitude of these voltages, we select  $\alpha = \frac{1}{3}$ , their equality point.

The voltages across inputs and output for the MAGIC NIMP gate are listed in Table IV. The (IN1=IN2='1') input case

Fig. 3. Schematic of a MAGIC NIMP gate within a crossbar.

TABLE IV

INPUT AND OUTPUT VOLTAGES FOR THE MAGIC NIMP GATE

| State                 |                        | Voltage                |                         |                         |

|-----------------------|------------------------|------------------------|-------------------------|-------------------------|

| $R_{IN1}$             | $R_{IN2}$              | $V_{IN1}$              | $V_{IN2}$               | $V_{OUT}$               |

| $R_{OFF}$ ('0')       | R <sub>OFF</sub> ('0') | $\frac{5}{9} V_{SET} $ | $-\frac{1}{9} V_{SET} $ | $-\frac{4}{9} V_{SET} $ |

| $R_{OFF}$ ('0')       | R <sub>ON</sub> ('1')  | $\frac{2}{3} V_{SET} $ | 0V                      | $-\frac{1}{3} V_{SET} $ |

| $R_{ON}$ ('1')        | R <sub>OFF</sub> ('0') | 0V                     | $-\frac{2}{3} V_{SET} $ | $- V_{SET} $            |

| R <sub>ON</sub> ('1') | R <sub>ON</sub> ('1')  | $\frac{1}{3} V_{SET} $ | $-\frac{1}{3} V_{SET} $ | $-\frac{2}{3} V_{SET} $ |

forces the following condition on the threshold voltages:

$$\left| \frac{V_{\text{SET}}}{V_{\text{RESET}}} \right| < 3. \tag{7}$$

Therefore, the MAGIC NIMP gate can be implemented on devices with low set-to-reset voltage ratios. For the (IN1='1', IN2='0') input case, since the output is being switched, the voltage across the inputs changes during the operation. To guarantee a nondestructive operation, and keep the inputs unchanged, even after the output switched to  $R_{\rm ON}$ , the threshold voltages should fulfill the same condition in (5).

## C. Two-Cycle MAGIC XOR

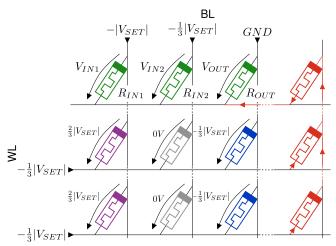

In the MAGIC NIMP gate design, we initialized the output to  $R_{\rm OFF}$ , and targeted a set event. If the output is not initialized, and is already in  $R_{\rm ON}$ , a MAGIC NIMP operation will not affect its state. Namely, if we apply subsequent operations on the same output, without an initialization cycle between them, we gain an OR operation between these operations. Thus, we can create a two-cycle XOR logic gate, by running the NIMP operation twice, according to the following steps.

- 1) Initialize the output memristor to  $R_{\text{OFF}}$ .

- 2) Apply  $-|V_{\text{SET}}|$  on IN1 bitline,  $-\frac{1}{3}|V_{\text{SET}}|$  on IN2 bitline, and ground OUT bitline.

- 3) Apply  $-\frac{1}{3}|V_{\text{SET}}|$  on IN1 bitline,  $-|V_{\text{SET}}|$  on IN2 bitline, and ground OUT bitline.

The results of these steps are presented for each input case in Table V, which corresponds to the truth table of a XOR gate.

## D. Crossbar Compatibility

The structure of the proposed MAGIC gates is compatible with the standard memristive memory crossbar array. To reliably perform computation within the crossbar array, a voltage isolation scheme is required to lower the sneak-path current and the write-disturb phenomena [8]. For MAGIC operations,

Fig. 4. MAGIC NIMP within a crossbar array. Cells participating in the logic operation are marked in green. Unselected cells with a constant voltage drop of  $-\frac{1}{3}|V_{\text{SET}}|$ ,  $\frac{2}{3}|V_{\text{SET}}|$  and 0 V are marked in blue, purple and gray, respectively. Floating cells and the possible sneak-path current passing through them are marked in red.

TABLE V

MAGIC XOR GATE STEPS

| Input |     | Output                 |                           |                                       |

|-------|-----|------------------------|---------------------------|---------------------------------------|

| IN1   | IN2 | Step (1)<br>Initialize | Step (2)<br>NIMP(IN1,IN2) | Step (3)<br>OR(OUT,<br>NIMP(IN2,IN1)) |

| '0'   | '0' | '0'                    | '0'                       | '0'                                   |

| '0'   | '1' | '0'                    | '0'                       | '1'                                   |

| '1'   | '0' | '0'                    | '1'                       | '1'                                   |

| '1'   | '1' | '0'                    | '0'                       | '0'                                   |

we set unselected rows to a third of the set voltage, and keep unused bitlines floating, as shown in Fig. 4 for the MAGIC NIMP gate. This maintains the voltage across the unselected cells below the switching threshold. Nevertheless, the sneakpath currents from unselected columns still affect the output of the gate, as demonstrated in the red mark in Fig. 4, where current flows from the unselected cells to the output. Given the resistance of cells and wires, this effect is low and can be mitigated by minor adjustments to the input voltages. MAGIC operations can be also implemented in selector-based crossbar arrays, e.g., 1T1R [33] 1S1R [18], and will likely suffer less from sneak-path and write-disturb phenomena. We are planning to examine the use of such structures in future work. The distribution of voltages between the operating cells, as described in the proposed gates, remains valid as long as the wire resistance is negligible when compared with the memristor resistance. In large crossbar arrays, this assumption might not hold [8]. We leave the exploration of this constraint in large arrays for future work.

#### IV. EXPERIMENTS

## A. Fabrication

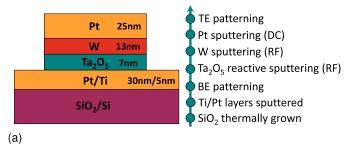

To experimentally demonstrate the proposed MAGIC gates, a thoroughly studied VCM device [26], [34] was fabricated.

Fig. 5. Pt/Ta<sub>2</sub>O<sub>5</sub>/W/Pt VCM device fabrication details. (a) Schematic cross-sectional diagram of experimental split conditions. (b) SEM image of the 2  $\mu$ m × 2  $\mu$ m VCM device in passive crossbar configuration.

TABLE VI

DEVICE MEASUREMENT PARAMETERS

| Parameter           | Value                |

|---------------------|----------------------|

| $V_{SET}$           | -1.0 [V]             |

| $V_{RESET}$         | 2.0 [V]              |

| $V_{READ}$          | 0.1 [V]              |

| $R_{ON}$            | $2-5 [k\Omega]$      |

| $R_{OFF}$           | $50 - 500 [k\Omega]$ |

| $t_{SET}$           | $0.5~[\mu s]$        |

| $t_{RESET}$         | $1 \ [\mu s]$        |

| $t_{MAGIC}$         | $2 [\mu s]$          |

| $t_{RISE}/t_{FALL}$ | 30 [ns]              |

|                     |                      |

About 5-nm-thick titanium (Ti) and 30-nm-thick platinum (Pt) layers were deposited by sputtering on a thermally grown 450-nm-thick SiO<sub>2</sub> layer on a Si substrate. Next, photolithography and dry-etching processes were used to pattern the Pt layer as a bottom electrode. Thereafter, 7-nm-thick Ta<sub>2</sub>O<sub>5</sub> was deposited by reactive sputtering under a process gas mixture of argon (77%) and oxygen (23%) with an RF power of 116 W, and at a chamber pressure of  $2.3 \times 10^{-2}$  mbar. Without breaking the vacuum, a 13-nm-thick tungsten (W) and a 25-nm-thick Pt layer were deposited by RF and dc sputtering, respectively. All deposition processes were performed at room temperature. To pattern the top electrode, photo-lithography with positive photoresist was applied. After the photoresist

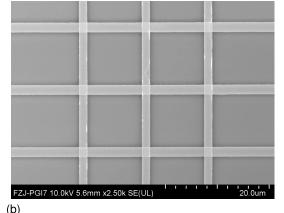

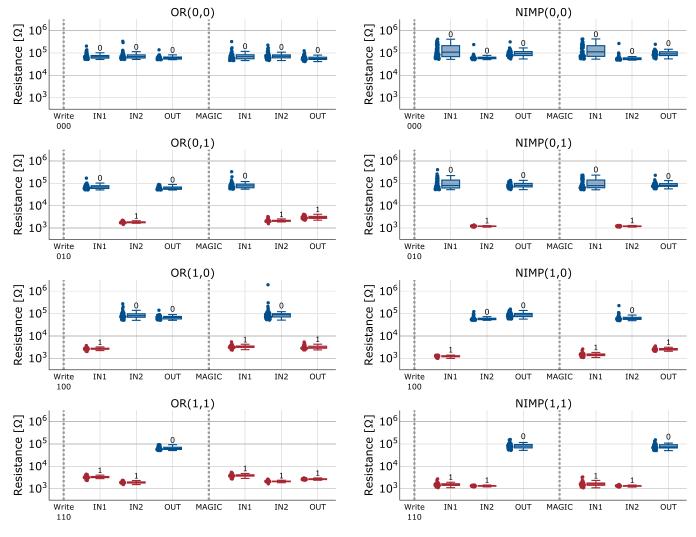

Fig. 6. Results of 50 cycles of MAGIC OR measured on the fabricated VCM device. The results show correct logic operation and exhibit input stability.

Fig. 7. Results of 50 cycles of MAGIC NIMP measured on the fabricated VCM device. The results show correct logic operation and exhibit input stability.

development, the top electrode was etched down with reactive ion beam etching (RIBE), forming the Pt/Ta<sub>2</sub>O<sub>5</sub>/W/Pt VCM device sketched in Fig. 5(a). A scanning electron microscope (SEM) image of the patterned passive crossbar structure, with a 2  $\mu$ m  $\times$  2  $\mu$ m cell size, is shown in Fig. 5(b).

# B. Functionality and Robustness

The experiments were managed using Keysight's B1530 WGFMU for voltage pulse control, a probe station, and an automated script to perform write, read, and MAGIC operations on the cells. The measured device parameters and selected timing conditions are listed in Table VI. To program a cell to  $R_{\rm ON}$ , we use a voltage pulse with an amplitude of  $V_{\rm SET}$  and width of  $t_{\rm SET}$ . To program it to  $R_{\rm OFF}$ , we use a voltage pulse with an amplitude of  $t_{\rm RESET}$ . For each gate (NOR, OR, NIMP), we tested the four input combinations and measured the output. For each input pattern, the test protocol was as follows.

1) Apply write pulses to program the inputs to their desired logical state and the output to an initial state ( $R_{\text{OFF}}$  or  $R_{\text{ON}}$ , according to the desired logic gate).

- 2) Read the resistance of the inputs and output by grounding the bitlines, applying  $V_{\text{READ}}$  to the wordline (WL) and reading the resulting current in each bitline. If the resistance is not in the desired state, go back to step (1).

- 3) Apply the MAGIC pulse.

- 4) Read the resistance of the output and the input memristors.

Each gate was tested for 50 cycles. Figs. 2, 6, and 7 present the results of the test protocol for the NOR, OR, and NIMP MAGIC gates, respectively. The *x*-axis represents the cell state or an operation (initialization or gate evaluation) and the *y*-axis represents the measured resistance in logarithmic scale. Each read cycle is plotted as a scatter and a median box is marked. By comparing the resistance of the output cell before and after the MAGIC pulse, the switching event can be identified, if it occurs.

The results for the MAGIC OR (Fig. 6) and MAGIC NIMP (Fig. 7) show correct logic operation and exhibit input stability. Although there was some resistance variation, which is common for these devices [26], the general logic value was correct and there was always a distinguishable margin (at least

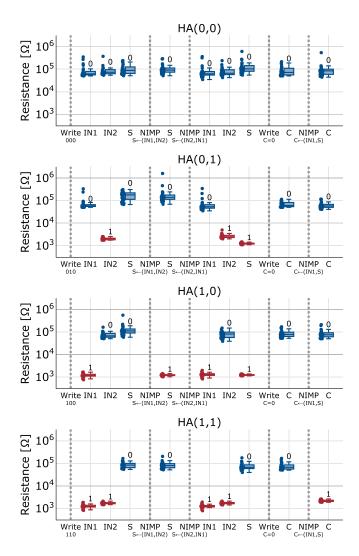

Fig. 8. Results of 25 cycles of the 1-bit half adder implementation using MAGIC gates.

one order of magnitude) in the resistance between the two logical states.

### C. Timina

To find the minimal pulse duration for performing the logic operation, we selected the input case (among those that switch the output), with the lowest voltage across the output, and increased the pulse length until a switching event occurred. Successful results were obtained with a minimal pulse width of 2  $\mu$ s. Since this is an experimental setup, we speculate that for a complete integrated design, with an optimized cell and lower capacitance, even substantially shorter pulses will work. The relatively long pulse length is dominated by the equipment's capacitance, mostly the probes' capacitance. Additionally, the capacitance driven by the gate is higher than a single cell because of the floating WL. To explore how variations of the pulse length affect the results, we increased the length of the pulse to as long as 100  $\mu$ s, while still getting correct results and stable inputs. This suggests robustness of the gates to pulse width and switching time variations.

TABLE VII

COMPARISON OF STATEFUL FULL ADDER IMPLEMENTATIONS

| Logic<br>Operations                 | Computation<br>Cycles | Additional<br>Cells | Additional<br>Resistor |

|-------------------------------------|-----------------------|---------------------|------------------------|

| IMPLY [5]                           | 29/23                 | 2/5                 | Yes                    |

| NIMP, AND,<br>OR, XOR [32]          | 8                     | 2                   | Yes                    |

| IMPLY, COPY,<br>ORNOR [35]          | 16                    | 1                   | Yes                    |

| NOR, NOT [8]                        | 15/13                 | 5/10                | No                     |

| NOR, NOT,<br>NAND, MIN,<br>XOR [28] | 6                     | 2                   | No                     |

| NIMP, OR,<br>XOR<br>(This Work)     | 6                     | 1                   | No                     |

#### D. Half Adder Demonstration

To show the performance of the proposed gates as a building block for more complex operations, we present a 1-bit half adder. Using the previously described XOR implementation, we get the sum output:

$$S_{\rm HA} = {\rm IN1} \oplus {\rm IN2}.$$

(8)

This sum can be further used to obtain the carry output:

$$C_{\text{HA}} = \text{IN1} \cdot \text{IN2} = \text{NIMP}(\text{IN1}, S_{\text{HA}}).$$

(9)

Fig. 8 shows correct logic operation of the proposed 1-bit half adder for 25 cycles. This demonstrates how the output of one MAGIC gate can serve as the input for another MAGIC gate. This concept can be extended to perform any desired function.

The half adder operation can be combined in consecutive cycles to create a full adder

$$S_{\text{FA}} = S_{\text{HA}} \oplus C_{\text{IN}}$$

$$C_{\text{FA}} = C_{\text{HA}} + \text{NIMP}(C_{\text{IN}}, S_{\text{FA}}). \tag{10}$$

Table VII compares different stateful logic full adder designs in terms of computation cycles, additional memristive cells, and whether an additional peripheral resistor is required. For some implementations, there is a tradeoff between the number of cycles and required cells. This comparison highlights that the full adder design using the proposed gates is attractive, since it is compact when compared with other stateful logic techniques, in terms of both computation time and area. Energy dissipation is not included in this comparison since it is highly dependent on device parameters, which are different for each study. Additionally, most of these studies are based on simulations and not experimental measurements. Nevertheless, generally, reset switching energy is higher than set energy in VCM devices [23], so the proposed logic gates may also reduce the energy dissipation compared to some of the implementations mentioned.

### V. CONCLUSION

In this article, we demonstrated the limitations of executing the popular MAGIC NOR gate in VCM memristive devices arising from input instability. To overcome this problem and perform computation within a memristive memory, three new logic gates based on the stateful MAGIC technique were proposed. These gates ensure input stability for devices such as VCM memristors, where the set voltage is lower than the reset voltage.

The design and usage of these gates in VCM devices were successfully demonstrated on fabricated Pt/Ta<sub>2</sub>O<sub>5</sub>/W/Pt VCM devices. Additionally, we demonstrated how more complex logic operations can be implemented, by consecutive operations of the proposed gates. This work enables stateful logic based on MAGIC for popular memristive technologies and is an important milestone toward real processing-in-memory.

#### REFERENCES

- M. Di Ventra and F. L. Traversa, "Perspective: Memcomputing: Leveraging memory and physics to compute efficiently," *J. Appl. Phys.*, vol. 123, no. 18, May 2018, Art. no. 180901, doi: 10.1063/1.5026506.

- [2] M. A. Zidan, J. P. Strachan, and W. D. Lu, "The future of electronics based on memristive systems," *Nature Electron.*, vol. 1, no. 1, pp. 22–29, Jan. 2018, doi: 10.1038/s41928-017-0006-8.

- [3] D. Ielmini and H.-S.-P. Wong, "In-memory computing with resistive switching devices," *Nature Electron.*, vol. 1, no. 6, pp. 333–343, Jun. 2018, doi: 10.1038/s41928-018-0092-2.

- [4] J. Reuben et al., "Memristive logic: A framework for evaluation and comparison," in Proc. 27th Int. Symp. Power Timing Model., Optim. Simulation (PATMOS), Sep. 2017, pp. 1–8, doi: 10.1109/ PATMOS.2017.8106959.

- [5] S. Kvatinsky, G. Satat, N. Wald, E. G. Friedman, A. Kolodny, and U. C. Weiser, "Memristor-based material implication (IMPLY) logic: Design principles and methodologies," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 22, no. 10, pp. 2054–2066, Oct. 2014, doi: 10.1109/TVLSI.2013.2282132.

- [6] S. Kvatinsky et al., "MAGIC—Memristor-aided logic," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 11, pp. 895–899, Nov. 2014, doi: 10.1109/TCSII.2014.2357292.

- [7] N. Wald and S. Kvatinsky, "Design methodology for stateful memristive logic gates," in *Proc. IEEE Int. Conf. Sci. Electr. Eng. (ICSEE)*, Nov. 2016, pp. 1–5, doi: 10.1109/ICSEE.2016.7806155.

- [8] N. Talati, S. Gupta, P. Mane, and S. Kvatinsky, "Logic design within memristive memories using memristor-aided loGIC (MAGIC)," *IEEE Trans. Nanotechnol.*, vol. 15, no. 4, pp. 635–650, Jul. 2016, doi: 10.1109/TNANO.2016.2570248.

- [9] R. Ben Hur and S. Kvatinsky, "Memory processing unit for inmemory processing," in *Proc. Int. Symp. Nanosc. Archit. (NANOARCH)*, Jul. 2016, pp. 171–172, doi: 10.1145/2950067.2950086.

- [10] A. Haj-Ali, R. Ben-Hur, N. Wald, and S. Kvatinsky, "Efficient algorithms for in-memory fixed point multiplication using MAGIC," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2018, doi: 10.1109/ ISCAS.2018.8351561.

- [11] A. Haj-Ali, R. Ben-Hur, N. Wald, R. Ronen, and S. Kvatinsky, "IMAGING: In-memory algorithms for image processing," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 12, pp. 4258–4271, Jun. 2018, doi: 10.1109/TCSI.2018.2846699.

- [12] M. Imani, S. Gupta, Y. Kim, and T. Rosing, "FloatPIM: In-memory acceleration of deep neural network training with high precision," in *Proc. 46th Int. Symp. Comput. Archit.*, Jun. 2019, pp. 802–815, doi: 10.1145/3307650.3322237.

- [13] G. C. Adam, B. D. Hoskins, M. Prezioso, and D. B. Strukov, "Optimized stateful material implication logic for three-dimensional data manipulation," *Nano Res.*, vol. 9, no. 12, pp. 3914–3923, Dec. 2016, doi: 10.1007/s12274-016-1260-1.

- [14] L.-J. Yu et al., "Stateful logic operations implemented with graphite resistive switching memory," *IEEE Electon Device Lett.*, vol. 39, no. 4, pp. 607–609, Apr. 2018, doi: 10.1109/LED.2018.2803117.

- [15] Z.-Y. He et al., "Atomic layer-deposited HfAlOx-based RRAM with low operating voltage for computing in-memory applications," Nanosc. Res. Lett., vol. 14, no. 1, p. 51, Dec. 2019, doi: 10.1186/s11671019-2875-4.

- [16] H. Bae et al., "Functional circuitry on commercial fabric via textile-compatible nanoscale film coating process for fibertronics," Nano Lett., vol. 17, no. 10, pp. 6443–6452, Sep. 2017, doi: 10.1021/acs.nanolett.7b03435.

- [17] B. C. Jang et al., "Zero-static-power nonvolatile logic-in-memory circuits for flexible electronics," Nano Res., vol. 10, no. 7, pp. 2459–2470, Jul. 2017, doi: 10.1007/s12274-017-1449-y.

- [18] B. C. Jang et al., "Memristive logic-in-memory integrated circuits for energy-efficient flexible electronics," Adv. Funct. Mater., vol. 28, no. 2, Jan. 2018, Art. no. 1704725, doi: 10.1002/adfm.201704725.

- [19] R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories–nanoionic mechanisms, prospects, and challenges," *Adv. Mater.*, vol. 21, nos. 25–26, pp. 2632–2663, Jul. 2009, doi: 10.1002/adma.200900375.

- [20] F. Lentz, B. Roesgen, V. Rana, D. J. Wouters, and R. Waser, "Current compliance-dependent nonlinearity in TiO<sub>2</sub> ReRAM," *IEEE Electron Device Lett.*, vol. 34, no. 8, pp. 996–998, Aug. 2013, doi: 10.1109/LED.2013.2265715.

- [21] C. Ho et al., "Integrated HfO2-RRAM to achieve highly reliable, greener, faster, cost-effective, and scaled devices," in IEDM Tech. Dig., Dec. 2017. pp. 2.6.1–2.6.4, doi: 10.1109/IEDM.2017.8268314.

- [22] S.-Y. Hu et al., "Reconfigurable Boolean logic in memristive crossbar: The principle and implementation," *IEEE Electron Device Lett.*, vol. 40, no. 2, pp. 200–203, Feb. 2019, doi: 10.1109/LED.2018.2886364.

- [23] A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, and R. S. Williams, "Sub-nanosecond switching of a tantalum oxide memristor," *Nanotechnology*, vol. 22, no. 48, Nov. 2011, Art. no. 485203, doi: 10.1088/09574484/22/48/485203.

- [24] M.-J. Lee et al., "A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> bilayer structures," Nature Mater., vol. 10, no. 8, pp. 625–630, Jul. 2011, doi: 10.1038/nmat3070.

- [25] L. Goux, A. Fantini, Y. Y. Chen, A. Redolfi, R. Degraeve, and M. Jurczak, "Evidences of electrode-controlled retention properties in Ta<sub>2</sub>O<sub>5</sub>-based resistive-switching memory cells," ECS Solid State Lett., vol. 3, no. 11, pp. 79–81, Sep. 2014, doi: 10.1149/2.0011412ssl.

- [26] W. Kim et al., "Impact of oxygen exchange reaction at the ohmic interface in Ta<sub>2</sub>O<sub>5</sub>-based ReRAM devices," Nanoscale, vol. 8, no. 41, pp. 17774–17781, Oct. 2016, doi: 10.1039/C6NR03810G.

- [27] A. Haj-Ali, R. Ben-Hur, N. Wald, R. Ronen, and S. Kvatinsky, "Not in name alone: A memristive memory processing unit for real inmemory processing," *IEEE Micro*, vol. 38, no. 5, pp. 13–21, Sep. 2018, doi: 10.1109/MM.2018.053631137.

- [28] S. Gupta, M. Imani, and T. Rosing, "FELIX: Fast and energy-efficient logic in memory," in *Proc. Int. Conf. Comput.-Aided Des.*, vol. 7, Nov. 2018, pp. 1–7, doi: 10.1145/3240765.3240811.

- [29] A. Siemon, D. Wouters, S. Hamdioui, and S. Menzel, "Memristive device modeling and circuit design exploration for computation-inmemory," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2019, pp. 1–5, doi: 10.1109/iscas.2019.8702600.

- [30] Q. Chen, X. Wang, H. Wan, and R. Yang, "A logic circuit design for perfecting memristor-based material implication," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 36, no. 2, pp. 279–284, Feb. 2017, doi: 10.1109/TCAD.2016.2578881.

- [31] X. Wang, Q. Wu, Q. Chen, and Z. Zeng, "A novel design for memristor-based multiplexer via NOT-material implication," *IEEE Trans. Comput. Aided Design Integr. Circuits Syst.*, vol. 37, no. 7, pp. 1436–1444, Jul. 2018, doi: 10.1109/TCAD.2017.2753204.

- [32] K. M. Kim and R. S. Williams, "A family of stateful memristor gates for complete cascading logic," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 11, pp. 4348–4355, Nov. 2019, doi: 10.1109/tcsi.2019.2926811.

- [33] W. Shen et al., "Stateful logic operations in one-transistor-one-resistor resistive random access memory array," IEEE Electron Device Lett., vol. 40, no. 9, pp. 1538–1541, Sep. 2019, doi: 10.1109/led.2019.2931947.

- [34] W. Kim, S. Menzel, D. J. Wouters, R. Waser, and V. Rana, "3-bit multi-level switching by deep reset phenomenon in Pt/W/TaOX/Pt-ReRAM devices," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 564–567, May 2016, doi: 10.1109/LED.2016.2542879.

- [35] A. Siemon et al., "Stateful three-input logic with memristive switches," Sci. Rep., vol. 9, no. 1, Dec. 2019, Art. no. 14618, doi: 10.1038/s41598-019-51039-6.