# Impact of the Ohmic Electrode on the Endurance of Oxide-Based Resistive Switching Memory

Stefan Wiefels<sup>®</sup>, *Graduate Student Member, IEEE*, Moritz von Witzleben<sup>®</sup>, Michael Hüttemann, Ulrich Böttger, Rainer Waser<sup>®</sup>, *Member, IEEE*, and Stephan Menzel<sup>®</sup>, *Member, IEEE*

Abstract—As one of the key aspects in the reliability of redox-based resistive switching memories (ReRAMs), maximizing their endurance is of high relevance for industrial applications. The major limitation regarding endurance is considered the excessive generation of oxygen vacancies during cycling, which eventually leads to irreversible RESET failures. Thus, the endurance could be increased by using combinations of switching oxide and ohmic electrode (OE) metal that provides a high barrier for the generation of oxygen vacancies [defect formation energy (DFE)]. In this work, we present a sophisticated programming algorithm that aims to maximize the endurance within reasonable measurement time. Using this algorithm, we compare ReRAM devices with four different OE metals and confirm the theoretically predicted trend. Thus, our work provides valuable information for device engineering toward higher endurance.

Index Terms— Defect formation energy (DFE), endurance algorithm, endurance, OxRAM, redox-based resistive switching memory (ReRAM), valence change mechanism (VCM).

### I. INTRODUCTION

SINCE conventional memory architectures are about to reach physical scaling limitations [1], novel nonvolatile memory (NVM) technologies are intensively studied [2]. Among other concepts, redox-based resistive switching memory (ReRAM) gained a lot of attention [3], [4] due to its good

Manuscript received October 26, 2020; revised December 11, 2020; accepted December 29, 2020. Date of publication January 15, 2021; date of current version February 24, 2021. This work was supported in part by the Deutsche Forschungsgemeinschaft under Grant SFB 917 and in part by the Federal Ministry of Education and Research (BMBF, Germany) through the project NEUROTEC under Project 16ES1134 and Project 16ES1133K, based on the Jülich Aachen Research Alliance (JARA-Fit). The review of this article was arranged by Editor S. Alam. (Corresponding author: Stefan Wiefels.)

Stefan Wiefels, Moritz von Witzleben, Michael Hüttemann, and Ulrich Böttger are with the Institut für Werkstoffe der Elektrotechnik II (IWE II) and JARA-FIT, RWTH Aachen University, 52074 Aachen, Germany (e-mail: wiefels@iwe.rwth-aachen.de).

Rainer Waser is with the Institut für Werkstoffe der Elektrotechnik II (IWE II) and JARA-FIT, RWTH Aachen University, 52074 Aachen, Germany, and also with the Peter-Grünberg-Institut 7 and 10 (PGI-7&10), Forschungszentrum Jülich GmbH, 52425 Jülich, Germany.

Stephan Menzel is with the Institut für Werkstoffe der Elektrotechnik II (IWE II) and JARA-FIT, RWTH Aachen University, 52074 Aachen, Germany, and also with the Peter-Grünberg-Institut 7 (PGI-7), Forschungszentrum Jülich GmbH, 52425 Jülich, Germany.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3049765.

Digital Object Identifier 10.1109/TED.2021.3049765

scalability, fast operation, low power consumption, and high retention [3], [5]–[9].

Toward the industrial application of ReRAM, its reliability is highly relevant [10]. Along with variability [11] and retention [12], the endurance or maximum number of switching cycles until failure is one of the most important reliability aspects. While  $10^4$ – $10^5$  cycles are reported as typical endurance for flash memory [10], several groups reported ReRAM devices with an endurance of  $10^7 - 10^{12}$  cycles [13]–[18].

However, the ideal ReRAM device is not yet found, and several material combinations are under investigation [14]–[17]. For oxide-based ReRAM using the valence change mechanism (VCM) [3], Guo and Robertson [19] presented a theoretical approach toward optimized materials selection. Through density functional theory (DFT) calculations, they determined the defect formation energy (DFE) for the generation of oxygen vacancies at the interface of HfO2 or Ta2O5 with different ohmic electrode (OE) metals [19]. Regarding endurance, a high barrier for the formation of oxygen vacancies is desired since the excessive generation of oxygen vacancies during cycling is believed to be the predominant origin of irreversible RESET failures, leaving the device stuck in LRS [19]. Thus, Guo and Robertson [19] suggest to implement electrode metals with a low oxygen chemical potential in order to increase the DFE and, thus, the expected endurance. The influence of the DFE on the switching characteristics of Ta<sub>2</sub>O<sub>5</sub>-based devices was experimentally shown by Kim et al. [20].

In this work, we present experimental verification of the findings in [19]. In order to do so, VCM ReRAM devices based on ZrO2 are fabricated with four different electrode metals. A novel programming algorithm, inspired by the work of Meng et al. [21], is developed, which automatically determines the ideal programming parameters for each tested device. It is able to correct reversible endurance failures and aims to reach the maximum endurance of each device. As a consequence, the maximum endurance for each material combination can be determined and compared to the prediction in [19]. In addition, the algorithm dynamically adapts the frequency of voltage adjustments to the success rate of the individual device. If the cycling characteristics are more stable, the number of cycles without reading verify is increased, which accelerates the experiment. This enabled us to determine the maximum endurance of 50 devices for each material combination within

TABLE I

DEFECT FORMATION ENERGIES AT THE ME/HfO<sub>2</sub> INTERFACE

EXTRACTED FROM [19]

| Ma | terial | Hf  | Zr  | Ti | Ta   |

|----|--------|-----|-----|----|------|

| DF | E / eV | 0.1 | 0.2 | 1  | 1.65 |

reasonable measurement time, resulting in statistically sound results.

#### II. DEFECT FORMATION ENERGY

According to Guo and Robertson [19], the presence of a metal scavenging layer shifts the oxygen chemical potential of the oxide toward the oxygen-poor limit, which is close to the oxygen chemical potential of the respective scavenging metal. Thus, the DFE  $E_{\rm form}$  at the interface of the oxide with the metal electrode is obtained by the sum of the formation energy in the bulk oxide  $E_{\rm form,bulk}$  and the oxygen chemical potential  $\mu_{\rm Me}$  of the metal, reading

$$E_{\text{form}} = E_{\text{form,bulk}} + \mu_{\text{Me}}.$$

(1)

In principle, the DFE is the difference between the energy gained by oxidizing the top electrode and the energy required to reduce the oxide layer.

For the material combinations in this work, we obtain the parameters summarized in Table I. It may be noted here that the DFE is determined with respect to  $HfO_2$  with a DFE in the bulk oxide of  $E_{form,bulk}=5.9$  eV. However, since  $HfO_2$  and  $ZrO_2$  are nearly identical with respect to their physicochemical properties, only minor deviations are expected. For the generation of oxygen vacancies in bulk,  $ZrO_2$  values of  $E_{form,bulk}$  in the range of 5.4–6.4 eV are reported [22]. Foster *et al.* [23], [24] determined  $E_{form,bulk}=5.94$  eV for m- $ZrO_2$ . Nevertheless, the relative trend for the four metals should not be affected by an offset in  $E_{form,bulk}$ .

According to Table I, the lowest DFE is observed for the devices with Hf, followed closely by Zr. Since this low barrier is believed to cause the excessive generation of oxygen vacancies during cycling, the likelihood for the device to become stuck in LRS increases from cycle to cycle. This means that, in each SET process, more oxygen vacancies are generated at the interface of oxide and OE than recombined during RESET, which eventually leads to a too low-resistive state (LRS). In this case, the RESET fails even at higher voltages, which terminates the endurance of the tested device. This failure mechanism was also demonstrated after few cycles for Ta<sub>2</sub>O<sub>5</sub>-based devices by Kim *et al.* [20].

Thus, the shortest endurance is expected for the devices with Hf and Zr as OE. In contrast, Ti as OE metal should improve the endurance, and the best results are expected for Ta. Here, higher DFE should reduce the parasitical generation of excessive oxygen vacancies.

## III. EXPERIMENTAL

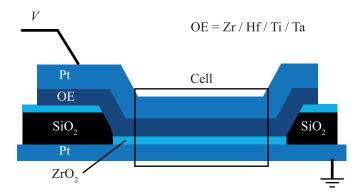

For the experimental verification of the proposed impact of the DFE [19], we fabricated VCM ReRAM devices in a  $1 \times 32$  line array structure, which is schematically shown in Fig. 1.

Fig. 1. Device stack of the samples fabricated in this work. The common Pt BE is covered by 30 nm  $SiO_2$ . A 7  $\mu$ m-wide channel is etched into the  $SiO_2$  layer and covered by 5 nm  $ZrO_2$ . Perpendicular to this channel, the top electrodes are structured via UV lithography; 20 nm of one of four different metals is deposited as OE and *in situ* covered by 30 nm Pt to prevent oxidation.

Therefore, 30 nm SiO<sub>2</sub> is deposited via electron-beam evaporation onto the common Pt bottom electrode (BE) covering the whole substrate. Using UV-lithography, a channel with a width of 7 µm is structured and then etched free. Subsequently, 5 nm ZrO<sub>2</sub> is deposited onto the sample via reactive RF-sputtering (80 W). After a further lithography step, the OE is deposited. Here, 20 nm of one of the four metals Zr (60 W), Hf (60 W), Ti (60 W), and Ta (12.5 W) is sputtered and in situ covered by 30 nm Pt (80 W) to prevent oxidation. It may be noted that the SiO<sub>2</sub> layer does not participate in resistive switching but is used to separate the single line arrays. The resulting stack of the switching VCM cell, as highlighted by the black box in Fig. 1, is (30 nm Pt/5 nm ZrO<sub>2</sub>/20 nm Me/30 nm Pt), with Me being Zr, Hf, Ti, or Ta. Thin OE layers have been demonstrated to oxidize due to residual oxygen in the fabrication process [25]. Thus, we decided for a 20 nm Me layer to ensure the presence of the respective metal.

In the literature, also symmetrical (Pt/ZrO<sub>2</sub>/Pt) devices have been demonstrated to switch (in unipolar mode) [26]. However, symmetrical electrodes may induce the complementary switching (CS) mode, which is considered a failure mechanism in bipolar switching devices and could lead to unstable switching characteristics [27]. Furthermore, the OE supports the electroforming operation [25], as will also be discussed in Section V.

The top electrodes of the line array are contacted by a probe card with 32 probes connected to a custom array tester by aixACCT Systems. The tester provides an arbitrary waveform generator and a switch box that maps the applied waveform to one of the 32 contacted top electrodes. The common BE is connected by an additional probe to the virtual ground of the measurement device where the resulting current is recorded.

To prepare the contacted cells for resistive switching, an electroforming operation is required. This is performed by a voltage ramp with a rise time of 20 ms to reach the maximum voltage  $V_{\rm max}$ . A series resistor of  $R_{\rm series}=10~{\rm k}\Omega$  is used to limit the current in the event of dielectric breakdown. Through a program-verify algorithm,  $V_{\rm max}$  is initialized at 2 V and increased stepwise to a maximum of 4 V if the operation fails.

The sweep rate depends on the respective stop voltage. For each material system, 50 individual devices are electroformed. Their endurance is determined by the developed algorithm presented in Section IV.

### IV. ENDURANCE ALGORITHM

In order to verify the impact of the DFE on the endurance, the latter has to be determined for different material combinations. For comparability, these endurance tests could be performed at identical switching parameters. However, if the SET and RESET voltages are optimized for one of the four material combinations, a worse endurance of the remaining three stacks could be attributed to inappropriate or unbalanced biasing. Therefore, we developed an algorithm that automatically determines the ideal programming conditions for each individual device.

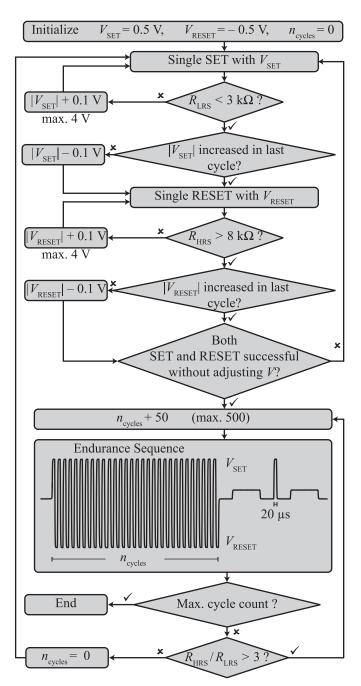

In general, the algorithm determines the lowest SET and RESET voltages with which the device switches reliably. Subsequently, a dedicated pulse sequence for endurance tests is applied which performs multiple SET/RESET cycles within one pulse sequence, followed by reading HRS and LRS. Here, a low number of cycles  $n_{\rm cycles}$  per pulse sequence allows for frequent voltage adjustments but increases the measurement time significantly. Therefore, the algorithm dynamically adjusts  $n_{\rm cycles}$  to the switching characteristics of the tested device.

A detailed flowchart of the algorithm is presented in Fig. 2. After initializing the SET voltage  $V_{\text{SET}} = 0.5 \text{ V}$ , the RESET voltage  $V_{\text{RESET}} = -0.5 \text{ V}$ , and the number of cycles per pulse sequence  $n_{\text{cycles}} = 0$  (which will be increased later), a single SET is applied to the device under test. If the resulting resistance of the cell exceeds the target of 3 k $\Omega$ , the SET voltage is increased by 0.1 V, and the SET is repeated. After a successful SET, the algorithm considers decreasing  $V_{\text{SET}}$  if the parameter was not increased in the previous step. This step is important to prevent a runaway of SET and RESET voltage up to the maximum of  $\pm 3$  V, which would cause higher stress to the device and early endurance failure. Subsequently, the RESET voltage is determined analogously, with a target resistance of  $R_{HRS} > 8 \text{ k}\Omega$ . The width of all programming pulses is kept constant at 20 µs due to limitations of the test setup. Shorter pulses may reduce the device stress and, thus, further increase endurance.

Both steps are repeated until SET and RESET are successful without voltage adjustments. Then, the number of cycles per pulse sequence is increased by +50 (up to a maximum of 500), and the actual endurance test sequence is executed. Here,  $n_{\rm cycles}$  SET/RESET cycles are performed, followed by one read pulse for the high resistive state (HRS) and one read pulse for the LRS. The programming pulses are alternated without an intermediate wait time. All reads are performed at 0.2 V.

As long as a defined maximum cycle number of  $2.0 \cdot 10^7$  cycles is not reached, the reads are evaluated. If the ratio of HRS and LRS resistance exceeds 3, the endurance sequence is considered successful. In this case,  $n_{\rm cycles}$  is increased again by +50, and the endurance sequence is repeated. If it fails, the number of cycles is reset to 0, and the

Fig. 2. Flowchart of the endurance algorithm. Initially, appropriate SET and RESET voltages are determined for the tested device. If SET or RESET fails, the respective voltage is increased. In the case of successful switching, a voltage decrease is considered. Once  $V_{\rm SET}$  and  $V_{\rm RESET}$  are determined, the endurance scheme is executed. Here, the number of cycles per pulse sequence is increased each time the previous sequence was successful. This allows for frequent voltage adjustments if the cycling is unstable and fast endurance assessment in case of reliable switching.

algorithm jumps back to the initial voltage adjustments. Thus, reversible endurance failures are corrected, and the endurance measurement continues with adjusted biasing conditions. If the single SET and RESET operations fail despite reaching one of the maximum voltages, the experiment is terminated, and the last successful cycle number is saved as the endurance of the device. Due to the fact that 32 cells of one line array

are contacted at once, the endurance test can automatically continue with the next device. It may be noted that the target read window of  $R_{\rm HRS}/R_{\rm LRS}>3$  is comparatively small. Aiming for a larger read window will presumably reduce the maximum endurance [28].

In conclusion, the algorithm aims to find the ideal switching parameters for each device with regard to maximum endurance. The number of cycles per pulse sequence is increased if the device switches reliably in order to reduce the measurement time. Nevertheless, frequent voltage adjustments are performed if necessary, and thus, reversible endurance failures can be corrected, and the maximum endurance is determined for each device. Accordingly, the results for the four tested material combinations are presented in the following.

## V. RESULTS

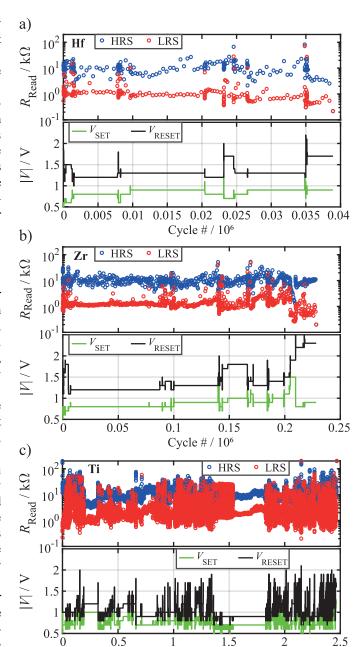

First, exemplary endurance traces measured with the four material stacks will be discussed. Later, a statistical evaluation is given. Fig. 3 shows exemplary endurance results for Hf, Zr, and Ti as OE metals. In each subfigure, the upper panel contains HRS and LRS resistances versus the cycle number, and the lower panel depicts the respective voltages applied by the algorithm.

As expected and shown in Fig. 3(a), the endurance of the  $ZrO_2/Hf$  stack is rather low. The algorithm is able to correct some early failures, but, after approximately,  $3.8 \cdot 10^4$  cycles, the device becomes irreversibly stuck in LRS.

Also, in line with the expectation, the endurance of an exemplary  $ZrO_2/Zr$  device, as shown in Fig. 3(b), is slightly higher compared to Hf as OE. Again, the algorithm corrected several cycling failures until an irreversible RESET failure occurs after approximately  $2.3 \cdot 10^5$  cycles. In both cases (Hf and Zr), the low endurance can be explained by the accumulation of excessive oxygen vacancies due to the low barrier for their generation [19].

Respectively, devices with Ti as OE metal provide a higher endurance, as demonstrated in Fig. 3(c). Here, the endurance of a typical  $\rm ZrO_2/Ti$  device is increased by one order of magnitude with respect to  $\rm ZrO_2/Zr$ . An irreversible RESET failure is observed after approximately  $2.5 \cdot 10^6$  cycles. However, the presented cycling characteristics are rather unstable and show large cycle-to-cycle variability. In this case, the presented algorithm is especially effective since it corrects all reversible endurance failures. The origin of the high variability might be the formation of different Ti suboxides at the  $\rm ZrO_2/Ti$  interface. As demonstrated by Kindsmüller *et al.* [25], the suboxide layer could be tuned by changing the thickness of the OE. Thus, future studies could investigate the impact of the suboxide layer on endurance.

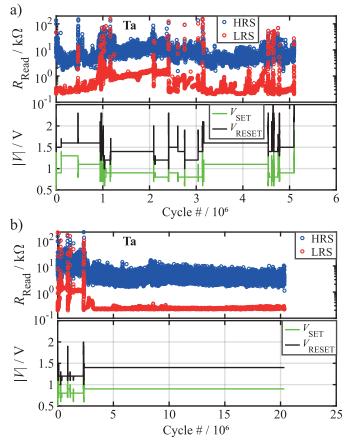

Finally, the endurance of two exemplary  $ZrO_2/Ta$  devices is shown in Fig. 4. As expected, considering the higher DFE at the  $ZrO_2/Ta$  interface, the devices with Ta as OE provide the highest endurance of all stacks tested in this work. The exemplary device in Fig. 4(a) reached approximately  $5.1 \cdot 10^6$  cycles until the RESET fails irrevocably. Until the terminal endurance failure, the cycling characteristics vary between rather stable periods in which the SET and RESET

Fig. 3. Exemplary endurance results for  $ZrO_2$  with (a) Hf, (b) Zr, or (c) Ti as OE metal. Each subfigure shows LRS and HRS resistance versus the cycle number in the upper panel and the corresponding SET and RESET voltages applied by the algorithm in the lower panel.

Cycle # / 106

voltages are kept constant, and more unstable periods. Here, the algorithm corrects several reversible endurance failures and tries to restore stable cycling.

In one of the best tested devices, as shown in Fig. 4(b), the same behavior is observed until approximately  $2.5 \cdot 10^6$  cycles. Subsequently, the characteristics become particularly stable, and no corrections are necessary for the remaining cycles. After approximately  $2.0 \cdot 10^7$  cycles, the defined maximum number of cycles is reached, and the experiment is terminated. Presumably, the device was still

Fig. 4. Exemplary endurance results for  $ZrO_2$  with Ta as OE metal. Each subfigure shows LRS and HRS resistance versus the cycle number in the upper panel and the corresponding SET and RESET voltages applied by the algorithm in the lower panel. (a) Cycling characteristics vary between stable and unstable periods. The latter are stabilized by the programming algorithm. Irreversible endurance failure after  $5.1 \cdot 10^6$  cycles (b) Cycling characteristics become remarkably stable after  $2.5 \cdot 10^6$ . No terminal endurance failure occurred but the experiment was terminated after approximately  $2.0 \cdot 10^7$  cycles.

operational at the end of the experiments and its endurance well above  $2.0 \cdot 10^7$  cycles.

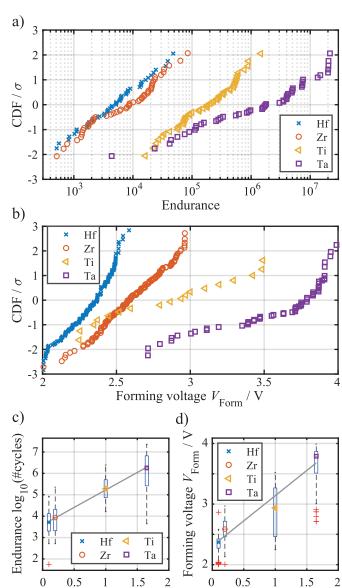

The presented examples follow the expected trend of prolonged endurance with higher DFE. Nevertheless, the significance of single-cell results is limited. Thus, the experiment is extended to 50 devices per stack. Using the discussed algorithm, the maximum endurance is determined for all devices and summarized by the distributions in Fig. 5(a). As already suggested by the single-device results, the endurance follows the predicted trend. Due to the very similar DFE with Hf and Zr, the resulting distributions are rather similar. However, the slightly higher DFE calculated for the ZrO<sub>2</sub>/Zr stack is recognizable as the shift toward higher endurance. Accordingly, a larger increase in endurance is observed with Ti as OE metal. Among the tested combinations, the highest DFE is achieved by the ZrO<sub>2</sub>/Ta, which is in very good agreement with the highest endurance in Fig. 5(a). In most cases, the final endurance failure occurs as RESET failure, leaving the device stuck in LRS, which is in line with the theory of accumulating excessive oxygen vacancies during cycling.

Fig. 5. (a) Statistical evaluation of endurance with different OE metals. Metals with higher oxygen chemical potential increase the DFE and provide higher endurance. (b) Analogously, the electroforming voltage increases with increasing DFE. (c) Median of the logarithmic cycle number linearly increases with the DFE. (d) Forming voltage follows a linear trend with respect to the DFE. Red cross symbols in the box plots represent outliers.

DFE  $E_{\text{form}}$  / eV

$\mathrm{DFE}\,E_{\mathrm{form}}\,/\,\mathrm{eV}$

In addition to the presented cumulative distributions, the median endurance is evaluated for the four material combinations and plotted versus the DFE in Fig. 5(c). It is remarkable that the logarithm of the maximum cycle number describes an exceptionally linear trend regarding the DFE. Thus, the achievable endurance is directly determined by the fabricated material stack, which verifies the theoretical prediction by Guo and Robertson [19] and provides valuable information for device engineering.

Following these results, material combinations with even higher DFE could be utilized to further increase endurance. Exchanging Ta by (for example) W, as suggested in [20],

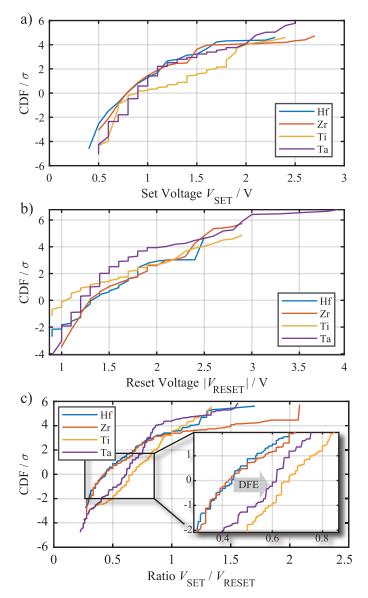

Fig. 6. Cumulative distributions of (a) SET and (b) RESET voltages determined by the programming algorithm to optimize the endurance of the stacks with Hf, Zr, Ti, or Ta as OE. (c) Ratio  $V_{\rm SET}/V_{\rm RESET}$ . The devices with Hf and Zr require slightly higher RESET and lower SET voltages to counteract excessive oxygen vacancy generation due to the low DFE, as highlighted in the inset.

the endurance should be significantly increased. However, Guo *et al.* [19] also predicted an increasing forming voltage  $V_{\text{Form}}$  with increasing DFE. Thus, we evaluated the voltage necessary to form the four material stacks discussed in this work and summarized the forming voltages in Fig. 5(b). Again, the distributions follow the predicted trend. Analogous to the endurance results, the median of  $V_{\text{Form}}$  is plotted versus the DFE in Fig. 5(d). Here, a linear trend is detected. This leads to a tradeoff between exponentially increasing endurance and linearly increasing forming voltage with the DFE, which has to be considered for the ReRAM stack design. Although the endurance can be significantly increased by OE metals with high oxygen chemical potential, this also induces higher forming voltage, which may be suboptimal. In our study,

all devices are fabricated with the same lateral cell size of 7  $\mu$ m. Future studies could also include a variation of the geometries since a further increase of the forming voltage is likely if the cell size is reduced. However, an effect on the switching characteristics after forming is not expected because the conductive filament is believed to be significantly smaller than the lateral cell size [29].

Since the active electrode not only acts as an oxygen scavenging layer but also represents a series resistance, the observed trend of endurance and forming voltage could also be induced by the resistivity of the respective metal. However, typical literature values of the resistivity (at 300 K) are 1.5 n $\Omega \cdot$ m for Ta, 3.6 n $\Omega \cdot$ m for Zr, 11 n $\Omega \cdot$ m for Hf, and 420 n $\Omega \cdot$ m for Ti [30]. Thus, the resistivity cannot account for the observed trends.

Apart from the forming voltage, the SET and RESET voltages required for successful switching are likely to be affected by the DFE. Since both parameters are adjusted by our algorithm for each tested device, a trend may be detectable regarding the four material systems. Thus, cumulative distributions of all occurring SET and RESET voltages separated by the OE material are shown in Fig. 6. The effect of the OE material on the SET and RESET voltages seems to be significantly lower compared to endurance and forming voltage. In general, the required switching voltages are rather similar, which indicates that the resistive switching primarily occurs at the active (Pt) electrode. Nevertheless, the devices with lower DFE and Hf or Zr as OE are observed to require slightly higher RESET voltage and lower SET voltage. The ratio  $V_{\text{SET}}/V_{\text{RESET}}$ , as shown in Fig. 6(c), reveals that the bias determined by the programming algorithm is shifted more toward the RESET direction to counteract the generation of excessive oxygen vacancies. On the one hand, this underlines the effectiveness of the presented algorithm. On the other hand, it supports the conclusion that a high DFE is beneficial to suppress the accumulation of excessive oxygen vacancies and, therefore, enhances the endurance of the ReRAM device.

#### VI. CONCLUSION

All in all, we present a sophisticated endurance algorithm that combines frequent voltage adjustments if necessary with high measurement speed if a device requires fewer adjustments. Thus, reversible endurance failures can be corrected, and the maximum endurance is determined for each device. Furthermore, it is demonstrated that the maximum endurance exponentially increases with the DFE determined by the combination of switching oxide and OE metal. However, the DFE also increases the required forming voltage. We consider these results valuable for ReRAM device engineering and verify the theoretical findings of Guo and Robertson [19].

# REFERENCES

- I. L. Markov, "Limits on fundamental limits to computation," *Nature*, vol. 512, no. 7513, pp. 147–154, Aug. 2014, doi: 10.1038/nature13570.

- [2] R. Strenz, "Review and outlook on embedded NVM technologies—From evolution to revolution," in *Proc. IEEE Int. Memory Workshop (IMW)*, May 2020, pp. 1–4, doi: 10.1109/IMW48823.2020.9108121.

- [3] R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories—nanoionic mechanisms, prospects, and challenges," *Adv. Mater.*, vol. 21, nos. 25–26, pp. 2632–2663, Jul. 2009, doi: 10.1002/adma.200900375.

- [4] J. J. Yang, D. B. Strukov, and D. R. Stewart, "Memristive devices for computing," *Nature Nanotechnol.*, vol. 8, no. 1, pp. 13–24, Jan. 2013, doi: 10.1038/nnano.2012.240.

- [5] H.-S.-P. Wong et al., "Metal-oxide RRAM," Proc. IEEE, vol. 100, no. 6, pp. 1951–1970, Jun. 2012, doi: 10.1109/JPROC.2012.2190369.

- [6] Y. Chen, "Reram: History, status, and future," *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1420–1433, Apr. 2020, doi: 10.1109/TED.2019.2961505.

- [7] M. A. Zidan, J. P. Strachan, and W. D. Lu, "The future of electronics based on memristive systems," *Nature Electron.*, vol. 1, no. 1, pp. 22–29, Jan. 2018, doi: 10.1038/s41928-017-0006-8.

- [8] M.-J. Lee *et al.*, "A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> bilayer structures," *Nature Mater.*, vol. 10, no. 8, pp. 625–630, Aug. 2011, doi: 10.1038/nmat3070.

- [9] M. von Witzleben, T. Hennen, A. Kindsmüller, S. Menzel, R. Waser, and U. Böttger, "Study of the SET switching event of VCM-based memories on a picosecond timescale," *J. Appl. Phys.*, vol. 127, no. 20, May 2020, Art. no. 204501, doi: 10.1063/5.0003840.

- [10] D. J. Wouters, Y.-Y. Chen, A. Fantini, and N. Raghavan, "Reliability aspects," in *Resistive Switching: From Fundamentals of Nanoionic Redox Processes to Memristive Device Applications*, D. Ielmini and R. Waser, Eds. Hoboken, NJ, USA: Wiley, 2016.

- [11] S. Wiefels, C. Bengel, N. Kopperberg, K. Zhang, R. Waser, and S. Menzel, "HRS instability in oxide-based bipolar resistive switching cells," *IEEE Trans. Electron Devices*, vol. 67, no. 10, pp. 4208–4215, Oct. 2020, doi: 10.1109/TED.2020.3018096.

- [12] S. Wiefels, U. Bottger, S. Menzel, D. J. Wouters, and R. Waser, "Statistical modeling and understanding of HRS retention in 2.5 Mb HfO<sub>2</sub> based ReRAM," in *Proc. IEEE Int. Memory Workshop (IMW)*, May 2020, pp. 1–4, doi: 10.1109/IMW48823.2020.9108123.

- [13] G. Sassine et al., "Optimizing programming energy for improved RRAM reliability for high endurance applications," in Proc. IEEE Int. Memory Workshop (IMW), May 2018, pp. 1–4, doi: 10.1109/IMW.2018.8388843.

- [14] C.-W. Hsu et al., "Homogeneous Barrier modulation of TaO<sub>X</sub>/TiO<sub>2</sub> bilayers for ultra-high endurance three-dimensional storage-class memory," *Nanotechnology*, vol. 25, no. 16, 2014, Art. no. 165202, doi: 10.1088/0957-4484/25/16/165202.

- [15] A. Kawahara et al., "An 8 Mb multi-layered cross-point ReRAM macro with 443 Mb/s write throughput," in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 2012, pp. 432–434, doi: 10.1109/isscc.2012.6177078.

- [16] X.-D. Huang, Y. Li, H.-Y. Li, K.-H. Xue, X. Wang, and X.-S. Miao, "Forming-free, fast, uniform, and high endurance resistive switching from cryogenic to high temperatures in W/AlO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub>/Pt bilayer memristor," *IEEE Electron Device Lett.*, vol. 41, no. 4, pp. 549–552, Apr. 2020, doi: 10.1109/LED.2020.2977397.

- [17] Y. Y. Chen et al., "Endurance/retention trade-off on HfO<sub>2</sub>/metal cap 1T1R bipolar RRAM," *IEEE Trans. Electron Devices*, vol. 60, no. 3, pp. 1114–1121, Mar. 2013, doi: 10.1109/TED.2013.2241064.

- [18] Y.-B. Kim et al., "Bi-layered RRAM with unlimited endurance and extremely uniform switching," in *Proc. IEEE Symp. VLSI Techn.*, Jun. 2011, pp. 52–53.

- [19] Y. Guo and J. Robertson, "Materials selection for oxide-based resistive random access memories," *Appl. Phys. Lett.*, vol. 105, no. 22, Dec. 2014, Art. no. 223516, doi: 10.1063/1.4903470.

- [20] W. Kim et al., "Impact of oxygen exchange reaction at the ohmic interface in Ta<sub>2</sub>O<sub>5</sub>-based ReRAM devices," Nanoscale, vol. 8, no. 41, pp. 17774–17781, 2016, doi: 10.1039/C6NR03810G.

- [21] Y. Meng et al., "Fast step-down set algorithm of resistive switching memory with low programming energy and significant reliability improvement," in Symp. VLSI Technol., Dig. Tech. Papers, Jun. 2014, pp. 1–2.

- [22] M. V. Ganduglia-Pirovano, A. Hofmann, and J. Sauer, "Oxygen vacancies in transition metal and rare Earth oxides: Current state of understanding and remaining challenges," Surf. Sci. Rep., vol. 62, no. 6, pp. 219–270, Jun. 2007, doi: 10.1016/j.surfrep.2007.03.002.

- [23] A. S. Foster, V. B. Sulimov, F. L. Gejo, A. L. Shluger, and R. M. Nieminen, "Structure and electrical levels of point defects in monoclinic zirconia," *Phys. Rev. B, Condens. Matter*, vol. 64, no. 22, Nov. 2001, Art. no. 224108, doi: 10.1103/PhysRevB.64.224108.

- [24] A. S. Foster, V. B. Sulimov, F. L. Gejo, A. L. Shluger, and R. M. Nieminen, "Modelling of point defects in monoclinic zirconia," *J. Non-Crystalline Solids*, vol. 303, pp. 101–107, May 2002, doi: 10.1016/S0022-3093(02)00974-2.

- [25] A. Kindsmuller, A. Schonhals, S. Menzel, R. Dittmann, R. Waser, and D. J. Wouters, "The influence of interfacial (sub) oxide layers on the properties of pristine resistive switching devices," in *Proc. Non-Volatile Memory Technol. Symp. (NVMTS)*, Oct. 2018, pp. 1–4, doi: 10.1109/NVMTS.2018.8603115.

- [26] C.-Y. Lin et al., "Effect of top electrode material on resistive switching properties of ZrO<sub>2</sub> film memory devices," IEEE Electron Device Lett., vol. 28, no. 5, pp. 366–368, May 2007, doi: 10.1109/LED.2007.894652.

- [27] C. L. Torre, A. F. Zurhelle, T. Breuer, R. Waser, and S. Menzel, "Compact modeling of complementary switching in oxide-based ReRAM devices," *IEEE Trans. Electron Devices*, vol. 66, no. 3, pp. 1268–1275, Mar. 2019, doi: 10.1109/TED.2019.2892997.

- [28] C. Nail et al., "Understanding RRAM endurance, retention and window margin trade-off using experimental results and simulations," in *IEDM Tech. Dig.*, Dec. 2016, pp. 4–5, doi: 10.1109/IEDM.2016.7838346.

- [29] S. Privitera, G. Bersuker, S. Lombardo, C. Bongiorno, and D. C. Gilmer, "Conductive filament structure in HfO<sub>2</sub> resistive switching memory devices," *Solid-State Electron.*, vol. 111, pp. 161–165, Sep. 2015, doi: 10.1016/j.sse.2015.05.044.

- [30] J. R. Rumble and J. Rumble, CRC Handbook of Chemistry and Physics, 98th ed. Boca Raton, FL, USA: CRC Press, 2017.