## Scalable Control Electronics for a Spin Based Quantum Computer

Lotte Geck

Information

Band / Volume 65

ISBN 978-3-95806-540-6

Forschungszentrum Jülich GmbH Zentralinstitut für Engineering, Elektronik und Analytik (ZEA) Systeme der Elektronik (ZEA-2)

# Scalable Control Electronics for a Spin Based Quantum Computer

Lotte Geck

Schriften des Forschungszentrums Jülich Reihe Information / Information

Bibliografische Information der Deutschen Nationalbibliothek. Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte Bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

Herausgeber Forschungszentrum Jülich GmbH

und Vertrieb: Zentralbibliothek, Verlag

52425 Jülich

Tel.: +49 2461 61-5368 Fax: +49 2461 61-6103 zb-publikation@fz-juelich.de

www.fz-juelich.de/zb

Umschlaggestaltung: Grafische Medien, Forschungszentrum Jülich GmbH

Druck: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2021

Schriften des Forschungszentrums Jülich Reihe Information / Information, Band / Volume 65

D 82 (Diss. RWTH Aachen University, 2020)

ISSN 1866-1777 ISBN 978-3-95806-540-6

Vollständig frei verfügbar über das Publikationsportal des Forschungszentrums Jülich (JuSER) unter www.fz-juelich.de/zb/openaccess.

This is an Open Access publication distributed under the terms of the <u>Creative Commons Attribution License 4.0</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

#### **Abstract**

In the last years, the topic of quantum computing has received increased attention and a rising number of universities, research institutes and companies are exploring it. One reason for that is the great potential to solve some of today's practically intractable mathematical problems. The superiority of quantum computers is based on quantum mechanical effects in the smallest computation unit, the quantum bit (qubit). The operation and readout of these qubits is complex and very sensitive to noise and other disturbances. For a universal, programmable quantum computer qubit numbers in the order of millions need to be operated together which is a great scale up from today's 53 qubits.

For a qubit several different implementations exist and one promising candidate type are qubits made out of semiconductor materials. They typically store information in the spin of localized charge carriers. The manipulation of that spin and the corresponding computation is possible through electrical signals. However, due to the operation requirements of the qubit the electronic-qubit interface is very complex and current control methods are not feasible for large qubit numbers.

The goal of this work is a systematic study of the scalability of integrated control electronics based on existing, industrial complementary metal-oxide-semiconductor (CMOS) technology. Included in this goal is also the identification of potential hindrances to the scalability and necessary subsequent research and the interaction of the electronics with other parts of the quantum computer. In this work, the so called gallium-arsenide S-T qubit is used as a reference and most of the technology parameter values take a 65 nm CMOS process into account.

In a first step, a control concept for the qubits was developed and its scalability judged on the estimated area and power consumption of the integrated circuit. Next to the 65 nm technology parameter values, also extrapolated values for smaller nodes were used. Results show that the main hindrance to scalability is the power consumption of the electronics and in order to scale up to millions of qubits technology advancements are necessary, among others. In the more near term application technologies with low digital supply voltage are promising.

The second step was to derive a behavioral model not only of the electronic control concept but the interface to the rest of the quantum computer and the qubit, as well. Simulations of the complete system show that the electronics concept works as designed and qubit control is possible. The interaction of the different units also highlights that processes critical to the scalability are for example the measurement and the adaption of pulse sequences to each individual qubit.

In order to test the effect of imperfect electronics on the operation a qubit, several exemplary qubit gates and the corresponding voltage pulse sequences were defined. On these gates effects like interferer signals or process variations were tested. For the simulated quality of qubit gates, the outcome is that for high precision computation a co-optimization of pulse sequences and electronics is vital. Thus, a tight interdisciplinary cooperation is advisable. Overall, the developed behavioral model is a good tool for further investigation of scalability issues and electronic-qubit interaction.

#### Contents

| A  | bstra | ct                                                                      | i    |

|----|-------|-------------------------------------------------------------------------|------|

| Li | st of | Figures                                                                 | vii  |

| Li | st of | Tables                                                                  | хi   |

| A  | crony | vms :                                                                   | xiii |

| 1  | Intr  | oduction                                                                | 1    |

|    | 1.1   | Problem at hand                                                         | 2    |

|    | 1.2   | Approach of this thesis                                                 | 4    |

|    | 1.3   | Organization of this work                                               | 6    |

| 2  | Bas   | ics of Quantum Information and Quantum Computing                        | 7    |

|    | 2.1   | The qubit                                                               | 10   |

|    | 2.2   | Multiple qubits                                                         | 12   |

|    | 2.3   | Quality measures for qubits and gates                                   | 13   |

|    |       | 2.3.1 Gate operations                                                   | 13   |

|    | 2.4   | Qubit implementations and their scalability potential                   | 14   |

|    |       | 2.4.1 The GaAs S-T $_0$ qubit                                           | 16   |

|    | 2.5   | State of the Art (scalable) qubit control                               | 21   |

| 3  | Fea   | sibility and scalability of cryogenic control electronics for qubits    | 23   |

|    | 3.1   | Motivation and method                                                   | 23   |

|    | 3.2   | Requirements for qubit operation extracted from current lab experiments | 25   |

|    | 3.3   | Concept for scalable cryogenic control electronic                       | 27   |

|    |       | 3.3.1 Memory                                                            | 29   |

|    |       | 3.3.2 Managing Unit                                                     | 30   |

|    |       | 3.3.3 Bias generation                                                   | 31   |

|    |       | 3.3.4 RF generation                                                     | 36   |

|    |       | 3.3.5 Feasibility conclusion                                            | 37   |

|    | 3.4   | Area and Power estimations                                              | 37   |

|    |       | 3.4.1 DAC area and power                                                | 41   |

|    |       | 3.4.2 Control electronics area and power                                | 43   |

|    | 3.5   | Reduction possibilities of area and power                               | 45   |

|    | 3.6   | Critical discussion of assumptions                                      | 48   |

|    | 3.7   | Scalability Discussion and Conclusion                                   | 49   |

| 4 | Beh | avioral modeling of electronics                  | 53  |

|---|-----|--------------------------------------------------|-----|

|   | 4.1 | Motivation                                       | 53  |

|   | 4.2 | Simulation with Simulink                         | 54  |

|   | 4.3 | Top Level Model                                  | 55  |

|   | 4.4 | QC levels at higher temperatures                 |     |

|   | 4.5 | Control electronics                              | 62  |

|   |     | 4.5.1 Managing unit                              | 62  |

|   |     | 4.5.2 Memory                                     | 69  |

|   |     | 4.5.3 Bias generation                            | 71  |

|   |     | 4.5.4 RF generation                              | 73  |

|   | 4.6 | Readout                                          |     |

|   | 4.7 | Discussion and implications on scalability       | 75  |

|   | 4.8 | Summary                                          |     |

| 5 | Qul | oit Modeling and Characterization                | 79  |

|   | 5.1 | Motivation and Method                            | 79  |

|   | 5.2 | Behavioral modeling of the qubit state           | 80  |

|   | 5.3 | Qubit operation                                  | 82  |

|   |     | 5.3.1 Finding pulse sequences                    | 83  |

|   | 5.4 | Sensitivity                                      |     |

|   |     | 5.4.1 Conclusion                                 | 92  |

|   | 5.5 | Frequency behaviour                              | 92  |

|   |     | 5.5.1 Sinusoidal interference signal             | 92  |

|   |     | 5.5.2 Filter functions                           | 94  |

|   |     | 5.5.3 Summary                                    | 96  |

|   | 5.6 | Noise power influence                            | 96  |

|   |     | 5.6.1 Summary                                    | 98  |

|   | 5.7 | Conclusions and implication for circuit designer | 98  |

| 6 | Mod | deling qubits and electronics together           | 101 |

|   | 6.1 | Motivation and method                            |     |

|   | 6.2 | Modeled non-idealities                           |     |

|   |     | 6.2.1 Jitter                                     |     |

|   |     | 6.2.2 Noise on the reference voltage             |     |

|   |     | 6.2.3 DAC nonlinearities                         |     |

|   | 6.3 | Combined simulation with exemplary pulses        | 105 |

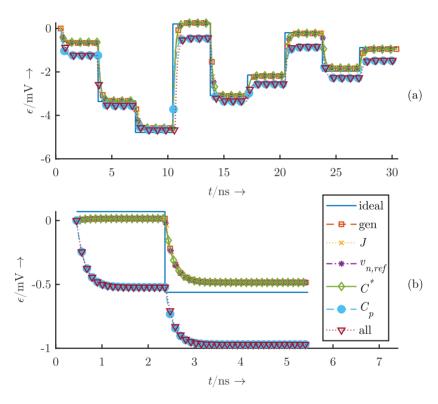

|   |     | 6.3.1 Results                                    | 107 |

|   | 6.4 | Conclusion                                       | 110 |

| 7 | Sun | nmary, Conclusion and Outlook                    | 111 |

|   | 7.1 | Summary                                          |     |

|   | 7.2 | Conclusion                                       | 113 |

| 7.3     | Outlook                             | . 113 |

|---------|-------------------------------------|-------|

| Bibliog | graphy                              | xv    |

| Curric  | ulum Vitae                          | xxvii |

| Publica | ations and additional contributions | xxix  |

| A Esti  | mations block diagrams              | xxxi  |

### **List of Figures**

| 1.1        | of a dilution refrigerator adapted from [6]                                                                                                         | 3  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2        | Approach for electronics placement in the available temperature stages .                                                                            | 5  |

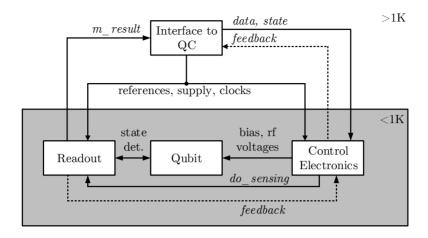

| 1.3        | System concept of qubit and electronic interconnects                                                                                                | 5  |

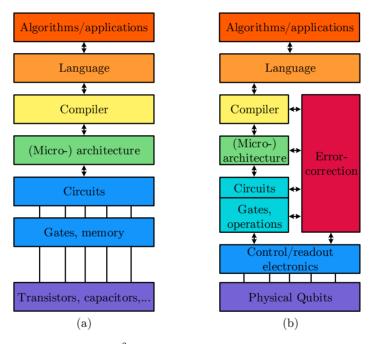

| 2.1        | Levels of abstraction of a (a) classical computer and (b) a quantum computer.                                                                       | 7  |

| 2.2<br>2.3 | Bloch sphere with representation of qubit state $ \Psi\rangle$                                                                                      | 11 |

| 2.4        | potential distribution, (b) principle electrode layout of one double dot GaAs double dot energy diagrams: (a) energy levels only due to charge      | 17 |

| 2.5        | configuration, (b) added spin and tunneling effects (adapted from [57]) . (a) Energy diagram of the logical subspace with state changing parameters | 18 |

|            | and (b) visualization of state changing rotations on the Bloch sphere                                                                               | 20 |

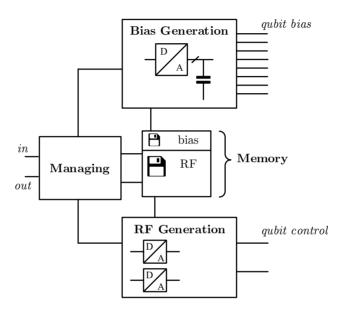

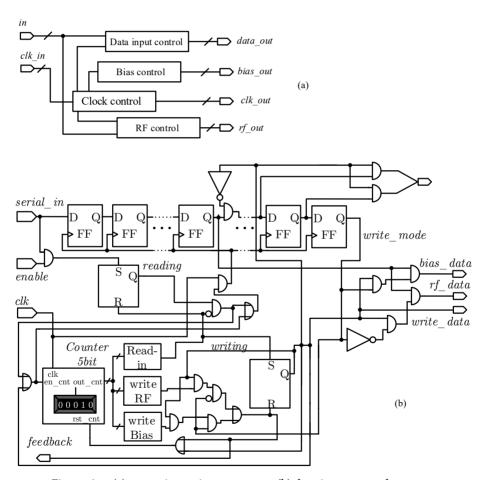

| 3.1        | Electronics system model with its units                                                                                                             | 27 |

| 3.2        | RF data word with composition                                                                                                                       | 28 |

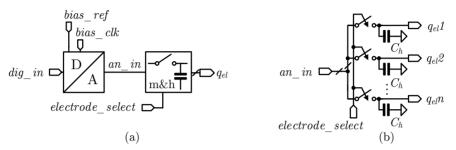

| 3.3        | (a) Bias generation unit and (b) detailed multiplex-and-hold (m&h) subunit                                                                          | 31 |

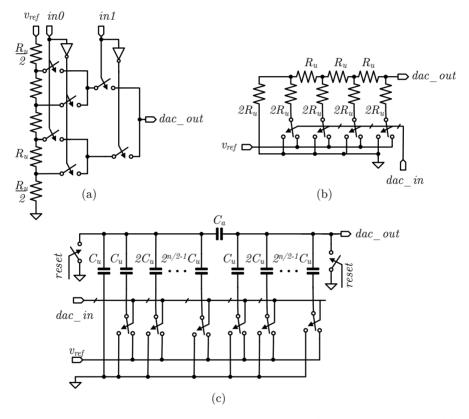

| 3.4        | Circuit architectures of all DAC types considered: (a) Kelvin Divider                                                                               |    |

|            | DAC, (b) Ladder DAC, (c) Capacitive Divider DAC                                                                                                     | 33 |

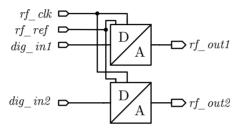

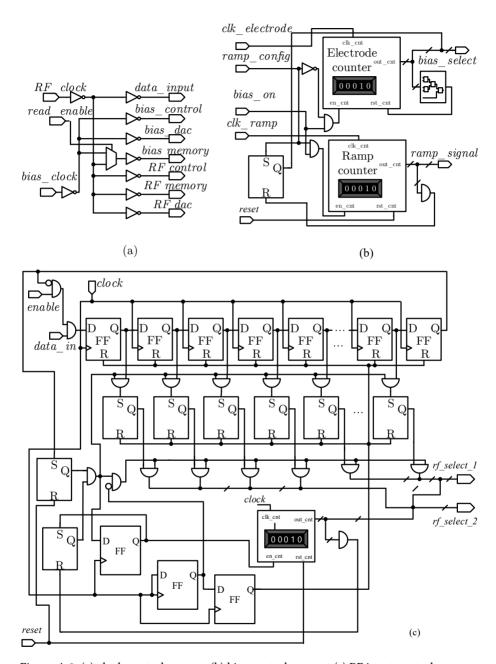

| 3.5        | RF generation model with units                                                                                                                      | 36 |

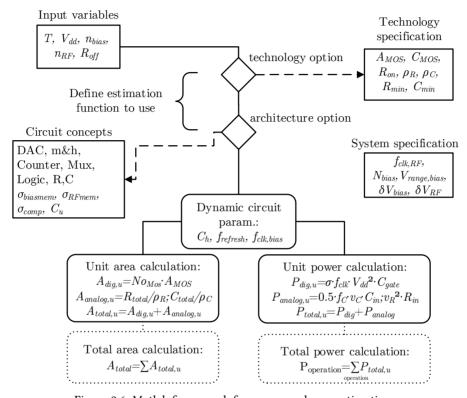

| 3.6        | Matlab framework for power and area estimations                                                                                                     | 39 |

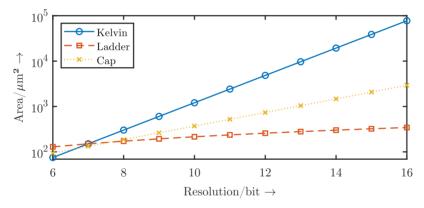

| 3.7        | Area consumption estimation of the different DAC architectures                                                                                      | 41 |

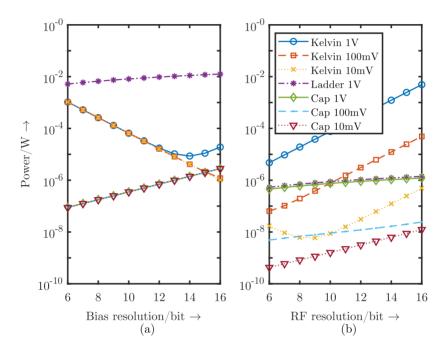

| 3.8        | Power consumption estimation of different DAC architectures                                                                                         | 42 |

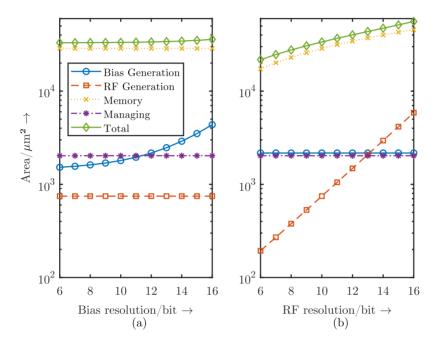

| 3.9        | Area estimation results of the complete system: (a) variable bias resolu-                                                                           |    |

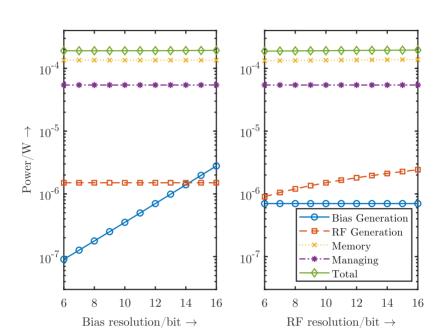

| 3.10       | tion and (b) variable RF resolution                                                                                                                 | 44 |

|            | lution and (b) variable RF resolution                                                                                                               | 45 |

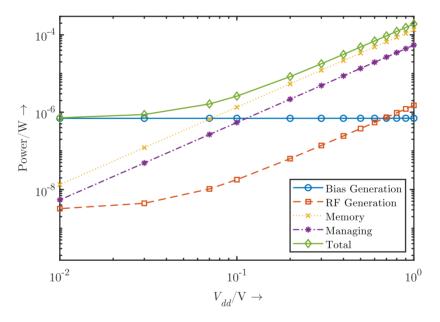

| 3.11       | Power estimation results of the complete system for different digital supply voltages $V_{dd}$                                                      | 47 |

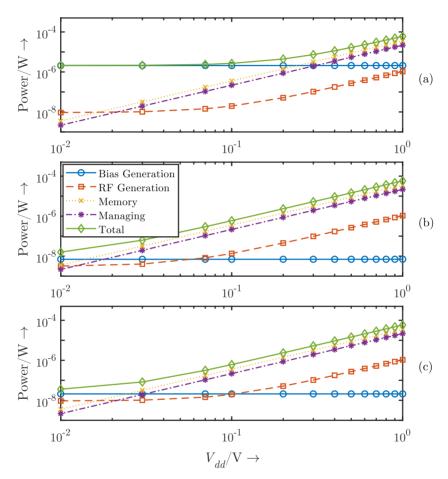

| 3.12       | Power estimation results of the complete system for different digital                                                                               |    |

|            | supply voltages $V_{dd}$ with technology parameters for advanced nodes                                                                              | 50 |

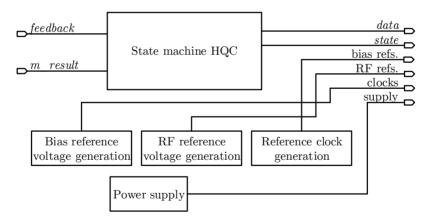

| 4.1<br>4.2 | Behavioral model structure with temperature stages                                                                                                  | 56 |

|            | enced to as HQC                                                                                                                                     | 58 |

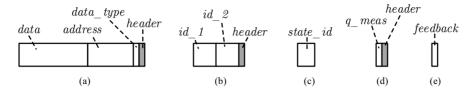

| 4.3        | measurement, (e) feedback                                                                                                                           | 60 |

|            | • •                                                                                                                                                 |    |

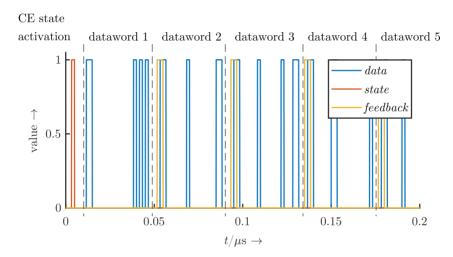

| 4.4  | Simulation results for data transfer from the HQC (data and state) to the                                     |     |

|------|---------------------------------------------------------------------------------------------------------------|-----|

|      | control electronics memory (feedback)                                                                         | 60  |

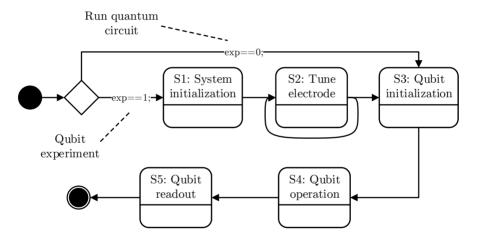

| 4.5  | UML state flow of the HQC state machine                                                                       | 61  |

| 4.6  | Progression of the HQC state machine over time                                                                | 62  |

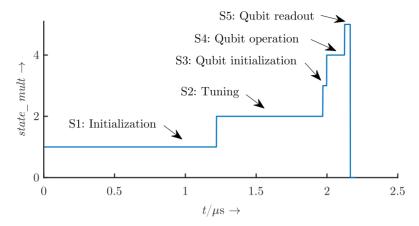

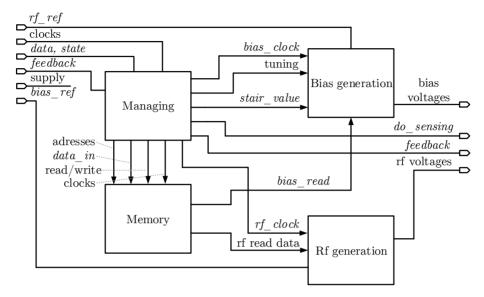

| 4.7  | Structure of the control electronics with internal signals                                                    | 63  |

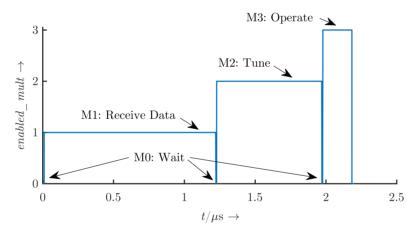

| 4.8  | UML state flow for the state machine in the managing unit                                                     | 63  |

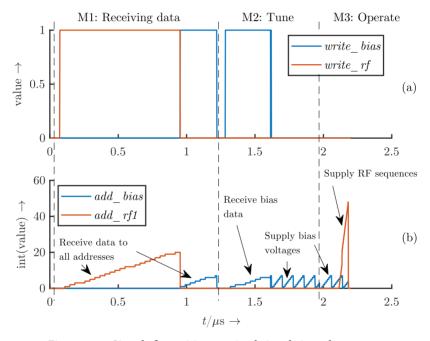

| 4.9  | Progression of the managing unit state machine over time                                                      | 64  |

| 4.10 | Signals for writing received signals into the memory                                                          | 65  |

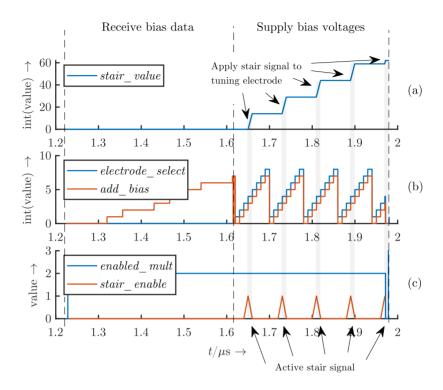

| 4.11 | Relevant signals during tuning in state M2                                                                    | 68  |

| 4.12 | Model concept for qubit operation                                                                             | 68  |

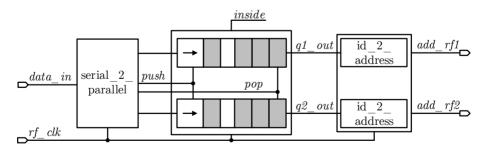

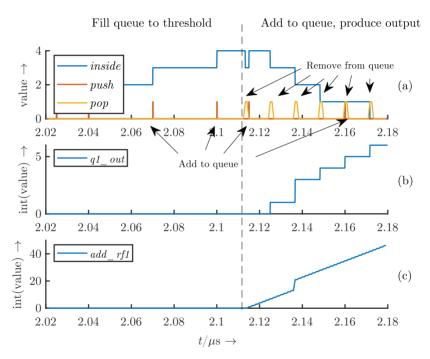

| 4.13 | Relevant signals for qubit operation of the queue in M3                                                       | 69  |

| 4.14 | Memory                                                                                                        | 70  |

| 4.15 | Bias generation mode                                                                                          | 71  |

| 4.16 | Bias generation signals                                                                                       | 72  |

| 4.17 | Model of the RF generation unit                                                                               | 73  |

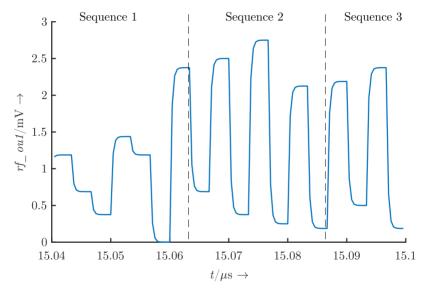

| 4.18 | One output signal of the RF generation unit with indicated sequence                                           |     |

|      | borders                                                                                                       | 74  |

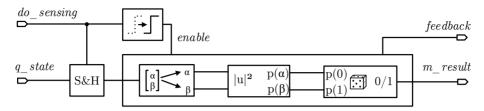

| 4.19 | Readout behavioral model including measurement                                                                | 76  |

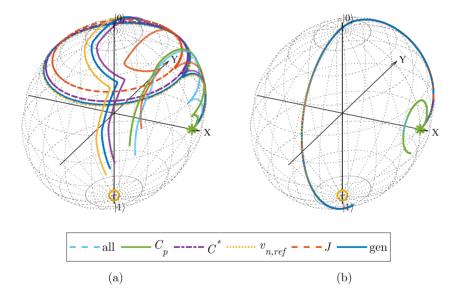

| 5.1  | Rotation of an angle $\delta = \frac{\pi}{2}$ around the y-axis in the Bloch sphere                           | 82  |

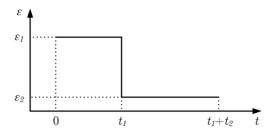

| 5.2  | Concept of pulse sequence for any rotation defined by four variables $t_1$ ,                                  |     |

|      | $t_2$ , $\epsilon_1$ and $\epsilon_2$                                                                         | 84  |

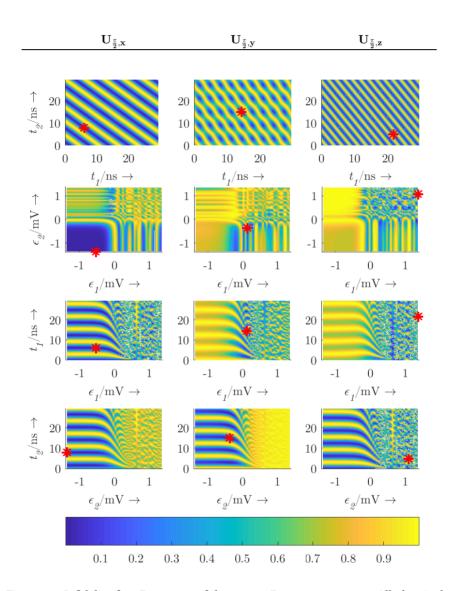

| 5.3  | Infidelity for 2D extracts of the swept 4D parameter space                                                    | 86  |

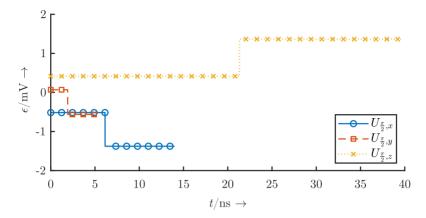

| 5.4  | Optimized voltage signal progression for $\frac{\pi}{2}\text{-rotations}$ around different axis               | 88  |

| 5.5  | Bloch sphere representations of the found gate solutions                                                      | 89  |

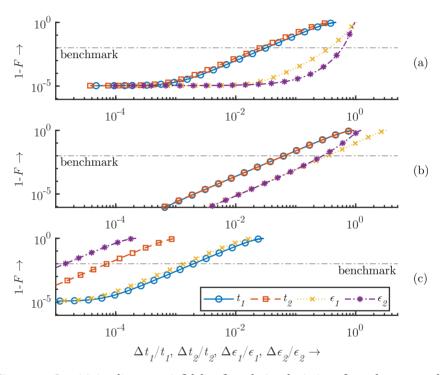

| 5.6  | Sensitivity diagrams: infidelity for relative deviations from the norm value for all gates and all parameters | 90  |

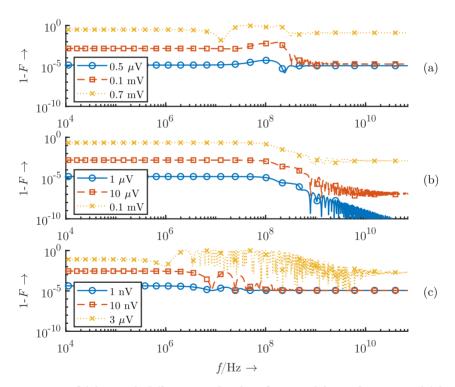

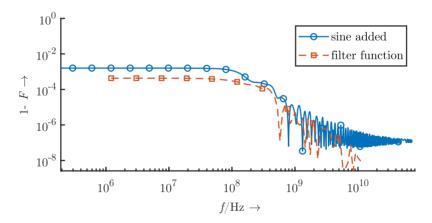

| 5.7  | Infidelity with differing amplitudes of sinusoidal interfering signal                                         | 93  |

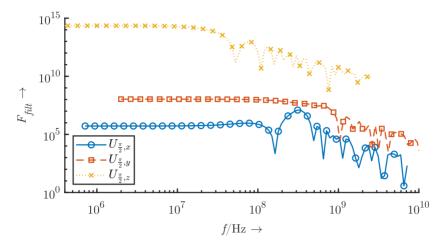

| 5.8  | Filter functions $F_{filt}$ that are used to describe the frequency noise filtering                           | 93  |

| 3.0  | behaviour of the different qubit gates $\dots \dots \dots \dots \dots$                                        | 95  |

| 5.9  | Comparison of the infidelity $1-F$ vs frequency as simulated with a simu-                                     | 73  |

| 3.9  | lation using the filter function                                                                              | 95  |

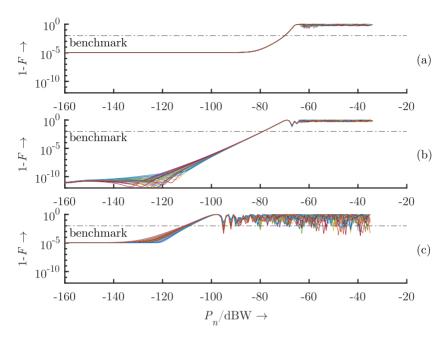

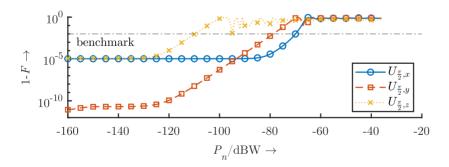

| 5.10 | Infidelity of all gates for different white noise powers $P_n$ and different                                  | /3  |

| 3.10 | white noise seeds                                                                                             | 97  |

| 5.11 | Mean infidelity of all gates vs. the white noise power level $P_n$                                            | 97  |

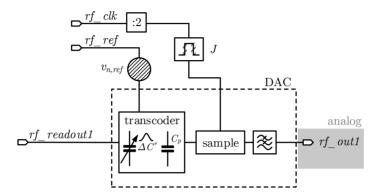

| 6.1  | RF generation model with non-idealities                                                                       | 102 |

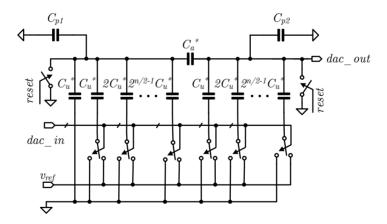

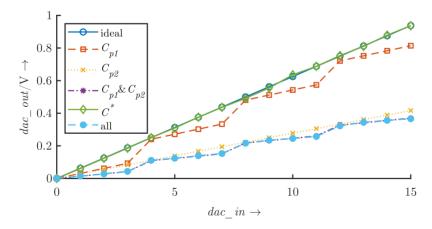

| 6.2  | Concept of DAC nonlinearities                                                                                 | 103 |

| 6.3  | Transfer characteristic of a 4 bit DAC                                                                        |     |

| 6.4  | Theoretical 'ideal' signals as programmed into the source                                                     |     |

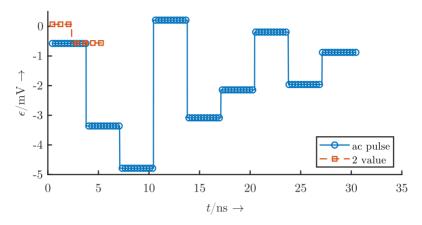

| 6.5  | Signals in the ideal form 'none' and simulated through the RF generation                                      |     |

|      | part 'gen' as well as with additional impairments                                                             | 108 |

| 6.6 | Bloch spheres after simulation of the RF generation generation and different added impairments                                           |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|

|     | (a) managing unit components (b) data input control concept xxxi (a) clock control concept (b) bias control concept (c) RF input control |

|     | conceptxxxii                                                                                                                             |

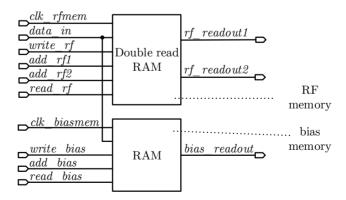

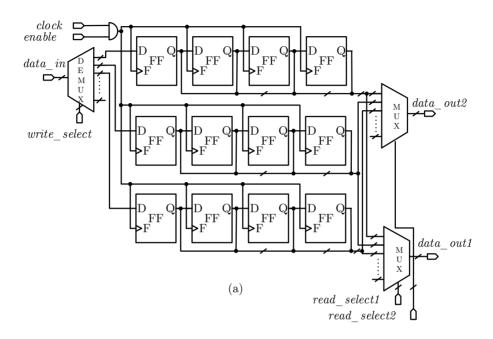

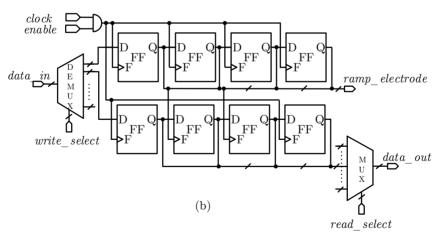

| A.3 | Memory concept (a) RF memory (b) bias memory xxxiii                                                                                      |

#### **List of Tables**

| 2.1 | Summary of the most promising scalable qubit candidates and their best achieved properties | 16  |

|-----|--------------------------------------------------------------------------------------------|-----|

| 3.1 | Summary of current set of system specifications                                            | 26  |

| 3.2 | Minimum necessary connections to electronics from outside for one qubit                    | 28  |

| 3.3 | Parameter of suitable DAC types dependent on the resolution $n$                            | 35  |

| 3.4 | Parameters used for area and power estimation for the 65 nm CMOS                           |     |

|     | technology extracted from room temperature models                                          | 38  |

| 3.5 | Area and power consumption for different technology and architecture                       |     |

|     | options included in the model                                                              | 46  |

| 3.6 | Controllable number of qubits, as limited by the power consumption, for                    |     |

|     | different environment, architecture and and technology settings                            | 51  |

| 4.1 | Parameters for the simulation/model and the corresponding variables of                     |     |

| 7,1 | Chap. 3                                                                                    | 57  |

|     | Спир. 3                                                                                    | 57  |

| 5.1 | Parameter values found through numeric optimization with reached                           |     |

|     | infidelity                                                                                 | 87  |

| 5.2 | Infidelity values for 1% deviations of the norm values of one parameter                    |     |

|     | for the different gates and parameters                                                     | 91  |

| 5.3 | Maximum relative deviation from the norm value for each parameter for                      |     |

|     | $1 - F = 10^{-2}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $         | 92  |

| 5.4 | Maximum possible white noise power level for fault tolerance $(1 - F = 10^{-2})$           | 98  |

| 5.5 | Specification summary for every gate and all gates together, for each                      |     |

|     | effect to stay below $1 - F = 10^{-2}$                                                     | 99  |

| 6.1 | Parameter values of non-idealities                                                         | 102 |

| 6.2 |                                                                                            | 106 |

| 6.3 | Infidelity values for the signals produced by the RF generation 'gen' with                 |     |

|     | several added non-idealities                                                               | 107 |

#### **Acronyms**

$\epsilon_0$  voltage-exchange interaction fit constant

2DEG two-dimensional electron gas AlGaAs aluminum-gallium-arsenide

ASIC application-specific integrated circuit

**AWG** arbitrary waveform generator

CE control electronics

CMOS complementary metal-oxide-semiconductor

**CNOT** controlled-not

**DAC** digital-to-analog converter

DC direct current

DNP dynamic nuclear polarizationFPGA field-programmable gate array

GaAs gallium-arsenide

HDL hardware description language

**HQC** higher levels of the quantum computer

IC integrated circuit

**ID** identifier

LHC Large Hadron Colliderm&h multiplex-and-holdMIM metal-insulator-metal

**NISO** noisy intermediate-scale quantum

**PCIe** peripheral component interconnect express

**pdk** physical design kit

**QAM** quadrature amplitude modulation

QC quantum computer QEC quantum error correction

**qubit** quantum bit

**RAM** random-access memory

RF radio frequency

RMS root mean square

RSA Rivest-Shamir-Adleman

RT room temperature

S singlet

s&hsample-and-holdSHFsuper high frequencySiGesilicon-germaniumSOIsilicon-on-insulator

**SPICE** Simulation Program with Integrated Circuit Emphasis

**SRAM** static random-access memory

T triplet

UML Unified Modeling Language

**VHF** very high frequency

VLSI very large-scale integrationwgn white gaussian noise

Chapter

#### Introduction

Quantum computing research is a topic of increasing popularity. The reason is the large variety of proposed use cases for a universal quantum computer with a potential high impact on research, economy and thus society. In this case 'universal' describes the ability of the quantum computer to be application unspecific and programmable to solve different problems. Example use cases in which quantum computer show superior performance in comparison to classical computers are quantum chemistry, quantum communication, cryptography, big data and optimization problems.

Quantum chemistry, for example, analyzes reaction properties of atoms and molecules on the basis of their quantum mechanical structure. The simulation is an intractable problem for a classical computer but can be done on a quantum computer [1]. The insights resulting from the simulation would not only have an impact on theoretical chemistry and material research but could influence whole economy branches. For example, chemical reactions like fertilizer synthesis, which consumes a few percent of the earth's electrical power, could be optimized [2] and the power consumption reduced.

In the communication sector, as another example, quantum computers have different potential applications. One is the so-called quantum network or quantum internet [3]. A quantum network could be used for distributed computing or secure communication. An advantage of the communication in quantum networks is that the quantum processor requires only a very low complexity. Thus, such a network could be implemented even if a universal quantum computer has not been realized yet. While quantum computers can establish secure communication channels, another use case of them is to crack encryptions based on standard algorithms used in classical computing.

In general, all of the potential applications of the universal quantum computer are based on the fact that there exist specific quantum algorithms for that specific problem. These algorithms employ the unique abilities of the quantum computer to solve the problems much faster. Indeed, they can potentially solve it exponentially faster such that practical intractable problems become solvable. Quantum algorithms exist for a range of problems, but not for everything. For example, there are also classical encryption algorithms that a quantum computer cannot crack. In theory a quantum computer could also run a classical

algorithm. However, due to the large overhead needed the execution would probably be even slower than on a classical computer. Research concerning the realization of quantum computers is done in wide range of topics such as algorithms, general theory, computer architecture, software and error correction and different qubit implementations.

The hardware necessary for a universal quantum computer able to run relevant algorithms is in the range of at least tens of millions of basic processing units [4] in addition to the classical backbone electronics required for any computational system. The basic processing units are called qubits, work as systems with quantum mechanical properties and need to be individually controlled.

The highest number of operational qubits reported on one chip is currently 53, with an implementation of so-called superconducting qubits [5]. Comparing this number with the millions of qubits necessary for a quantum computer makes it clear that a massive scale up is required. As the qubits need to be controlled and read out individually by currently unique signals, research effort is needed to realize scalable control and readout of many qubits.

#### 1.1 Problem at hand

The work of this thesis contributes to the goal of implementing an innovative scalable electrical scheme to control a large number of qubits, i.e. up to millions of qubits. Challenges to this goal are the operating requirements of the qubits and the resulting limited access paths for the around 10 control signals per qubit. The quantum mechanical properties of the qubits relevant to this work are only observable at temperatures of maximum a few Kelvin but ideally below 1 Kelvin<sup>1</sup>. In practice this kind of temperature is usually produced by a dilution refrigerator that uses a mixture of helium isotopes to reach these cryogenic temperatures.

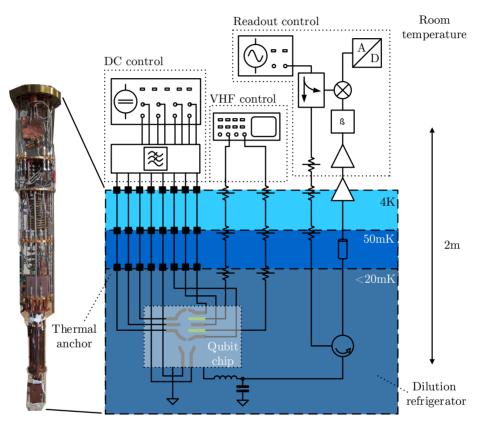

A standard dilution refrigerator is in total more than 1.5 m high and includes different chambers with varying temperatures, pressures and gases. The temperature in the fridge is mostly not distributed continuously but in discrete steps allocated to the different chambers. Thus, the temperature can also be used to identify an area or chamber of the fridge, here also referred to as stage. Interfacing qubits at the lowest temperature stage from the outside at room temperature is an intricate challenge. In nearly all current experiments all measurement and supply equipment is located outside of the fridge and connected to the qubit via, among others, coaxial cables. An example of such a wiring scheme for one qubit is shown in Fig. 1.1. The transmission of a high quality signal is non-trivial, not only because of the long distance, but also because of additional elements

<sup>&</sup>lt;sup>1</sup>One type of qubits utilizing ion traps can be operated at room temperature, but as their scalability potential is low they are not relevant here.

Figure 1.1: Experimental setup with wiring concept and section of inside structure of a dilution refrigerator adapted from [6]. Three different control parts are depicted for direct current (DC) voltages, very high frequency (VHF) signals and readout

.

in the signal path like attenuators, thermal anchors and amplifiers. These elements are necessary to transport a viable electrical signal across such an immense temperature difference, but they are also a potential source of delay and signal distortion.

For most of the current experiments these challenges are manageable with high quality room temperature equipment and a reasonable number of cables. The setup allows detailed research of the qubit properties precisely and flexibly. However, with increasing numbers of qubits and the goal of millions of qubits in mind, this approach reaches its limits at the latest for 1000 qubits. The heat load of the cables is increasingly relevant, as the cooling power of the fridge is at maximum only a few mW at the coldest stage. The diameter of the cables introduces problems as well. On one hand the fridge size is limited and on the other hand the qubit size of  $< 1\,\mu m$  leads to a highly complex wiring challenge for the fanout to the connecting cables. In addition to that the qubits require very precise VHF (several 100 MHz) or even super high frequency (SHF) control signals ( $\geq$  3 GHz). This gives rise to issue like crosstalk and data throughput considerations.

#### 1.2 Approach of this thesis

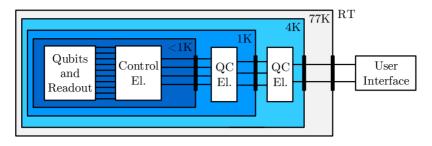

In this work the approach to overcome the mentioned challenges is to use integrated circuits (ICs) and especially application-specific integrated circuits (ASICs) close to the qubits. A systematic study or implementation of such a control setup has not been done yet. The approach here transfers electrical functionality into the direct vicinity of the qubit which reduces the number of cables and the data throughput coming from circuits working at room temperature (RT). Fig 1.2 shows the concept that places the control electronics with the qubits at the coldest stage of the dilution refrigerator. Next to the control electronics at the lowest temperature stage, further electronics are depicted at higher temperature stages in the fridge. As a quantum computer is expected to have more classical electronics than the qubit control electronics, these are included in the concept. Since the power budget at the lowest temperature is extremely limited the additional electronics are envisioned to be placed at higher temperatures.

To place the electronics as close to the qubits as possible, without being on the same chip, the qubit and the electronics wafer have to be bonded together. The idea is to match electronics area and mean qubit footprint and use microfabricated interconnects between electronics and qubits, as sketched in Fig. 1.3. These interconnects are envisioned to be small enough in diameter to fit into the footprint matched to the electronics. Through this the issue of connecting many coaxial cables to the small qubits is circumvented as only few signals have to be transferred to higher temperatures.

While this approach addresses two major pitfalls of increasing qubit numbers, it brings challenges with it as well. To match electronics area and qubit footprint a very limiting

Figure 1.2: Approach for electronics placement in the available temperature stages

Figure 1.3: System concept of qubit and electronic interconnects

area restriction is given for the electronics. The area of spin qubits is below  $1 \,\mu\text{m}^2$ , even if in today's device layouts a large area for pads and fanout has to be added to that. Qubits have to interact with each other to function as a quantum computer, so a placement in the direct vicinity of other qubits is ideal. Since this area is much to small for electronics with relevant functionality, the qubits have to be moved away from each other without impeding their ability to interact with each other. Current research into long distance coupling of qubits makes a distance of  $10 \,\mu\text{m}$  seem to be possible in the future [7–9].

Next to the area the power consumption of the electrical circuits is critical. Most of the power consumed by the electronics is dissipated as heat. At the same time, the qubit operating temperature should not be increased, therefore the power consumption of the electrical circuit has to be smaller than the available cooling power of the fridge. The cooling power of a few mW at the mK stage is enough for a low number of qubits, but very challenging for many qubits. For example, for 1000 qubits the power budget is only a few  $\mu W$  per qubit control circuit and a few nW for 1 million qubits.

Another issue at low temperatures is the behaviour of electrical circuits. The Simulation Program with Integrated Circuit Emphasis (SPICE)-based models used to design circuits are not valid at cryogenic temperatures. While it has been shown that standard bulk complementary metal-oxide-semiconductor (CMOS) technologies at nodes <90 nm work quite well at cryogenic temperatures [10], correct and detailed models are essential for

high performance circuit design. The models for temperatures in industrial applications have to be adapted to be accurate for cryogenic temperatures. This characterization is still in the early stage for the technology at hand.

An additional element of uncertainty regarding control electronics for spin qubits is the ongoing research on qubits. New aspects and insights on how to best control qubits are continuously gained which changes the requirements of the electronics. Coupled with the fact that up to now very high-quality and high-performance equipment has been used, a fixed minimum requirements specification is not available.

To overcome the uncertainty issues of the approach this work is done through high level modeling. With system modeling a flexible tool is created to explore options which can be adapted to changing requirements. In addition to that such a model is suited to analyze the feasibility of the approach with less effort than a full ASIC implementation.

The complete system model also has advantages for verification, since no operational qubit is at hand. First verification and tests of component designs can be done with the model.

#### 1.3 Organization of this work

In this work a new and detailed concept of scalable control electronics for spin qubits is developed and tested. Next to the control electronics themselves also the interfacing components have been included, resulting in a complete system model. Chapter 2 gives the reader necessary basics of quantum computing in general and a brief overview of qubit technologies. Chapter 3 discusses the specifications of control electronics and contains the feasibility analysis of the presented concept. On top of that an extensive discussion of the scalability is done. In chapter 4 a behavioral model of the qubit control electronics and the surrounding components is developed. Analogous to that in chapter 5 a model of the qubit is established. In chapter 6 these both model parts are combined together, and chapter 7 draws a conclusion.

# Chapter 2

## **Basics of Quantum Information and Quantum Computing**

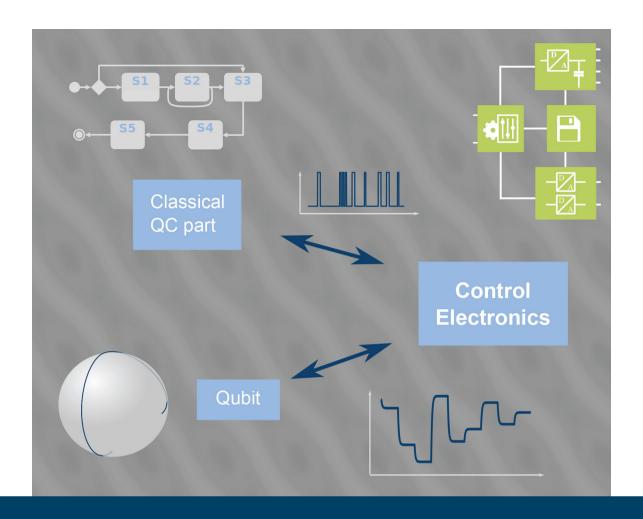

Figure 2.1: Levels of abstraction<sup>2</sup> of a (a) classical computer and (b) a quantum computer.

This chapter introduces the concepts necessary to understand the later parts of this work. For the interested reader publications such as [11–14] are recommended to get more involved with the topic of Quantum Computers and Quantum Information. On top of that [15] reports on an overview of current scientific results on all levels of quantum computer research.

The idea of a quantum computer (QC) is already regularly mentioned in the mainstream media, but seldom statements are made on how non-experts in the field can picture and understand such a computer. While the specific details of a QC are naturally still unclear, a direct comparison to a classical computer gives a perhaps more accessible picture of how a quantum computer could look like. Fig. 2.1 shows a 'levels of abstraction' depiction of a classical computer on the left and a possible well suited one for a quantum computer on the right. A lot of components of the classical computer find their equivalent in the quantum computer, but some parts are different, especially in the lower levels. The equivalent parts in the quantum computer not only have the same functionality as the ones in the classical computer, but their hardware is classical as well. Therefore, a quantum computer will consist in large parts of classical logic.

The topmost level for both computers is the algorithm and applications level. While a classical computer can only run classical algorithms, a quantum computer could run classical and quantum algorithms. As the classical algorithms do not utilize the unique hardware properties of the QC, no advantage would be gained, as mentioned in already in Chap. 1. One example of a quantum algorithm is Shor's algorithm, which may be used to efficiently factorize large numbers into their primes. The impact of the runtime difference to the best classical algorithm is emphatically shown with the time it takes to factorize a 2048 bit number into its primes. The Tianhe-2 supercomputer [16] would need about 100 years to achieve the factorization, while a quantum computer could complete the calculation in roughly 8 hours [17]. The significant reduction in calculation time is relevant, since the current Rivest-Shamir-Adleman (RSA) encryption is based on the computational difficulty of prime factorization [11]. As a quantum computer could crack this encryption, standardization of quantum computer safe algorithms is underway [18].

Research on the software and micro-architecture parts of the quantum computer, which are similar to their corresponding classical computer versions, is varied. It reaches from object-oriented high-level languages like QCL, Q#, Qlanguage, OpenQL to lower level languages like Quantum pseudocode and instruction sets like Quil, OpenQASM, and QUISA. On top of that there are several software development kits like ProjectQ, Qiskit, Forest, Quantum development Kit, and Cirq available. A complete review or listing of the different projects does not exist, but some well advanced collections can be found in [15, 19–21]. So far, no package or language could clearly establish themselves as a quasi standard.

The next lower levels of circuits and gates in Fig. 2.1 also exist in both computer versions. For the quantum computer these levels are directly connected because no distinct hard-

<sup>&</sup>lt;sup>2</sup>Among others, depicting levels of abstraction is a method used in computer science and software engineering where the same object, or principle is depicted with different amounts of abstraction. The top level usually provides the most abstraction while the lowest level includes the most details.

ware representing circuits exists. Circuits are established through actions on the basic units, as the most basic processing unit is a memory element as well.

The combination of memory and processor element leads to a completely different mode of operation compared to the classical computer, where sets of transistor basic units are hard-wired together to provide one specific logical function. The operations in a quantum computer are variable and as such a set of basic units can perform different logical operations, as explained in more detail in Sec. 2.1. There is only one basic processing unit in a quantum computer, called the quantum bit (qubit). The combination of memory and processing capability in a quantum processor makes the classical Von-Neuman architecture with separated memory and processing obsolete. In its place new gate-defined quantum architectures have been established [4, 22–24]. Another consequence of the nonexistence of dedicated long life memory elements up to now is that no working memory or hard drive<sup>3</sup> exist in QCs. All information to be stored must be kept in classical electronics [15].

The construction of logic operations from actions on the processing unit has a significant disadvantage which is represented by the additional layer of control/readout electronics in Fig. 2.1b. This layer contains complex electronic circuits, which are needed to operate the basic processing units in the lowest level. The basic units in a classical computer are transistors, capacitors and so forth, but a quantum computer has only the one type of unit, the qubit. While classical logic mainly needs a power supply, a reference clock and decent quality input signals, qubit operation is much more demanding. Depending on the qubit implementation it requires for example several very stable DC voltages and in addition to that VHF or SHF control signals or even lasers (Sec. 2.1).

Next to the way of implementing circuits and the operation of the qubits, the error correction is a deciding difference between quantum and classical computers (Fig. 2.1). Large-scale quantum computation is heavily dependent on quantum error correction (QEC) for several reasons. First, the error rate of the qubits [25] currently is mostly around  $10^{-1}$  to  $10^{-2}$  with some exceptions in the range of  $10^{-4}$ . Second, correcting errors in a quantum computer is much more complex than in classical electronics. Typical classical correction schemes involve copying and comparing states, which are actions that are fundamentally impossible in quantum mechanics. On top of that the errors in qubits are continuous, rather than discrete as in classical logic. These issues highlight the difficulties for QEC and explain the necessity of extensive error correction [26] on several levels of the QC. A currently popular QC code is the so-called surface code [27]. One advantage of this code is that only neighboring qubits have to be able to interact. Other codes require possible coupling of each qubit to every other qubit which is difficult to implement in hardware. Another advantage of the surface code is its fault tolerance, if the qubit's error rate is under a certain threshold. Here fault tolerance describes the code's ability to correct both the original error and the possible error introduced through

$<sup>^3</sup>$ So far, no method to preserve qubit states without a constant power supply has been found.

the correction mechanism. The threshold error rate of the surface code is the subject of ongoing research, but has been estimated to be  $1\,\%$  [27, 28]. However, the models which contributed to this number include several simplifying assumptions. The impact of these simplifications is not yet clear, so the 1% threshold is more a minimum requirement on the quality of the qubits.

#### 2.1 The qubit

The qubit is the most basic unit of a quantum computer and the term is used both for the unit of information and for the technical realization containing such information. In this work, the term 'qubit' refers to the physical implementation while the information is referred to as 'state of the qubit'.

In general, the state of a qubit corresponds to the state of a two-level quantum mechanical system. The levels are encoded into  $|0\rangle$  and  $|1\rangle$ , similar to the classical bits 0 and 1. In the quantum computing community the state of a qubit is then given by:

$$|\Psi\rangle = \alpha|0\rangle + \beta|1\rangle, \quad \alpha, \beta \in \mathbb{C}.$$

(2.1)

Eq. 2.1 is written in the so-called bra-ket notation. It has advantages when expressing quantum mechanical operators, but the same equation can also be written in a standard vector notation:

$$\vec{\Psi} = \alpha \vec{e_1} + \beta \vec{e_2}, \quad \alpha, \beta \in \mathbb{C}. \tag{2.2}$$

In this case  $\vec{e_1}$  and  $\vec{e_2}$  are perpendicular basis vectors of the state space of  $\vec{\Psi}$  (Hilbert space of the qubit) and a state is the result of a vector addition. This vector addition is the foundation of the superposition property of the state of one or several qubits. The state cannot only be  $|0\rangle$  or  $|1\rangle$  but can be a bit of both at the same time. The amplitudes of the basis vectors determine the amount of superposition of  $|0\rangle$  and  $|1\rangle$  and are normalized to

$$|\alpha|^2 + |\beta|^2 = 1. {(2.3)}$$

The amplitudes  $\alpha$  and  $\beta$  play an important role in the readout of a qubit state as well. A state can only be measured in one of the basis vectors of the state space. This means that the measurement projects the superposition state onto one of its (measurement) bases, thus destroying the superposition. This implicates that a measurement destroys the quantum mechanical property of the qubit state. The result of the measurement can only be either 0 or 1 and is not deterministic. The probability p of measuring either 0 or 1 from the same state is given by  $p(0) = |\alpha|^2$  and  $p(1) = |\beta|^2$ .

The 4-dimensional state space of a qubit can be projected onto a 2-dimensional space to make a visualization possible. Here, this 2-dimensional space is the surface of the so called Bloch sphere, as shown in Fig. 2.2. The Bloch sphere representation ignores a non-observable global phase and rewrites the qubit state as<sup>4</sup>:

$$|\Psi\rangle = \cos\left(\frac{\theta}{2}\right)|0\rangle + e^{i\varphi}\sin\left(\frac{\theta}{2}\right)|1\rangle, \text{ with } \varphi, \theta \in \mathbb{R}.$$

(2.4)

Figure 2.2: Bloch sphere with representation of qubit state  $|\Psi\rangle$ .

The change of the state of a qubit is described by a unitary transformation applied to a starting state  $|\Psi_0\rangle$ :

$$|\Psi\rangle = U |\Psi_0\rangle,\tag{2.5}$$

where U is a unitary matrix and  $|\Psi\rangle$  the resulting state. The most similar corresponding action in a classical computer is to perform a classical logic gate.

On the Bloch sphere the unitary transformation corresponds to a movement on the surface of the sphere. For example, the rotation of a state around one axis by an angle of  $\rho$  can be achieved with well-known rotation matrices, as written in Eq. 2.6. Further, the so-called Pauli matrices (Eq. 2.7) describe the rotation around one axis by an angle of  $\pi$ . The difference to a corresponding rotation matrix with the same angle is only a global phase of  $\pi$ .

$$R_{x,\rho} = \begin{pmatrix} \cos\frac{\rho}{2} & -i\sin\frac{\rho}{2} \\ -i\sin\frac{\rho}{2} & \cos\frac{\rho}{2} \end{pmatrix} \quad R_{y,\theta} = \begin{pmatrix} \cos\frac{\rho}{2} & -\sin\frac{\rho}{2} \\ \sin\frac{\rho}{2} & \cos\frac{\rho}{2} \end{pmatrix} \quad R_{z,\rho} = \begin{pmatrix} e^{-i\rho/2} & 0 \\ 0 & e^{i\rho/2} \end{pmatrix} \quad (2.6)$$

<sup>&</sup>lt;sup>4</sup>Note that in this work *i* indicates the imaginary unit.

$$\sigma_x = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix} \quad \sigma_y = \begin{pmatrix} 0 & -i \\ i & 0 \end{pmatrix} \quad \sigma_z = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}$$

(2.7)

#### 2.2 Multiple qubits

A quantum computer is not only made of single unrelated qubits but is a large system of a high number of qubits which have to interact with each other. The state of multiple qubits together can be calculated with using the tensor product  $\otimes$

$$|\Psi\rangle = |\Psi_1\rangle \otimes |\Psi_2\rangle,$$

(2.8)

with the single qubit states  $|\Psi_n\rangle$ . Thus, the dimension of the state vector of n>0 qubits is  $2^n\times 1$  and the dimension of a gate matrix U is  $2^n\times 2^n$ , which describes the number of possible basis states. The exponential increase in states with additional qubits can be seen as one of the reasons why a quantum computer can be more powerful than a classical one. With each qubit the information content is increasing exponentially. On top of that it is one of the reasons why even supercomputers struggle to simulate qubit numbers over 40. The number is heavily dependent on the computer and the complexity of the quantum mechanical model.

While the Bloch sphere is used to visualize single qubit gates no such well known way exists for multi-qubit states. The state of multi-qubits can be calculated from the individual states, but the reverse is not always true. There are possible multi-qubit states which cannot be separated into single qubit states, which still fulfill the normalization in Eq. 2.3. Since the decomposition into separate individual qubit states is not possible this implies that the single qubit states are dependent on each other. This is called entanglement and is another deciding feature of the quantum computer next to the superposition. Entanglement is so powerful because if n qubits are entangled the state of only one has to be changed to affect the state of all of them. This can be imagined similarly to parallel computation on n cores but with the computational effort of only one core.

An entangled state of several qubits is achieved through multi-qubit operations. A multi-qubit operation works analogously to a single qubit operation as detailed in Eq. 2.1. The only difference is the dimension of the state vectors and the matrix U. An often-used example for a two-qubit gate is the so called controlled-not (CNOT) gate whose matrix representation is [11]

$$U = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix} \tag{2.9}$$

in the standard two-qubit basis  $\{|00\rangle, |01\rangle, |10\rangle, |11\rangle\}$ . This operation can transform two independent single qubit states into one entangled state. With the CNOT gate and a small number of single qubit gates all components for one universal gate set are given [26]. Similar to the definition of universal gates in classical logic (NAND or NOR), such a set is able to implement all functionality in a universal quantum computer.

#### 2.3 Quality measures for qubits and gates

One important quality measure of a qubit is the lifetime of its state. That is the time it takes for the information encoded in the qubit state to disappear. Depending on the qubit type and the information loss mechanism the coherence time  $T_2$  or  $T_2^*$  is given, or the relaxation time  $T_1$  [29]. The relaxation and coherence times describe time constants at which the information content of the original state is decaying until the information of the current state does not show a correlation to the information of the original state. The relaxation time is the average time an excited qubit state relaxes to its energetic ground state. The coherence time describes the time it takes until the angle of a qubit state has no relation to the original angle<sup>5</sup> In general the relation between these parameters is  $T_2 \le 2T_1$ . Thus, different measurements of coherence apply for different qubit implementations. In contrast to  $T_1$  and to  $T_2$ ,  $T_2^*$  describes the loss of information of an ensemble of spins, which is relevant for multi-spin qubits. More detailed explanations of the phenomena and the quality measures are for example given in [29, 30]. Depending on the implementation the lifetime of a qubit state can be between a few μs [31] and the order of a second [32]. The longer the lifetime of the qubit the less errors on shorter timescales happen and the longer possible operation sequences can be. That means with a longer coherence time more complex circuits with higher circuit depth can be realized.

#### 2.3.1 Gate operations

The quality of a qubit operation, and the underlying state transformation, is usually described with the average gate fidelity [33, 34]

$$F = \frac{1}{n^2} |\text{Tr}[U_{ideal}^T \ U]|^2. \tag{2.10}$$

Eq. 2.10 shows the calculation of the fidelity with the ideal transformation matrix  $U_{ideal}$ , the actual matrix U, and a normalization factor n. The value of F lies between zero and one with one as best possible fidelity. In practice the infidelity I=1-F is often given for convenience. Current research mostly reports single qubit infidelities between  $10^{-1}$  and

<sup>&</sup>lt;sup>5</sup>Note that here the angle described is the angle in the Bloch sphere which is subject to constant precession.

$10^{-2}$  [15], depending on the qubit implementation<sup>6</sup>. Possible sources of non-idealities for the operation are plenty and range from systematic control errors to noise sources in the qubit samples and the control signals.

Non-ideal gate operations with I>0 lead to computation errors at an error rate  $\eta^7$ , that have to be corrected by error correction algorithms. The relationship between the fidelity F and error rates  $\eta$  is not trivial as additional information about the source of non-idealities is necessary for an exact calculation [35]. However, with assumptions on the type and amount of noise the relationship can be simplified [35]. Thus, for an error rate threshold of  $\eta=1\%$  (surface code) an infidelity of a little below  $10^{-2}$  could suffice. This is then under the assumption that existing noise only has a simple dephasing effect on the qubit [2]. In reality more effects from the noise are expected, such that the required infidelity to reach so called fault tolerance would be lower. A lower infidelity is also advantageous, as the cost of error correction (additional devices, hardware and software) decreases substantially with increasing gate fidelity. In this work the infidelity benchmarks used to evaluate gate performance are set to  $10^{-2}$  and  $10^{-3}$ , with the knowledge that a better infidelity is highly desirable.

## 2.4 Qubit implementations and their scalability potential

There are many physical two-level systems which can be used as a qubit. Research on qubit implementations is therefore done in a variety of systems. Examples are nitrogen centers in diamond [3], cold [36] and neutral atoms [37], trapped ions [38], photons [39], topological insulators, superconducting circuits [40] and spins in quantum dots [41]. The implementations vary significantly in many properties such as qubit lifetimes, gate fidelities, the control and gate operation mechanisms, environment specifications, physical size, sample production technology and their readout procedures. All these properties impact the suitability of this qubit implementation in a universal quantum computer. Ultimately, the computer requires millions of qubits, so the scalability of the qubits is a deciding factor, as first indicated by [42].

The highest chances in scaling numbers up are seen for superconducting qubits and semiconductor spin qubits. They have the advantage that their production is done with lithography techniques similar to the well-established processes in very large-scale integration (VLSI) electronics and the physical qubit size is comparably small. In addition,

<sup>&</sup>lt;sup>6</sup>Qubits based on ion traps are the most advanced, but as they are not considered scalable to high numbers they are not the focus of the present discussion.

<sup>&</sup>lt;sup>7</sup>A detailed introduction to errors in quantum computations, their correction and the terms associated is not in the scope of this work, but can be found in [25].

the control through electro-magnetic signals is possible. In Tab. 2.1 different potentially scalable qubit topologies and their properties are given.

For superconducting qubits, which are the most mature solid-state qubits, a maximum of 72 gubits on one chip has been announced [43] and 53 have been shown in operation [5]. In [5] the authors even claim that with their quantum processor they have shown superiority over a classical computer. The best infidelity reported to date for single qubit gates is  $10^{-3}$  and below  $6 \cdot 10^{-3}$  for two qubit gates [40]. These numbers all refer to todays most established superconducting qubit topology, the so-called transmon qubit. Like all superconducting qubits it is based on a resonant circuit. The circuits are cooled down to cryogenic temperatures and use quantum mechanical non-linear circuit elements to create the desired two-level qubit behaviour. The control of the qubits is done with quadrature amplitude modulation (OAM) microwave signals at a carrier frequency corresponding to the circuits' resonant frequency. While the superconducting qubits mainly can be produced with standard lithography techniques, their footprint slightly below 1 mm<sup>2</sup> is very large compared to the feature size of state-of-the-art VLSI processes. The scalability potential of the superconducting qubits is limited through the size of the footprint, as millions of qubits would already occupy an area of roughly 1 m<sup>2</sup>, which would have to be cooled. The control and readout of the superconducting qubits also opens issues regarding frequency multiplexing and crosstalk as the variability of the qubit resonance frequency is limited.

Semiconductor spin qubits mostly use quantum dots to locally confine electrons and use the spin to encode qubits. For the quantum dot fabrication different heterostructure material combinations as silicon-germanium (SiGe) and gallium-arsenide (GaAs) are often used, but Si-MOS devices exist as well [44]. A chip with 26 SiGe qubits has been announced in [45], but no measurements have been published yet. Most research groups work with a maximum of two qubits. The best achieved single qubit infidelity is  $10^{-3}$ [46] and a best two qubit infidelity of  $2 \cdot 10^{-2}$  [47] has been reached. However, these numbers were not achieved in the same experiment. SiGe qubits use the spin of a single electron and have a very small footprint of around 0.02 µm<sup>2</sup> (without electrode fanout and ohmic contacts to the electron reservoir) and the potential advantage of near zero nuclear spin. Nuclear spin is a material property that creates a small, local magnetic field which fluctuates over time and thus interferes with qubit operation. In SiGe qubits nuclear spin free isotopes like <sup>28</sup>Si can be used to avoid this noise source. This leads to very long coherence times on the order of 1 s [48, 49], while the operations can be as short as 100 ns [50] for single- and two-qubit gates. For operation the SiGe qubit requires several DC signals, a permanent magnetic field and microwave signals for a resulting effective magnetic AC field. Again, the microwave signals could potentially limit the scalability due to e.g. crosstalk.

GaAs qubits have already been studied extensively but have the disadvantage of unavoidable decoherence due to nuclear spin. For this reason GaAs qubits either use a

combination of spin and charge or the spin of several electrons to encode one qubit which mitigates the issue [41]. The most promising implementation of this is the so-called S-T<sub>0</sub> qubit using the spin of two electrons. The maximum number of qubits realized this way is only two, but the best infidelities experimentally achieved were  $5 \cdot 10^{-3}$  [51] for single qubit gates, not much worse than in SiGe. For two qubit gates only an infidelity of  $10^{-1}$  [52] has been experimentally shown, but theoretical results predict infidelities down to  $10^{-3}$  [53]. The duration of single and two qubit gates is several tens of ns with an achieved coherence of 0.87ms [54]. One deciding advantage of GaAs S-T<sub>0</sub> qubit is that only control at lower frequencies around a few hundred MHz is needed next to a few DC signals and a constant magnetic field. This simplifies the electrical generation of the signals compared to SiGe and transmon qubits and reduces the severity of crosstalk.

| Qubit | Lifetime | Gate duration (ns) |         | Infidelity       |                  | #  | Footprint | Control  |

|-------|----------|--------------------|---------|------------------|------------------|----|-----------|----------|

|       | ms       | 1 Qubit            | 2 Qubit | 1 Qubit          | 2 Qubit          |    | $\mu m^2$ |          |

| GaAs  | 0.87     | 40                 | 40      | $5\cdot 10^{-3}$ | $10^{-1(-3)}$    | 2  | 0.1       | VHF      |

| SiGe  | 1000     | 100                | 100     | $10^{-3}$        | $2\cdot 10^{-2}$ | 26 | 0.02      | SHF, VHF |

| T.mon | 0.01     | 20                 | 30      | $10^{-3}$        | $6\cdot 10^{-3}$ | 52 | $10^{6}$  | SHF      |

Table 2.1: Summary of the most promising scalable qubit candidates and their best achieved properties

As a comparison, the not highly scalable trapped ion qubits have single and two qubit error rates are below  $10^{-4}$  and  $10^{-3}$  with a coherence time of more than 1 s [38]. QEC has been demonstrated with these qubits as well but going from the current 1D lines of ions to 2D arrangements is a challenge. On top of that the control through lasers is not trivial for large scales of qubits. For such qubits with a high quality, other timelier use cases than a quantum computer are possible. Examples are quantum sensing, quantum networks and their quantum repeaters, and proof of principles in the current noisy intermediate-scale quantum (NISQ) [55] technology stage.

This thesis focuses on GaAs qubits as a reference as one of the promising candidates for scalable qubits. Especially the fact that only VHF control instead of microwave signals is needed for this topology makes it interesting to explore the scalability of control electronics. The methods used in this work, and by this the general results, can be transfered to other qubit technologies.

#### 2.4.1 The GaAs S-T<sub>0</sub> qubit

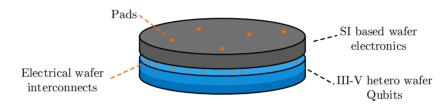

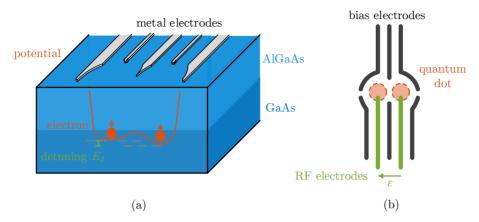

The basis of a GaAs qubit is a heterostructure made of aluminum-gallium-arsenide (AlGaAs) and GaAs as shown in Fig. 2.3. The shape of the conduction band in this

Figure 2.3: The GaAs qubit: (a) heterostructure cross-section with electrochemical potential distribution, (b) principle electrode layout of one double dot (radio frequency (RF))

heterostructure enables a two-dimensional electron gas (2DEG) of free electrons at the interface of the two materials. Electrodes on the top of the materials can locally deplete the 2DEG when a negative voltage is applied to them. With the correctly tuned voltage configuration two potential wells are created (Fig. 2.3), in which single electrons can be confined to a precisely defined location due to quantum mechanical principles. The wells are also called quantum dots. Thus, two wells together are named a double quantum dot or just a double dot.

In a GaAs qubit two electrons are confined in the double dot and their spin state is used to encode the logical basis states  $|0\rangle$  and  $|1\rangle$ . Next to different spin states, different charge configurations are employed e.g. for readout and initialization of the qubit. The different configurations of spin and charge can be distinguished by their discrete energy levels. In the case of the charge possible configurations are the occupancy of a dot with n electrons, with  $n \in \{0, 1, 2\}$ . The notation is  $(n_l, n_r)$  for the charge configuration of the double dot (left,right). In case of the spin the determining characteristic is the spin quantum number s. The spin quantum number is quantized and for s=0 a spin state is called a singlet (S) state. With s=1 the spin state is characterized as a triplet (T) state.

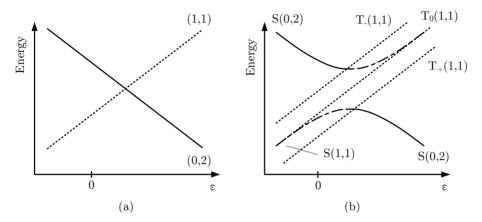

Figure 2.4b depicts the energy of all possible configurations dependent on the detuning voltage  $\epsilon$  (Fig. 2.3), which controls the energy difference between the dots through the detuning energy  $E_J$ . The basis of this complete energy diagram is the reduced energy diagram with only the relevant charge configurations, which is shown in Fig. 2.4a. Through energy level splitting due to electron spin (S-T splitting), bending of the levels because of possible inter-dot tunneling, and level splitting due to the Zeeman effect

(T splitting into  $T_-$ ,  $T_0$ , $T_+$ )<sup>8</sup>, the energy levels shown in Fig. 2.4b result. More detailed derivations can for example be found in [56].

Figure 2.4: GaAs double dot energy diagrams: (a) energy levels only due to charge configuration, (b) added spin and tunneling effects (adapted from [57])

Of all these states included in the full energy diagram, only the subset of S(1,1) and  $T_0(1,1)$  is used to encode the logical states  $|0\rangle$  and  $|1\rangle$ . That means during qubit operation there is always one electron in each dot. It follows also that the qubit can potentially have other states than the ones in the logical subspace. These are called leakage states. The loss of information towards leakage states, also called leakage rate, cannot be corrected by conventional QEC algorithms, but high-fidelity qubit operation is still possible [2]. States such as S(0,2) are used during readout and initialization. For example, readout principles are based on the fact that either a (0,2) charge configuration can be distinguished from a (1,1) one, or that the singlet and triplet spin configurations behave differently (e.g. Pauli exclusion principle).

The formal description of the energy states of a quantum mechanical system is typically done with the so called Hamiltonian H. The Hamiltonian for the logical subspace of a GaAs qubit, with the help of the Pauli matrices from Eq. 2.7, is often given in the form of [2, 56]:

$$H = \frac{\hbar\omega_{J}(\epsilon)}{2}\sigma_{z} + \frac{\hbar\Delta\omega_{z}}{2}\sigma_{x} = \frac{\hbar}{2}\begin{pmatrix}\omega_{J}(\epsilon) & \Delta\omega_{z}\\ \Delta\omega_{z} & -\omega_{J}(\epsilon)\end{pmatrix},\tag{2.11}$$

with  $\hbar$  being the reduced Planck constant. Eq. 2.11 uses the basis { $|S\rangle$ ,  $|T_0\rangle$ }. This computational basis can also be expressed in terms of spin orientations of the electrons

<sup>&</sup>lt;sup>8</sup>The Zeeman effect here is due to an applied constant magnetic field  $B_{ext}$ .

in the dot, with ↑ as spin up and ↓ denoting spin down

$$|S\rangle = |0\rangle = \frac{|\uparrow\downarrow\rangle - |\downarrow\uparrow\rangle}{\sqrt{2}},$$

(2.12)

$$|T_0\rangle = |1\rangle = \frac{|\uparrow\downarrow\rangle + |\downarrow\uparrow\rangle}{\sqrt{2}}.$$

(2.13)

The Hamiltonian in general describes energy states and with the Planck-Einstein relation  $E=hf=\hbar\omega$  ([58], p.1181) Eq. 2.11 can also be written in energy terms directly:

$$H = \frac{1}{2} \begin{pmatrix} E_J & \Delta E_{z,DNP} \\ \Delta E_{z,DNP} & -E_J \end{pmatrix}. \tag{2.14}$$

$E_J$  is the detuning energy which is equal to the energy difference of the dots and is connected to the so-called exchange interaction mechanism. The corresponding angular frequency  $\omega_I$  is given by [59, 60]

$$\omega_I(\epsilon(t)) \approx \omega_s \exp(\epsilon(t)/\epsilon_0).$$

(2.15)

Here,  $\epsilon(t)$  is a voltage defined as the potential difference between the right and the left dot and is applied through the two RF electrodes (Fig. 2.3). In contrast to convention in this work  $\epsilon_0$  does not denote the vacuum permittivity but is a fit constant. In addition, also  $\omega_s$  is a fit constant and thus the only parameter to actively change the state of the qubit is  $\epsilon(t)$ .

The other term in Eq. 2.14,  $\Delta E_z$ , is the result of the Zeeman effect. The Zeeman effect describes the shift of an electron energy level due to a magnetic field. In general  $E_z$  is given through ([61], p.150)

$$E_z = g\mu_B B, (2.16)$$

with the g factor (g=-0.44 in GaAs [32]), the Bohr magneton  $\mu_B$  and the magnetic field B. Of interest here is a magnetic field difference between the dots  $\Delta B_z$ . It is a result of the dynamic polarization of the nuclear spin of the host material leading to an angular frequency of  $\Delta \omega_z = \frac{g\mu_B}{\hbar} \Delta B_z$ . The procedure, which is also shortened to DNP (dynamic nuclear polarization), is for example described in [41]. The nuclear spin of the host material cannot be erased, so instead of trying to keep it as small as possible it is used here as a second axis for evolving the qubit state.

For the correct determination of the state of a GaAs qubit the absolute energy levels of in H are irrelevant. Thus, in this work the Hamiltonian  $\tilde{H}$  is used with

$$\tilde{H} = H \cdot \frac{1}{\hbar} = \frac{1}{2} \begin{pmatrix} \omega_J(\epsilon) & \Delta \omega_z \\ \Delta \omega_z & -\omega_J(\epsilon) \end{pmatrix}. \tag{2.17}$$

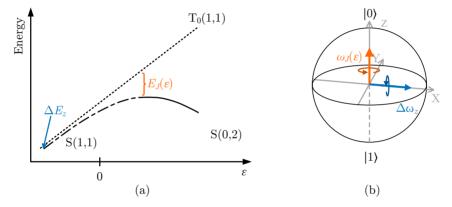

Figure 2.5 visualizes of influence of the two summands and thus the complete Hamiltonian on the qubit state while referring to the energy diagram. The exchange interaction is a measure of the amount of separation between  $|0\rangle$  and  $|1\rangle$ , as seen on the energy diagram of the logical subspace in Fig. 2.5a. The smaller  $E_J$ , the larger the superposition. Some residual separation of S(1,1) and the  $T_0(1,1)$  state remains at  $\epsilon \ll 0$  due to the polarized nuclear spin and the resulting  $\Delta E_z$ . In Fig. 2.5 the basis rotation axes in the Bloch sphere, as described in Eq. 2.11 are shown. As denoted by  $\sigma_z$  the exchange interaction rotates the qubit state around the z-axis. The strength and as a result the speed of the rotation is given through  $\epsilon$ . A state rotation due to the constant magnetic field difference happens around the x-axis and cannot be turned off. Only the relative strength of  $E_J$  governs the effect that  $\Delta E_z$  has.

Figure 2.5: (a) Energy diagram of the logical subspace with state changing parameters and (b) visualization of state changing rotations on the Bloch sphere

The relation between  $E_J$  and  $\epsilon$  in Eq. 2.15 is an approximation determined through device measurements and an exponential fit. The constant values used in this work are  $\omega_s = 2\pi \cdot 160$  MHz and  $\epsilon_0 = 0.27241$  mV. They were obtained from fit data from [59, 60], but differ depending on the sample geometry, the specific experiment settings and the electrode potentials that form the double dot.

To get from the Hamiltonian  $\tilde{H}$  description to the calculation of the unitary matrix U the following relation can be used for a piecewise constant Hamiltonian<sup>9</sup>:

$$U(t_M) = \prod_{k=1}^{M} \exp\left(-i \begin{pmatrix} \omega_J(\epsilon_k) & \Delta \omega_z \\ \Delta \omega_z & -\omega_J(\epsilon_k) \end{pmatrix} \Delta t_k \right) = \prod_{k=1}^{M} dU_k. \tag{2.18}$$

<sup>&</sup>lt;sup>9</sup>This is derived from the Schrödinger equation  $i\hbar d/dt |\Psi(t)\rangle = H|\Psi(t)\rangle$ .

Here, the time  $t_M$  is given by  $t_M = \sum_{k=1}^M \Delta t_k$  with  $\Delta t_k = t_k - t_{k-1}$  and  $\epsilon_k$  is the constant detuning during each timestep  $\Delta t_k$ .

# 2.5 State of the Art (scalable) qubit control

As seen exemplary in Fig. 1.1, most of todays laboratory setups for qubit research are done with standard signal sources and measurement equipment at room temperature. For the control especially arbitrary waveform generators (AWGs), RF sources and bias sources are needed. For the S-T $_0$  qubit focused on here, the microwave source is not necessary. In Chap. 1 is already mentioned that for a large qubit number this type of room temperature setup is not realistic, even if it is perfectly suited to the variable few qubit experiments today. Depending on the qubit type different approaches are investigated to control numerous qubits.

For superconducting qubits, where extensive microwave signal generation is necessary, the focus is mainly on making the room temperature equipment more efficient and affordable, as described in the supplementary material of [5] and in [62, 63].

For semiconductor qubits the approach is to put as much electronics as possible inside the fridge. Thus, the research started with implementing small, function specific circuits for cryogenic operation [64–68] and connectors [69]. Additional research on characterizing current CMOS technologies is also a part e.g. in [70–72]. In general, the newer technology generations show similar characteristics at cryogenic temperatures compared to room temperature for many devices. Issues such as hysteresis behaviour for transistors, which existed in older technologies, does not seem to be an issue any longer. The cited works are a good basis for future use of CMOS technologies at cryogenic temperatures, however the research is not yet at a point where the results can be easily integrated in the standard circuit design flow.

In the beginning of the research on placing the electronics inside the fridge, the location for the bulk of the electronics was the same. Only limited switching functionality was placed next to the qubits, while the other components were to be located at a stage with a higher temperature of 4 K [22, 73]. Several works describe the electronics for the case of SiGe qubits [74–76]. Especially valuable from this works is the result, that a standard field-programmable gate array (FPGA) is operational at cryogenic temperatures.

Current works still place the main electronics for the SiGe qubits at that temperature [77], while the concept of this work (also included in [78]) locates the electronics at the lowest temperature stage. Also preliminary results published in [79] use that concept. The higher temperature has the advantage, that more cooling power is available. This is especially important for SiGe qubits, as the microwave circuits necessary are expected to dissipate more heat. For example only the analog power of a current qubit controller

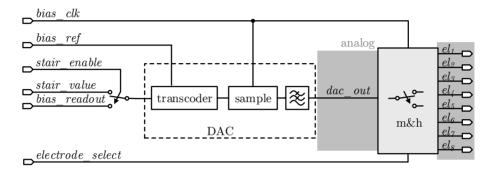

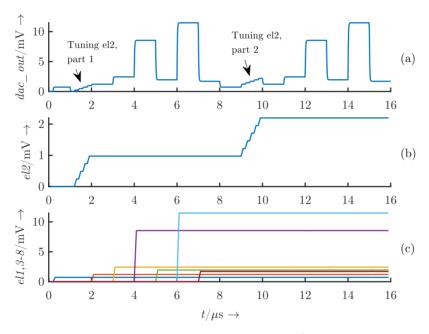

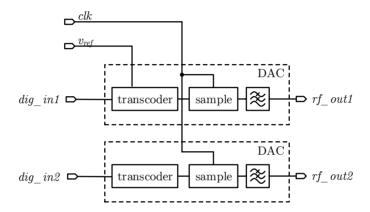

[80] consumes 1.7 mW per qubit and an oscillator for the same system draws 4.3 mW [81]. A cooling power of only a few mW at the lowest temperature stage makes it very difficult to place these kinds of circuits in the vicinity of the qubits without a negative impact on the temperature in the fridge and thus impeding qubit operation.